## eCPRI Intel<sup>®</sup> FPGA IP User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **22.4**

IP Version: 2.0.2

## intel

## Contents

| 1. | Introduction4                                             | ŧ |

|----|-----------------------------------------------------------|---|

|    | 1.1. Supported Features                                   | 1 |

|    | 1.2. Device Family Support                                | 5 |

|    | 1.3. eCPRI Intel FPGA IP Device Speed Grade Support       | 5 |

|    | 1.4. Resource Utilization                                 |   |

|    | 1.5. Intel FPGA IP Core Verification                      | 7 |

|    | 1.6. Release Information                                  | 7 |

| 2. | Getting Started                                           | 3 |

|    | 2.1. Installing and Licensing                             | 3 |

|    | 2.2. Specifying the IP Core Parameters and Options        |   |

|    | 2.2.1. Reference and System PLL Clock for your IP Design  | ) |

|    | 2.3. Generated File Structure11                           | L |

|    | 2.4. Simulating the IP Core13                             |   |

|    | 2.5. Compiling the Full Design and Programming the FPGA14 | 1 |

| 3. | IP Parameters15                                           | 5 |

| 4. | Functional Description                                    | ) |

| •• | 4.1. Interfaces                                           |   |

|    | 4.2. High Level Data Path Flow                            |   |

|    | 4.2.1. Transmit TX Path                                   |   |

|    | 4.2.2. Receive RX Path                                    |   |

|    | 4.2.3. Supported Ethernet Variants                        |   |

|    | 4.3. Operation of the eCPRI IP Blocks                     |   |

|    | 4.3.1. Packet Classifier24                                |   |

|    | 4.3.2. Ethernet Header Insertion/Removal25                |   |

|    | 4.3.3. Concatenation/De-concatenation27                   |   |

|    | 4.3.4. Header Mapper/De-Mapper 29                         | Э |

|    | 4.3.5. eCPRI IWF Type 0                                   | Э |

|    | 4.3.6. eCPRI Message 5 Packet Parser29                    |   |

|    | 4.3.7. Packet Queue                                       | L |

|    | 4.3.8. eCPRI Message Type31                               |   |

|    | 4.3.9. Error Handling                                     |   |

|    | 4.3.10. RX Throttling                                     | ) |

| 5. | Interface Overview                                        | ) |

|    | 5.1. Clock Signals40                                      | ) |

|    | 5.2. Power, Reset, and Firewalls Signals 42               |   |

|    | 5.2.1. Reset Control and Initialization Flows43           |   |

|    | 5.3. TX Time of Day Interface                             |   |

|    | 5.4. RX Time of Day Interface44                           |   |

|    | 5.5. Interrupt                                            |   |

|    | 5.6. Configuration Avalon Memory-Mapped Interface4        |   |

|    | 5.7. Ethernet MAC Source Interface                        |   |

|    | 5.7.1. E-tile Hard IP for Ethernet 1588 PTP Signals       |   |

|    | 5.7.2. 25G Ethernet MAC 1588 PTP Signals48                |   |

|    | 5.7.3. 10G Ethernet MAC 1588 PTP Signals49                | J |

6. 7.

8.

# intel

| 5.8. Ethernet MAC Sink Interface                             | 52 |

|--------------------------------------------------------------|----|

| 5.9. External ST Source Interface                            | 52 |

| 5.10. External ST Sink Interface                             | 53 |

| 5.11. eCPRI IP Source Interface                              | 54 |

| 5.12. eCPRI IP Sink Interface                                |    |

| 5.13. Miscellaneous Interface Signals                        | 58 |

| 5.14. IWF Type 0 eCPRI Interface                             | 58 |

| 5.14.1. IWF Source Interface                                 | 59 |

| 5.14.2. IWF Sink Interface                                   | 62 |

| 5.15. IWF Type 0 CPRI MAC Interface                          | 63 |

| 5.15.1. CPRI 32-bit IQ Data TX Interface                     | 63 |

| 5.15.2. CPRI 64-bit IQ Data TX Interface                     |    |

| 5.15.3. CPRI 32-bit Ctrl_AxC TX Interface                    |    |

| 5.15.4. CPRI 64-bit Ctrl_AxC TX Interface                    |    |

| 5.15.5. CPRI 32-bit Vendor Specific TX Interface             |    |

| 5.15.6. CPRI 64-bit Vendor Specific TX Interface             |    |

| 5.15.7. CPRI 32-bit Real-time Vendor Specific TX Interface   |    |

| 5.15.8. CPRI 64-bit Real-time Vendor Specific TX Interface   |    |

| 5.15.9. CPRI Gigabit Media Independent Interface (GMII)      |    |

| 5.15.10. CPRI IP L1 Control and Status Interface             | 68 |

| IP Registers                                                 |    |

| eCPRI Intel FPGA IP User Guide Archives                      | 72 |

| Document Revision History for eCPRI Intel FPGA IP User Guide |    |

intel

## **1. Introduction**

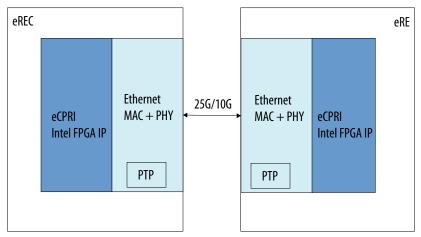

The enhanced Common Public Radio Interface (eCPRI) Intel<sup>®</sup> FPGA IP core implements the *eCPRI specification version 2.0*. The eCPRI IP is a front-haul interface protocol for radio base station aimed at connecting the eCPRI Radio Equipment Control (eREC) and the eCPRI Radio Equipment (eRE) via front-haul transport network.

## Figure 1. Typical eCPRI Application on Intel FPGA Devices

## **Related Information**

- eCPRI Specification V2.0

- eCPRI Intel FPGA IP Design Example User Guide

## **1.1. Supported Features**

The eCPRI Intel FPGA IP core offers the following features:

- Compliant with the *eCPRI Specification V2.0 (2018-06-25)* available on the CPRI Industry Initiative (CII) website.

- Supports eCPRI radio equipment controller (eREC) and eCPRI radio equipment (eRE) module configurations.

- Supports Ethernet headers in a variety of formats, including VLAN tag, source/ destination MAC address, IPv4, UDP extraction and encapsulation.

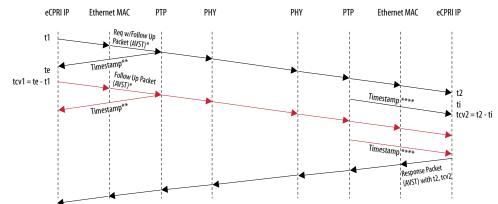

- Supports eCPRI one-way delay measurement based on IEEE Standard 1588 Precision Time Protocol (1588 PTP) hardware timestamp. Full hardware support, and required 1588 PTP software stack.

- Supports 25 Gbps and 10 Gbps Ethernet ports.

- Supports pairing of eCPRI Intel FPGA IP with O-RAN Intel FPGA IP.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

- Supports interworking function (IWF) type 0 between eCPRI node and one CPRI node.

- Capable of streaming Ethernet frame size up to 9,000 bytes as defined by Ethernet jumbo frames standard.

- Packet classifier responsible to classify eCPRI packet and send packets to eCPRI IP. All other packets are redirected to external port for user processing.

- Programmable packet queue (maximum 16 entries) to hold incoming packets when eCPRI packets transmission in progress.

- Arbitration between eCPRI packet and external incoming Ethernet frames, e.g., Control & Management (C&M) and synchronization packets.

- Offers mapping logic between eCPRI message physical channel ID to VLAN/MAC address CSR.

- Supports single distributed unit (DU) and up to eight radio unit (RU) configurations using source/destination MAC address CSR.

- Support all eCPRI message types compliant to eCPRI specification v2.0

- Input/output ports compliant with Avalon<sup>®</sup> streaming interface .

### Table 1. eCPRI Intel FPGA IP Feature Matrix

| Device Support                | Data Rate |  |

|-------------------------------|-----------|--|

| Intel Agilex™                 | 25G       |  |

|                               | 10G       |  |

| Intel Stratix <sup>®</sup> 10 | 25G       |  |

|                               | 10G       |  |

| Intel Arria <sup>®</sup> 10   | 10G       |  |

#### **Related Information**

- CPRI Industry Initiative website

- IEEE website

- Supported Ethernet Variants on page 23 Refer to this section for information on supported Ethernet variants from Intel.

- O-RAN Intel FPGA IP User Guide

## **1.2. Device Family Support**

#### Table 2. Intel FPGA IP Core Device Support Levels

| Device Support<br>Level | Definition                                                                                                                                                                                                                                                                                                          |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance                 | The IP core is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing |

|                         | continued                                                                                                                                                                                                                                                                                                           |

| Device Support<br>Level | Definition                                                                                                                                                                                                                                                                  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (datapath width, burst depth, I/O standards tradeoffs). |  |  |

| Preliminary             | The IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.                       |  |  |

| Final                   | The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                                              |  |  |

## Table 3. eCPRI Intel FPGA IP Core Device Family Support

Shows the level of support offered by the eCPRI Intel FPGA IP for each Intel FPGA device family.

| Device Family                     | Support    |  |

|-----------------------------------|------------|--|

| Intel Agilex (F-tile devices)     | Advance    |  |

| Intel Agilex (E-tile devices)     | Advance    |  |

| Intel Stratix 10 (E-tile devices) | Final      |  |

| Intel Stratix 10 (H-tile devices) | Final      |  |

| Intel Arria 10                    | Final      |  |

| Other device families             | No support |  |

## **1.3. eCPRI Intel FPGA IP Device Speed Grade Support**

The eCPRI Intel FPGA IP core supports the following speed grades.

## Table 4.Device Speed Grade Support

| Device                       | Transceiver Speed Grade | Core Speed Grade |  |

|------------------------------|-------------------------|------------------|--|

| Intel Agilex with F-tile     | -3, -2 and -1           | -3, -2 and -1    |  |

| Intel Agilex with E-tile     | -2 and -1               | -2 and -1        |  |

| Intel Stratix 10 with E-tile | -2 and -1               | -2 and -1        |  |

| Intel Stratix 10 with H-tile | -2 and -1               | -2 and -1        |  |

| Intel Arria 10               | -2 and -1               | -2 and -1        |  |

## **1.4. Resource Utilization**

The resources for the eCPRI Intel FPGA IP core were obtained form the Intel Quartus<sup>®</sup> Prime Pro Edition software version 22.3 with advance mapping enabled:

## Table 5.Resource Utilization

| Device       | Mode          | ALMs | Dedicated Logic<br>Registers | Memory 20K |

|--------------|---------------|------|------------------------------|------------|

| Intel Agilex | Non-streaming | 9576 | 21913                        | 53         |

|              | Streaming     | 9335 | 22127                        | 52         |

|              | O-RAN Fixed   | 7538 | 17383                        | 43         |

|              |               |      |                              | continued  |

# intel

| Device           | Device Mode          |       | Dedicated Logic<br>Registers | Memory 20K |

|------------------|----------------------|-------|------------------------------|------------|

|                  | O-RAN L2COS          | 11978 | 20305                        | 44         |

|                  | IWF (with streaming) | 11250 | 24365                        | 72         |

|                  | Non-streaming        | 9535  | 22641                        | 53         |

|                  | Streaming            | 9429  | 22542                        | 52         |

| Intel Stratix 10 | O-RAN Fixed          | 7650  | 17273                        | 43         |

|                  | O-RAN L2COS          | 11886 | 22746                        | 44         |

|                  | IWF (with streaming) | 11176 | 23940                        | 74         |

|                  | Non-streaming        | 8876  | 20827                        | 53         |

|                  | Streaming            | 8653  | 20251                        | 52         |

| Intel Arria 10   | O-RAN Fixed          | 6729  | 15779                        | 43         |

|                  | O-RAN L2COS          | 10844 | 18842                        | 44         |

|                  | IWF (with streaming) | 14026 | 25126                        | 69         |

## **1.5. Intel FPGA IP Core Verification**

To ensure functional correctness of the eCPRI Intel FPGA IP core, Intel performs validation through both simulation and hardware testing. Before releasing a version of the eCPRI Intel FPGA IP core, Intel runs regression tests in the associated version of the Intel Quartus Prime software.

## **1.6.** Release Information

The Intel FPGA IP version (X.Y.Z) number can change with each Intel Quartus Prime software version. A change in:

- X indicates a major revision of the IP. If you update the Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

## Table 6. eCPRI Intel FPGA IP Core Release Information

| Item                        | Description |

|-----------------------------|-------------|

| IP Version                  | 2.0.2       |

| Intel Quartus Prime Version | 22.4        |

| Release Date                | 2023.02.24  |

| Ordering Code               | IP-eCPRI    |

## **Related Information**

## eCPRI Intel FPGA IP Release Notes

The IP Release Notes describes changes to the IP in a particular release.

## 2. Getting Started

The following sections explain how to install, parameterize, simulate, and initialize the eCPRI Intel FPGA IP IP core:

## 2.1. Installing and Licensing

The eCPRI Intel FPGA IP core is an extended FPGA IP core which is not included with the Intel Quartus Prime release. This section provides a general overview of the Intel extended FPGA IP core installation process to help you quickly get started with any Intel extended FPGA IP core.

The Intel extended FPGA IP cores are available from the Intel Self-Service Licensing Center (SSLC). Refer to Related Information below for the correct link for this IP core.

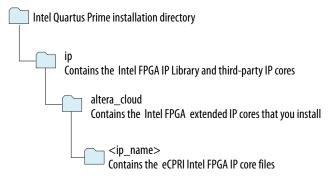

#### Figure 2. eCPRI Intel FPGA IP Core Installation Directory Structure

Directory structure after you install the eCPRI IP core.

## Table 7. Intel FPGA IPCore Installation Locations

| Location                                                                                          | Software                        | Platform |

|---------------------------------------------------------------------------------------------------|---------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\<version>\quartus\ip \altera_cloud</version></drive></pre>            | Intel Quartus Prime Pro Edition | Windows* |

| <pre><home directory="">:/intelFPGA_pro/<version>/ quartus/ip/altera_cloud</version></home></pre> | Intel Quartus Prime Pro Edition | Linux*   |

## **Related Information**

#### Self-Service Licensing Center (SSLC)

After you purchase the eCPRI Intel FPGA IP core, the IP core is available for download from the SSLC page in your My Intel account. You must create a My Intel account if you do not have one already, and log in to access the SSLC. On the SSLC page, click Run for this IP core. The SSLC provides an installation dialog box to guide your installation of the IP core.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

## 2.2. Specifying the IP Core Parameters and Options

The IP parameter editor allows you to quickly configure your custom IP variation. Use the following steps to specify IP core options and parameters in the Intel Quartus Prime Pro Edition software.

**Prerequisite**: Once you receive the eCPRI web-core IP, save the web-core installer to the local area. Run the installer with Windows/Linux. When prompt, install to the same location as Intel Quartus Prime folder. The eCPRI Intel FPGA IP now appears in the IP Catalog.

## Figure 3. eCPRI IP Parameter Editor

| Elle Edit System Generate View Tools Help   |               |                                    |                                          |                            |

|---------------------------------------------|---------------|------------------------------------|------------------------------------------|----------------------------|

| Marameters 🕺                                |               | - ď 🗆                              | Details 🛛 🐸 Block Symbol 🔅               | - 6 0                      |

| System: test_203 Path: ecpri_0              |               |                                    | Show signals                             | -                          |

| eCPRI Intel FPGA IP                         |               | Details<br>Generate Example Design |                                          | ecpri_0 =                  |

| * Configuration                             |               |                                    | mac clk tx                               | c_clk_tx mac_source        |

| General Example Design                      |               |                                    |                                          | clk valid                  |

| Transceiver tile to be used:                | E             | -                                  | mac_clk_rx                               | startofpacket              |

| Data Width:                                 | 64            | -<br>-                             |                                          | clk_tx empty               |

| Protocol Revision:                          | 1             |                                    | <u>slk_tx</u>                            | cik error                  |

| Delay Measurement:                          | one step      |                                    | <u>c</u> lk_rx                           | clk_n ready<br>avst_source |

| RX external data path FIFO depth:           | 64            |                                    |                                          | clk_csr valid              |

| Queue Miscellaneous FIFO Depth:             | 64            |                                    | <u>clk_csr</u>                           | clk startofpacket          |

| Queue PTP FIFO Depth:                       | 32            |                                    | ext_sink_clk                             | ank_cik endofpacket        |

| Advance Mapping Mode                        |               |                                    |                                          | st_tx_n error              |

| Pair With ORAN                              |               |                                    | rst_tx_n                                 | reset ext_source           |

| Streaming                                   |               |                                    | _rst_rx_n                                | st_rx_n valid data         |

| Interworking Function (IWF) Support         |               |                                    | < II                                     | reset ctastafaackat F      |

| Interworking Function (IWF) Type:           | 0             |                                    | of Presets 🕺                             | - 6 0                      |

| Interworking Function (IWF) Number of CPRI: | 1             |                                    |                                          |                            |

| CPRI Line Bit Rate (Gbit/s):                | 24.33024      |                                    | Presets for ecpri_0                      |                            |

| Remote Memory Access Timer Bit-width:       | 12            |                                    |                                          | ×                          |

| One-way Delay Measurement Timer Bit-Width:  | 16            |                                    |                                          |                            |

| Remote Reset Timer Bit-width:               | 12            |                                    | Project<br>Click New to create a preset. |                            |

| Default MAC Source Address:                 | 0x00000000000 |                                    | Library                                  |                            |

| Default MAC Destination Address 0:          | 0x00000000000 |                                    | - No presets for eCPRI Intel FPG         | A IP 1.2.0                 |

| Default MAC Destination Address 1:          | 0x00000000000 |                                    |                                          |                            |

| Default MAC Destination Address 2:          | 0x00000000000 |                                    |                                          |                            |

| Default MAC Destination Address 3:          | 0x00000000000 |                                    |                                          |                            |

| Default MAC Destination Address 4:          | 0x00000000000 |                                    |                                          |                            |

| Default MAC Destination Address 5:          | 0x00000000000 |                                    |                                          |                            |

| Default MAC Destination Address 6:          | 0x00000000000 |                                    |                                          |                            |

| Default MAC Destination Address 7:          | 0x00000000000 | •                                  |                                          |                            |

| ä≣ System Messages 💠                        |               | - 5 0                              |                                          |                            |

| Type Path                                   |               |                                    |                                          |                            |

|                                             |               |                                    |                                          |                            |

| (No messages)                               |               |                                    | Apply Update Delet                       | le New                     |

|                                             |               |                                    |                                          |                            |

| 0 Errors, 0 Warnings                        |               |                                    |                                          | Generate HDL               |

- 1. If you do not already have an Intel Quartus Prime Pro Edition project in which to integrate your eCPRI IP core, you must create one.

- a. In the Intel Quartus Prime Pro Edition, click File ➤ New Project Wizard to create a new Quartus Prime project, or File ➤ Open Project to open an existing Quartus Prime project. The wizard prompts you to specify a device.

- b. Specify the device family that meets the speed grade requirements for the IP core.

- c. Click Finish.

- 2. In the IP Catalog, locate and select **eCPRI Intel FPGA IP**. The **New IP Variation** window appears.

- 3. Specify a top-level name for your new custom IP variation. The parameter editor saves the IP variation settings in a file named <*your\_ip*>.ip.

- 4. Click **OK**. The parameter editor appears.

- 5. Specify the parameters for your IP core variation. Refer to IP Parameters on page 15 for information about specific IP core parameters.

- 6. Optionally, to generate a simulation testbench or compilation and hardware design example, follow the instructions in the *Design Example User Guide*.

- 7. Click **Generate HDL**. The **Generation** dialog box appears.

- 8. Specify output file generation options, and then click **Generate**. The IP variation files generate according to your specifications.

- Click Finish. The parameter editor adds the top-level .ip file to the current project automatically. If you are prompted to manually add the .ip file to the project, click Project ➤ Add/Remove Files in Project to add the file.

- 10. After generating and instantiating your IP variation, make appropriate pin assignments to connect ports and set any appropriate per-instance RTL parameters.

## **Related Information**

eCPRI Intel FPGA Design Example User Guide

## 2.2.1. Reference and System PLL Clock for your IP Design

Each F-tile system must instantiate one F-Tile Reference and System PLL Clocks Intel FPGA IP. The F-Tile Reference and System PLL Clocks Intel FPGA IP performs three main functions:

- 1. Configure reference clock for FHT PMA:

- Enable the FHT common PLLs and select the reference clock source for FHT common PLL

- Specify the FHT reference clock source frequency

- 2. Configure reference clock for FGT PMA:

- Enable FGT reference clocks and specify the reference clock frequency

- Specify FGT CDR output

- 3. Configure system PLL:

- Enable system PLL and specify its mode

- Specify the reference clock source and frequency for system PLL

- *Note:* In your IP design, you must include an F-Tile Reference and System PLL Clocks Intel FPGA IP core to pass logic generation flow.

The F-Tile Reference and System PLL Clocks Intel FPGA IP must always connect to a protocol based Intel FPGA IP. The F-Tile Reference and System PLL Clocks Intel FPGA IP cannot be compiled or simulated as a standalone IP. For more information on parameters and port list for F-Tile Reference and System PLL Clocks Intel FPGA IP core, refer to the *F-tile Architecture and PMA/FEC Direct PHY IP User Guide*.

When you design multiple interfaces or protocol-based IP cores within a single F-tile, you must use only one instance of the F-Tile Reference and System PLL Clocks Intel FPGA IP core to configure:

- All required reference clocks for FGT PMA (up to 10) and FHT PMA (up to 2) to implement multiple interfaces within a single F-tile.

- All required FHT common PLLs (up to 2) to implement multiple interfaces within a single F-tile.

- All required System PLLs (up to 3) to implement multiple interfaces within a single F-tile.

- All required reference clocks for system PLLs (up to 8 shared with FGT PMA) to implement multiple interfaces within a single F-tile.

When you design multiple interfaces or protocol-based IP cores within a single F-tile, you can only use three System PLLs. For example, you can use one System PLL for PCIe and two for Ethernet and other protocols. However, there are other use cases where you can use all three for various interfaces within the Ethernet and PMA-Direct digital blocks. As there are only three System PLLs, multiple interfaces or protocol-based IP cores with different line rates may have to share a System PLL. While sharing a System PLL, the interface with the highest line rate determines the system PLL frequency, and the interfaces with the lower line rates must be overclocked. For more information, refer to the *F-tile Architecture and PMA/FEC Direct PHY IP User Guide*.

#### **Related Information**

F-tile Architecture and PMA/FEC Direct PHY IP User Guide

## 2.3. Generated File Structure

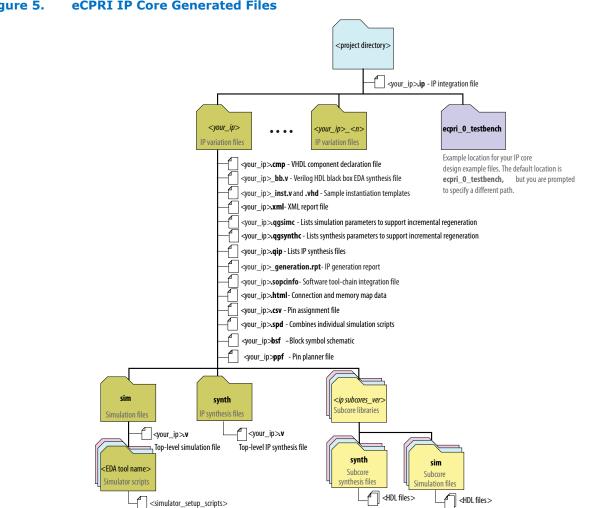

The Intel Quartus Prime Pro Edition software generates the following IP core output file structure.

#### Figure 4. eCPRI IP Core Generated Files

For more information about the file structure of the design example, refer to the *eCPRI Intel FPGA Design Example User Guide*.

# intel

#### Figure 5. **eCPRI IP Core Generated Files**

#### Table 8. **eCPRI IP Core Generated Files**

| File Name                                     | Description                                                                                                                                                                                                                                                                    |  |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <your_ip>.ip</your_ip>                        | The Platform Designer system or top-level IP variation file. < <i>your_ip</i> > is the name that you give your IP variation.                                                                                                                                                   |  |  |  |  |

| <your_ip>.cmp</your_ip>                       | The VHDL Component Declaration (. $cmp$ ) file is a text file that contains local generic and port definitions that you can use in VHDL design files.                                                                                                                          |  |  |  |  |

| <your_ip>.html</your_ip>                      | A report that contains connection information, a memory map showing the address of each slave with respect to each master to which it is connected, and parameter assignments.<br>IP or Platform Designer generation log file. A summary of the messages during IP generation. |  |  |  |  |

| <pre><your_ip>_generation.rpt</your_ip></pre> |                                                                                                                                                                                                                                                                                |  |  |  |  |

| <your_ip>.qgsimc</your_ip>                    | Lists simulation parameters to support incremental regeneration.<br>Lists synthesis parameters to support incremental regeneration.                                                                                                                                            |  |  |  |  |

| <your_ip>.qgsynthc</your_ip>                  |                                                                                                                                                                                                                                                                                |  |  |  |  |

| <your_ip>.qip</your_ip>                       | Contains all the required information about the IP component to integrate and compile the IP component in the Intel Quartus Prime software.                                                                                                                                    |  |  |  |  |

|                                               | continued                                                                                                                                                                                                                                                                      |  |  |  |  |

| File Name                                        | Description                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <your_ip>.sopcinfo</your_ip>                     | Describes the connections and IP component parameterizations in your<br>Platform Designer system. You can parse its contents to get requirements<br>when you develop software drivers for IP components.                                                                                                                                             |

|                                                  | Downstream tools such as the Nios <sup>®</sup> II tool chain use this file. The .sopcinfo file and the system.h file generated for the Nios II tool chain include address map information for each slave relative to each master that accesses the slave. Different masters may have a different address map to access a particular slave component. |

| <your_ip>.csv</your_ip>                          | Contains information about the upgrade status of the IP component.                                                                                                                                                                                                                                                                                   |

| <your_ip>.bsf</your_ip>                          | A Block Symbol File (.bsf) representation of the IP variation for use in Intel Quartus Prime Block Diagram Files (.bdf).                                                                                                                                                                                                                             |

| <your_ip>.spd</your_ip>                          | Required input file for ip-make-simscript to generate simulation scripts for supported simulators. The .spd file contains a list of files generated for simulation, along with information about memories that you can initialize.                                                                                                                   |

| <your_ip>.ppf</your_ip>                          | The Pin Planner File ( $_{\rm ppf}$ ) stores the port and node assignments for IP components created for use with the Pin Planner                                                                                                                                                                                                                    |

| <your_ip>_bb.v</your_ip>                         | You can use the Verilog black-box (_bb.v) file as an empty module declaration for use as a black box.                                                                                                                                                                                                                                                |

| <your_ip>_inst.v or _inst.vhd</your_ip>          | HDL example instantiation template. You can copy and paste the contents of this file into your HDL file to instantiate the IP variation.                                                                                                                                                                                                             |

| <your_ip>.v or <your_ip>.vhd</your_ip></your_ip> | HDL files that instantiate each submodule or child IP core for synthesis or simulation.                                                                                                                                                                                                                                                              |

| mentor/                                          | Contains a QuestaSim* script <pre>msim_setup.tcl</pre> to set up and run a simulation.                                                                                                                                                                                                                                                               |

| synopsys/vcs/<br>synopsys/vcsmx/                 | Contains a shell script vcs_setup.sh to set up and run a VCS* simulation.<br>Contains a shell script vcsmx_setup.sh and synopsys_ sim.setup file to<br>set up and run a VCS MX simulation.                                                                                                                                                           |

| aldec/                                           | Contains a shell script rivierapro_setup.sh to setup and run a Riviera-<br>PRO* simulation.                                                                                                                                                                                                                                                          |

| xcelium/                                         | Contains a shell script xcelium_setup.sh and other setup files to set up and run an Xcelium* simulation.                                                                                                                                                                                                                                             |

| submodules/                                      | Contains HDL files for the IP core submodules.                                                                                                                                                                                                                                                                                                       |

| <child cores="" ip="">/</child>                  | For each generated child IP core directory, Platform Designer generates synth/ andsim/ sub-directories.                                                                                                                                                                                                                                              |

## **Related Information**

eCPRI Intel FPGA Design Example User Guide

## 2.4. Simulating the IP Core

You can simulate your eCPRI IP variation using any of the vendor-specific IEEE encrypted functional simulation models which are available in the <instance\_name>/sim subdirectory of your project directory.

The eCPRI IP core supports the Synopsys\* VCS, Synopsys VCS MX, Siemens\* EDA QuestaSim, Aldec\* Riviera-PRO and Xcelium Parallel simulators. The eCPRI IP core generates a Verilog HDL and VHDL simulation model. The IP core parameter editor

offers you the option of generating a Verilog HDL or VHDL simulation model for the IP core. The IP core design example also supports Verilog HDL/VHDL simulation model or testbench.

For more information about functional simulation models for Intel FPGA IP cores, refer to the *Simulating Intel FPGA Designs chapter in Quartus Prime Pro Edition User Guide: Third-party Simulation*.

#### **Related Information**

- Simulating Intel FPGA Designs

- eCPRI Intel Stratix 10 FPGA Design Example User Guide

## 2.5. Compiling the Full Design and Programming the FPGA

You can use the **Start Compilation** command on the **Processing** menu in the Intel Quartus Prime software to compile your design. After successfully compiling your design, program the targeted Intel device with the Programmer and verify the design in hardware.

## **3. IP Parameters**

You customize the IP core by specifying parameters in the IP parameter editor.

Table 9.

Parameters: Configuration Tab

| Parameter                           | Supported Default Setting<br>Values |          | Description                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------------------------|-------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Transceiver Tile to be<br>used      | E<br>F<br>H                         | E        | <ul> <li>You can choose:</li> <li>H-tile or E-tile for your Intel Stratix 10 device</li> <li>E-tile or F-tile for your Intel Agilex device</li> <li>Note: This parameter is not present in the Intel Arria 10 IP variations.</li> </ul>                                         |  |  |  |

| Data Width                          | 64                                  | 64       | Primary data bus width.                                                                                                                                                                                                                                                         |  |  |  |

| Protocol Revision                   | 1                                   | 1        | Specifies eCPRI protocol revision used in eCPRI common header.<br>This option is grayed out in the current version of the Intel Quartus Prime software.                                                                                                                         |  |  |  |

| Delay Measurement                   | off<br>one_step<br>two_step         | one_step | Indicates option to support and the operation mode of<br>delay measurement for eCPRI message type 5 delay<br>measurement.<br>When set to <b>off</b> , the IP does not include the delay<br>measurement logic.                                                                   |  |  |  |

| RX external data path<br>FIFO depth | 64<br>128<br>256                    | 64       | Indicates the depth of the RX external data path FIFO. The actual depth is $\log_2$ of the FIFO depth.                                                                                                                                                                          |  |  |  |

| Queue Miscellaneous<br>FIFO depth   | 32<br>64<br>128<br>256              |          | Indicates the depth of the Queue miscellaneous FIFO. The actual depth is $\log_2$ of the FIFO depth.                                                                                                                                                                            |  |  |  |

| Queue PTP FIFO Depth                | 32<br>64<br>128<br>256              | 32       | Indicates the depth of the Queue PTP FIFO. The actual depth is $\log_2$ of the FIFO depth.                                                                                                                                                                                      |  |  |  |

| Advance Mapping Mode                | On On<br>Off                        |          | When you turn on this parameter, it allows the mapping<br>of the destination MAC address and VLAN tag CSE to<br>eCPRI message PC_ID field.                                                                                                                                      |  |  |  |

| Pair with ORAN                      | On<br>Off                           | Off      | Turn on this option to pair your eCPRI Intel FPGA IP with<br>Intel O-RAN FPGA IP. You can also pair your eCPRI Intel<br>FPGA IP with any external vendor O-RAN IP.<br>Note: When you turn on this parameter, the eCPRI Intel<br>FPGA IP only supports message type 0, 2, and 5. |  |  |  |

| Streaming                           | On<br>Off                           | Off      | Indicates Ethernet frame size.                                                                                                                                                                                                                                                  |  |  |  |

|                                     |                                     |          | continued                                                                                                                                                                                                                                                                       |  |  |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

## intel

| Parameter                                       | Supported<br>Values | Default Setting | Description                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------|---------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 |                     |                 | When you turn off this parameter, the maximum<br>Ethernet frame size can be 1500 bytes, and when you<br>turn on, the maximum Ethernet frame size can be 9,000<br>bytes.<br><i>Note:</i> When you turn on this parameter, the<br>sink_pkt_size port is available at the Sink<br>Interface of the eCPRI Intel FPGA IP.                                        |

| Interworking Function<br>(IWF) Support          | On<br>Off           | Off             | Turn on this option to connect your eCPRI IP with one<br>CPRI IP node.<br>The eCPRI Intel FPGA IP currently support IWF Type 0<br>only. It does not support IWF type 1 and type 2 in<br>current release of the IP.<br><i>Note:</i> When you turn on this parameter, the eCPRI Intel<br>FPGA IP supports message type 0, 2, 5, 6 and 7<br>with IWF function. |

| Interworking Function<br>(IWF) Type             | 0                   | 0               | Specifies eCPRI IP IWF type configuration. Currently the IP support IWF Type 0 configuration.                                                                                                                                                                                                                                                               |

| Interworking Function<br>(IWF) Number of CPRI   | 1                   | 1               | Specifies the number of CPRI MAC that can connect to IWF.                                                                                                                                                                                                                                                                                                   |

| Remote Memory Access<br>Timer Bit-width         | 12                  | 12              | Specifies bit-width of the request-response sequence<br>timer for the eCPRI message type 4.<br>This parameter triggers the timeout no memory access<br>response.                                                                                                                                                                                            |

| One-way Delay<br>Measurement Time Bit-<br>width | 16                  | 16              | Specifies bit-width of the request-response sequence<br>timer for the eCPRI message type 5,One-way delay<br>measurement.<br>This parameter triggers the timeout no memory access<br>response.                                                                                                                                                               |

| Remote Reset Timer Bit-<br>width                | 12                  | 12              | Specifies bit-width of the request-response sequence<br>timer for the eCPRI message type 6.<br>This parameter triggers the timeout no memory access<br>response.                                                                                                                                                                                            |

| Default MAC Source -<br>Address                 |                     | 0×000000000000  | Default MAC source address after cold and soft reset.                                                                                                                                                                                                                                                                                                       |

| Default MAC Destination<br>Address 0            | -                   | 0×000000000000  | Default MAC destination address 0 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default MAC Destination<br>Address 1            | -                   | 0x000000000000  | Default MAC destination address 1 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default MAC Destination<br>Address 2            | -                   | 0x00000000000   | Default MAC destination address 2 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default MAC Destination<br>Address 3            | -                   | 0×000000000000  | Default MAC destination address 3 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default MAC Destination<br>Address 4            | -                   | 0x000000000000  | Default MAC destination address 4 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default MAC Destination<br>Address 5            | -                   | 0x000000000000  | Default MAC destination address 5 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default MAC Destination<br>Address 6            | -                   | 0x00000000000   | Default MAC destination address 6 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default MAC Destination<br>Address 7            | -                   | 0x000000000000  | Default MAC destination address 7 after cold and soft reset.                                                                                                                                                                                                                                                                                                |

| Default VLAN ID                                 | -                   | 0x000           | Default VLAN ID after cold and soft reset.<br>continued                                                                                                                                                                                                                                                                                                     |

### 3. IP Parameters 683685 | 2023.02.24

# intel

| Parameter                       | Supported<br>Values         | Default Setting | Description                                                                                               |  |  |  |  |

|---------------------------------|-----------------------------|-----------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data Flow Identification        | MACADDR<br>VLANID           | MACADDR         | Use MAC Address or VLAN ID for Data Identification.                                                       |  |  |  |  |

| Packets Arbitration<br>Scheme   | L2COS<br>Fixed              | Fixed           | Specifies the TX packets arbitration scheme.                                                              |  |  |  |  |

| TX Packets Default<br>Priority  | 0 to 7                      | 7               | Indicates the default priority for S/M/other plane packets that doesn't contain VLAN ID within L2 header. |  |  |  |  |

| TX Arbitration Queue 0<br>Depth | 0<br>32<br>64<br>128<br>256 | 128             | Indicates the TX arbitration queue 0 depth. FIFO width is 8 Bytes.                                        |  |  |  |  |

| TX Arbitration Queue 1<br>Depth | 0<br>32<br>64<br>128<br>256 | 128             | Indicates the TX arbitration queue 1 depth. FIFO width is 8 bytes.                                        |  |  |  |  |

| TX Arbitration Queue 2<br>Depth | 0<br>32<br>64<br>128<br>256 | 128             | Indicates the TX arbitration queue 2 depth. FIFO width is 8 bytes.                                        |  |  |  |  |

| TX Arbitration Queue 3<br>Depth | 0<br>32<br>64<br>128<br>256 | 128             | Indicates the TX arbitration queue 3 depth. FIFO width is 8 bytes.                                        |  |  |  |  |

| TX Arbitration Queue 4<br>Depth | 0<br>32<br>64<br>128<br>256 | 128             | Indicates the TX arbitration queue 4 depth. FIFO width is 8 bytes.                                        |  |  |  |  |

| TX Arbitration Queue 5<br>Depth | 0<br>32<br>64<br>128<br>256 | 128             | Indicates the TX arbitration queue 5 depth. FIFO width is 8 bytes.                                        |  |  |  |  |

| TX Arbitration Queue 6<br>Depth | 0<br>32<br>64<br>128<br>256 | 128             | Indicates the TX arbitration queue 6 depth. FIFO width is 8 bytes.                                        |  |  |  |  |

| TX Arbitration Queue 7<br>Depth | 32<br>64<br>128<br>256      | 128             | Indicates the TX arbitration queue 7 depth. FIFO width is 8 bytes.                                        |  |  |  |  |

For parameters in the **Example Design** tab, refer to the *eCPRI Intel Stratix 10 FPGA Design Example User Guide*.

3. IP Parameters 683685 | 2023.02.24

## **Related Information**

- O-RAN Intel FPGA IP User Guide

- eCPRI Intel FPGA Design Example User Guide

- 25G Ethernet Intel Stratix 10 FPGA IP User Guide

- E-tile Hard IP User Guide

## **4. Functional Description**

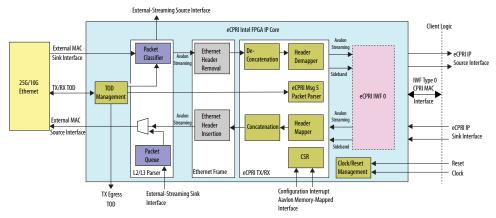

The eCPRI Intel FPGA IP core provides the functionality described in the *eCPRI* specification version 2.0.

## 4.1. Interfaces

The eCPRI Intel FPGA IP supports the following interfaces:

## • Clock and Reset Interface

The main interface for the clock and reset signals in the eCPRI IP.

#### • Configuration Avalon Memory-Mapped Interface

This interface provides access to the internal control and status registers of the eCPRI IP. This interface complies with Avalon memory-mapped interface specification as defined in the *Avalon Interface Specifications*.

#### • External MAC Source Interface

This interface provides datapath from eCPRI IP to 25G Ethernet MAC IP. This interface complies with Avalon streaming interface specification as defined in the *Avalon Interface Specifications*.

### • External MAC Sink Interface

This interface provides datapath from 25G Ethernet MAC IP to eCPRI IP. This interface complies with Avalon streaming interface specification as defined in the *Avalon Interface Specifications*.

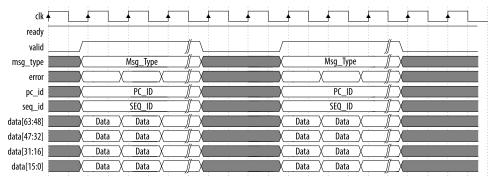

## • eCPRI IP Source Interface

This interface provides datapath from eCPRI IP to client logic. This interface includes a number of sideband signals which align with the Avalon streaming interface clock. This interface complies with Avalon streaming interface specification as defined in the *Avalon Interface Specifications*.

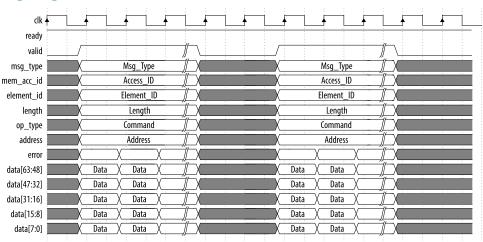

## • eCPRI IP Sink Interface

This interface provides datapath from client logic to eCPRI IP. This interface includes a number of sideband signals which align with the Avalon streaming interface clock. This interface complies with Avalon streaming interface specification as defined in the *Avalon Interface Specifications*.

## • IWF Type 0 eCPRI Source Interface

This interface provides datapath from eCPRI IP to IWF logic. This interface includes a number of sideband signals which align with the eCPRI IP source interface.

## • IWF Type 0 eCPRI Sink Interface

This interface provides datapath from IWF logic to eCPRI IP. This interface includes a number of sideband signals which align with the eCPRI IP source interface.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

## IWF Type 0 CPRI MAC Interface

This interface provides datapath from eCPRI IWF type 0 function to CPRI MAC. This interface consists of the following interfaces:

- CPRI 32-bit IQ Data

- CPRI 64-bit IQ Data

- CPRI 32-bit Ctrl\_AxC

- CPRI 64-bit Ctrl\_AxC

- CPRI 32-bit Vendor Specific

- CPRI 64-bit Vendor Specific

- CPRI 32-bit Real-Time Vendor Specific

- CPRI 64-bit Real-Time Vendor Specific

- CPRI Gigabit Media Independent Interface (GMII)

## External ST Source Interface

This interface provides datapath from eCPRI IP to client logic. This interface is a primary output interface for PTP and C&M messages. This interface complies with Avalon streaming interface specification as defined in the *Avalon Interface Specifications*. This interface includes a number of sideband signals which align with the Avalon streaming interface clock.

## External ST Sink Interface

This interface provides datapath from client logic to eCPRI IP. This interface is a primary input for PTP and C&M messages. This interface complies with Avalon streaming interface specification as defined in the *Avalon Interface Specifications*.

## • TX and RX Time-of-Day (TOD) Interface:

This interface provides 96-bit timestamp from PTP module to eCPRI IP core and to client logic.

## Figure 6. eCPRI Intel FPGA IP High-Level System Overview

## **Related Information**

- eCPRI Specification V2.0

- Avalon Interface Specifications

- 1588 Precision Time Protocol Interfaces For 25G Ethernet Intel Stratix 10 Intel FPGA IP

- 1588 Precision Time Protocol Interfaces For E-tile Hard IP for Ethernet Intel FPGA IP

## 4.2. High Level Data Path Flow

The eCPRI IP core consists of two paths:

- Transmit TX path

- Receive RX Path

## 4.2.1. Transmit TX Path

There are two sets of Avalon streaming interface source and sink signals available to the incoming packets on the transmit TX path. Avalon streaming interface source/sink connects to the eCPRI IP and external source/sink interface connects to external user logic. The incoming eCPRI packets passes through Ethernet header insertion block to insert Ethernet header, optionally with different VLAN tags, IPv4, and UDP headers configured during configuration time.

You can send different types of packets through the external source/sink interface signal (For example, C&M and synchronization packets) which arbitrates with eCPRI packets and the IP sends packets with the higher priority to Ethernet MAC for transmission. The incoming external user packets are expected to arrive with Ethernet MAC header inserted on the packets.

The eCPRI IP supports two types of packets arbitration:

- Fixed priority arbitration

- L2 CoS priority arbitration based on the O-RAN Control, User and Synchronization Plane Specification 7.01 (ORAN-WG4.CUS.0-v07.01), Section 5.3 Quality of Service.

Both of the arbitration features are mutually exclusive to each other and you can enable one of them using the **Packets Arbitration Scheme** parameter.

For fixed priority arbitration, the priority of the packets send to Ethernet MAC is listed as below, with highest priority order from top to bottom:

- PTP synchronization packet

- eCPRI packet

- C&M packets and remaining type of packets

The C&M and PTP synchronization packets are send/receive through external source/ sink interface signal. The C&M and PTP synchronization packets are generally low bandwidth traffic. When there is collision between external PTP synchronization packets and eCPRI packets, backpressure to the eCPRI IP occurs to stop eCPRI packets from transmitting. The eCPRI IP implements a counter to track the number of eCPRI packets and PTP packets granted and raise the priority of the C&M packet when the counter reaches a programmable threshold to allow the C&M packet transmission to Ethernet MAC and avoid starvation.

Ensure the bandwidth of external source/sink interface signal won't starve the overall bandwidth and cause interruption on eCPRI traffics. The grant ratio between C&M packets versus eCPRI/PTP packets is 10:1. The bandwidth allocated to C&M packets is 2.5G or 1G. The maximum C&M/PTP FIFO depth is 256 or 2048 bytes for eCPRI IP. The C&M/PTP FIFO should not be kept full beyond 2062.5 \* (mac\_clk\_tx) clock period, to allow for enough read margin prior to the arrival of the new packets.

When you set the Ethernet frame size to 9000 bytes, data from Avalon streaming interface sink directly pass through and does not required buffering. You must assert avst\_sink\_valid continuously between the assertions of avst\_sink\_sop and avst\_sink\_eop. The only exception is when avst\_sink\_ready signal deasserts, and you are required to deassert avst\_sink\_valid for three cycles of READY\_LATENCY.

The second L2 CoS priority arbitration is based on the *ORAN-WG4.CUS.0-v07.01 specification, Section 5.3 Quality of Service*, where the L2 CoS Priority of the packet determines the arbitration priority of the packet. You can enable this arbitration with Advance Mapping Mode. There are eight queues available to queue the packets for arbitration. Each queue is assigned with fixed priority 0 to 7, where queue 7 has the highest arbitration priority, and queue 0 has the lowest arbitration priority. Packets are stored into each queue according to the Priority Code Point (PCP) tag value extracted from the packet; for example, a packet with the PCP tag value of 7 is queued into queue 7.

The queue size for each priority must be configurable independently and use M20K to reduce ALM count. Queue depth must be configurable with a depth of 0/32/64/128/256 based on IP parameter selection per queue. The unused queue shall be configurable with the size of 0 to ensure no resource wastage. For queue 7, the minimum size is 32, and value 0 is not allowed to avoid a case where all queues are 0 sizes. When a particular queue size is configured to 0 (other than queue 7) and there is a request decoded with the PCP tag value of the queue, the request shall be routed to queue 7.

The ORAN C/U Plane packet uses the eCRPI IP Advance Mapping Mode feature to get the PCP value for the packet. When ORAN C/U Plane packet is sent into eCPRI IP, eCPRI IP uses the PCID sent as sideband and the packet to map to the VLAN tag register. The PCP values extracted from the VLAN tag register determine the queue to store the ORAN C/U Plane packet. The PCP field is a user input at packet SOP for S Plane, M-plane, and other traffic. Packets are stored in the queue according to the PCP field.

The PCP checker arbitrates the traffic (C/U/S/M/Other) based on the PCP tag value in the round-robin and stores it into the respective queue. Since the PTP software stack might not always generate PTP packets with the VLAN ID, the following statements explain the PCP values for handling each ITU-T profilethe the adetermine:

- The first two profiles (8264 and 8275.1 profiles) No VLAN ID (IP assigns the priority based on the TX Packets Default Priority parameter, default to highest 7).

- The third profile (8275.2 profile) parse PTP packet to extract PCP from L2/L3 header.

- The primary use case is based on the L2 header and not the L3 header (8275.2 profile) parser can parse the L2 header only to determine PTP packets and no L3 header parsing.

When the arbitration queue is full, backpressure applies to both eCPRI IP and S/M packets DCFIFO. Backpressure shall only apply on the same priority request. For example, when queue 7 is full, back pressure happens on traffic with PCP = 7 only (can be S/U/C/M plane traffic). Due to one input from ORAN IP for the U plane, subsequent packets with different priorities are blocked when the head of traffic is blocked. If the queue full happens in the middle of the packet, you must submit the remaining packet to the queue before switching to other traffic.

Run time priority change on traffic: You can switch PCP field values at packet boundary only, priority should remain the same for whole packet.

There is no starvation handling in hardware. For example, low-priority traffic always gives way to high-priority traffic and waits for its turn. Therefore, you are expected to handle the traffic flow between different queues to ensure no starvation scenarios which causes low-priority traffic continuously to get stuck in the queue without getting the arbitration grant.

Each queue generates FIFO full port and sends it to the eCPRI IP interface.

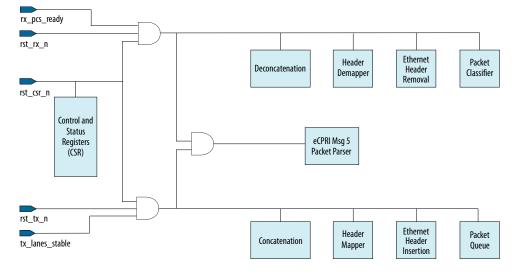

## 4.2.2. Receive RX Path

The receiving Ethernet frames from the Ethernet MAC first enters packet classifier block. Packet classifier block classifies the packet into eCPRI packets and non-eCPRI packets. The packet classifier sends eCPRI packets with matching MAC address to the Ethernet header removal block of the eCPRI IP, while sends all other non-eCPRI packets or eCPRI packets with non-matching MAC address to external user logic for processing.

The **Data Flow Identification** parameter determines the reset default value of match\_macaddr\_vlanid register bit of cu\_vlanid\_match\_address register. This register bit can be overridden during run time. You shall handle the Run time Data Flow Identification change gracefully (for example, empty the traffic before switching) to avoid indeterministic behavior or decision on the packet routing.

For detailed information on conditions when the IP classifies packet as eCPRI packet, refer to section *Packet Classifier*.

#### **Related Information**

Packet Classifier on page 24

## 4.2.3. Supported Ethernet Variants

The eCPRI Intel FPGA IP pairs together with the 25G/10G Ethernet. The eCPRI IP is validated together with the 25G Ethernet for Intel Stratix 10 designs.

For your Intel Stratix 10 designs, you can select **25G Ethernet Intel FPGA IP** for Htile variants and **E-tile Hard IP for Ethernet Intel FPGA IP** for E-tile variants. When you use these IPs, you must set the following parameter values in the IP parameter editor:

Select Ethernet Rate if you use E-tile Hard IP for Ethernet Intel FPGA IP.

*Note:* This option is not available with **25G Ethernet Intel FPGA IP**. Use **Enable 10G/25G dynamic rate switching** for 10G data rate.

- Enable Enable IEEE 1588 parameter to support client PTP message and eCPRI one-way delay measurement. The 25G Ethernet MAC only supports 96-bit (V2) timestamp format.

- Disable Enable preamble pass-through and Enable TX CRC pass-through parameters.

- Turn on **Enable 10G/25G dynamic rate switching** option to switch between 10G and 25G data rates.

For your Intel Arria 10 designs, you can use **Low Latency Ethernet 10G MAC Intel FPGA IP** and **1G/10GbE and 10GBASE-KR PHY Intel FPGA IP** to implement MAC and PHY respectively for your Ethernet.

#### **Related Information**

- 25G Ethernet Intel Stratix 10 FPGA IP User Guide

- E-tile Hard IP User Guide

- Low Latency Ethernet 10G MAC Intel FPGA IP User Guide

## 4.3. Operation of the eCPRI IP Blocks

The following section explains the operation of the eCPRI IP blocks.

## 4.3.1. Packet Classifier

The packet classifier parses the incoming Ethernet frame to identify the types of incoming packets. The incoming packets could be eCPRI packet, PTP packet, or C&M packet with different types of frames (e.g., standard Ethernet frame, IPv4, and etc.)

Packet classifier redirects eCPRI packets to next component for further processing and classifies a packet as eCPRI packet if all the condition listed in the table below met. The packet classifier sends all non-eCPRI packets and eCPRI packets with non-matching MAC address fields to external Avalon streaming interface.

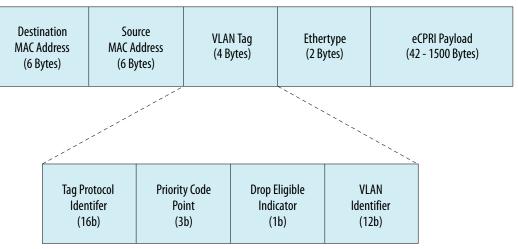

#### Table 10. Ethernet Frame Format (User Data over Ethernet)

| Number of Bits | RX Frame                                                                                                | Condition                                                            |  |  |

|----------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| 48             | MAC Destination address                                                                                 | Destination MAC address matches receiver source MAC address.         |  |  |

| 48             | MAC Source address                                                                                      | Do not check.                                                        |  |  |

| 32 (Optional)  | VLAN tag                                                                                                | Packet parser checks for VLAN tag and adjust the offset accordingly. |  |  |

| 32 (Optional)  | Optional)         Stack VLAN tag         Packet parser checks for SVLAN tag and the offset accordingly. |                                                                      |  |  |

| 16             | Ethertype (2 Bytes)= IP                                                                                 | Ethertype is equal to 0xAEFE                                         |  |  |

If eCPRI message transmitted over IP/UDP, the IP supports only IPv4 with UDP.

| No. of Bits   | IPv4 Header                               | Condition                                                             |  |  |  |

|---------------|-------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| 48            | MAC destination address                   | Destination MAC address matches receiver source MAC address.          |  |  |  |

| 48            | MAC source address                        | Do not check.                                                         |  |  |  |

| 32 (Optional) | VLAN Tag                                  | Packet parser checks for VLAN tag and adjusts the offset accordingly. |  |  |  |

| 32 (Optional) | Stack VLAN Tag                            | Packet parser checks for SVLAN tag and adjust the offset accordingly. |  |  |  |

| 16            | Ethertype (2B) = IP                       | Ethertype must be 0x0800 for IPv4.                                    |  |  |  |

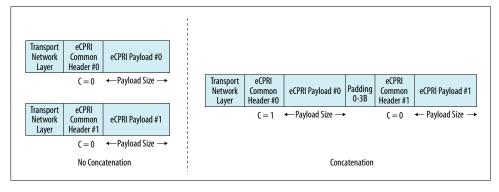

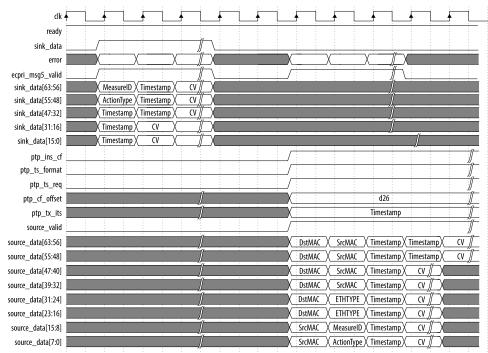

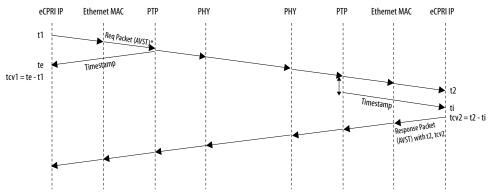

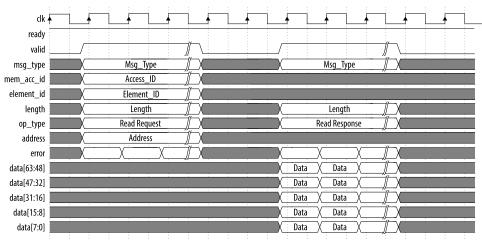

| 4             | Version                                   | Version must be 4'h4.                                                 |  |  |  |