# Intel® Stratix® 10 SoC FPGA Boot User Guide

Updated for Intel® Quartus® Prime Design Suite: 22.4

Version: **2023.01.20**

ID: 683847

# **Contents**

| 1. Int | roduction                                                 | . 4 |

|--------|-----------------------------------------------------------|-----|

|        | 1.1. Glossary                                             | 4   |

|        | 1.2. Intel Stratix 10 SoC FPGA Boot Overview              |     |

|        |                                                           |     |

| 2. FP( | GA Configuration First Mode                               |     |

|        | 2.1. Boot Flow Overview for FPGA Configuration First Mode |     |

|        | 2.1.1. Power-On Reset (POR)                               |     |

|        | 2.1.2. Secure Device Manager                              | 8   |

|        | 2.1.3. First-Stage Bootloader                             |     |

|        | 2.1.4. Second-Stage Bootloader                            | 9   |

|        | 2.1.5. Operating System                                   |     |

|        | 2.1.6. Application                                        | 9   |

|        | 2.2. System Layout for FPGA Configuration First Mode      | 10  |

|        | 2.2.1. External Configuration Host Only                   |     |

|        | 2.2.2. External Configuration Host with HPS Flash         | 11  |

|        | 2.2.3. Single SDM Flash                                   |     |

|        | 2.2.4. FPGA Configuration - First Dual Flash System       | 12  |

| 2 40   | S Boot First Mode                                         | 1 1 |

| э. пР  |                                                           |     |

|        | 3.1. Boot Flow Overview                                   |     |

|        | 3.1.1. Power-On Reset (POR)                               |     |

|        | 3.1.2. Secure Device Manager                              |     |

|        | 3.1.3. First-Stage Bootloader                             |     |

|        | 3.1.4. Second-Stage Bootloader                            |     |

|        | 3.1.5. Operating System                                   |     |

|        | 3.1.6. Application                                        |     |

|        | 3.2. System Layout for HPS Boot First Mode                |     |

|        | 3.2.1. External Configuration Host Only                   |     |

|        | 3.2.2. External Configuration Host with HPS Flash         |     |

|        | 3.2.3. Single SDM Flash                                   |     |

|        | 3.2.4. HPS Boot First - Dual Flash System                 | 22  |

| 4. Cre | ating the Configuration Files                             | 23  |

|        | 4.1. Overview                                             | 23  |

|        | 4.2. Intel Quartus Prime Hardware Project Compilation     |     |

|        | 4.2.1. Device and Pin Options                             |     |

|        | 4.2.2. Platform Designer Options                          |     |

|        | 4.3. Bootloader Software Compilation                      |     |

|        | 4.4. Programming File Generator                           |     |

|        | 4.5. Configuration over JTAG                              | 27  |

|        | 4.5.1. FPGA Configuration First                           |     |

|        | 4.5.2. HPS Boots First                                    |     |

|        | 4.6. Configuration from QSPI                              |     |

|        | 4.6.1. Supported QSPI Devices                             |     |

|        | 4.6.2. FPGA Configuration First                           |     |

|        | 4.6.3. HPS Boot First                                     |     |

|        | 4.7. Configuration over AVST                              |     |

|        |                                                           | 38  |

| 4.7.2. HPS Boot First                                                      | 41 |

|----------------------------------------------------------------------------|----|

| 4.8. Configuration via Protocol                                            | 44 |

| 4.8.1. Creating Configuration Files from Command Line                      | 45 |

| 4.8.2. Creating Configuration Files Using Graphical Interface              | 46 |

| 4.9. Remote System Update                                                  |    |

| 4.10. Partial Reconfiguration                                              | 50 |

| 5. Golden System Reference Design and Design Examples                      | 53 |

| 5.1. Golden System Reference Design                                        | 53 |

| 5.2. Bootloader Examples                                                   |    |

| 5.3. Additional Design Examples                                            |    |

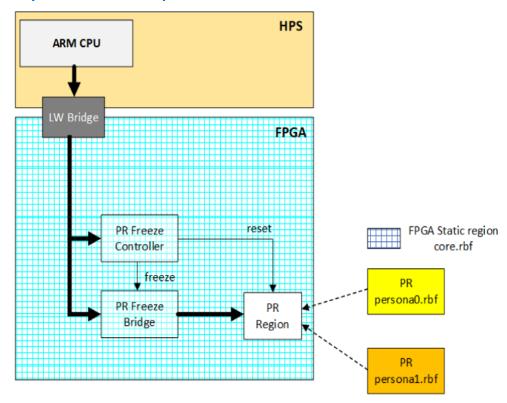

| 6. Configuring the FPGA Fabric from HPS Software                           | 55 |

| 6.1. Configuring the FPGA Fabric from U-Boot                               | 55 |

| 6.2. Configuring the FPGA Fabric from Linux                                |    |

| 6.3. FPGA Partial Reconfiguration from Linux                               | 57 |

| 7. Debugging the Intel Stratix 10 SoC FPGA Boot Flow                       | 61 |

| 7.1. Reset                                                                 | 61 |

| 7.1.1. HPS Reset Pin                                                       | 62 |

| 7.1.2. L4 Watchdog Timer 0                                                 | 63 |

| 7.2. Debugging the HPS Bootloader Using the Arm DS Intel SoC FPGA Edition  | 63 |

| 7.3. Other Debug Considerations                                            | 63 |

| 8. Intel Stratix 10 SoC FPGA Boot User Guide Archives                      | 67 |

| 9. Document Revision History for Intel Stratix 10 SoC FPGA Boot User Guide | 68 |

| J. Document Revision instory for Interstratik to soc i FGA boot oser duide |    |

# 1. Introduction

This user guide describes the Intel® Stratix® 10 SoC FPGA boot flow, boot sources, and how to generate a bitstream required for successful booting of the device. The details provided in this boot user guide include:

- The typical boot flows and boot stages of the Intel Stratix 10 SoC FPGA.

- The supported system layout for different hard processor system (HPS) boot modes.

- How to use Intel Quartus<sup>®</sup> Prime Pro Edition to generate the configuration bitstream.

## 1.1. Glossary

Table 1. Intel Stratix 10 SoC FPGA Boot Glossary

| Term                 | Definition                                                                                                                                                                                                                                                                            |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EMIF                 | External memory interface                                                                                                                                                                                                                                                             |  |

| *.pof                | Programming object file; contains data to configure the FPGA portion of the SoC and additionally, may contain the HPS first-stage payload. This file is typically stored in external flash such as quad serial peripheral interface (Quad SPI) or common flash interface (CFI) flash. |  |

| FW                   | Firmware; Controls and monitors software stored in Secure Device Manager's (SDM) read-only memory.                                                                                                                                                                                    |  |

| HPS                  | Hard Processor System; the SoC portion of the device, consisting of a quad core Arm* Cortex-A53 processor, hard IPs, and HPS I/Os in the Intel Stratix 10 SoC FPGA.                                                                                                                   |  |

| HPS EMIF I/O section | Part of the raw binary file (*. $rbf$ ) that configures the EMIF I/O used by the HPS                                                                                                                                                                                                  |  |

| FPGA I/O section     | Part of the *.rbf that configures the I/O assigned to the FPGA core                                                                                                                                                                                                                   |  |

| Core *.rbf           | Core raw binary file; FPGA core image file that includes logic array blocks (LABs), digital signal processing (DSP), and embedded memory. The core image consists of a single reconfigurable region, or both static and reconfigurable regions.                                       |  |

| FSBL                 | First-stage Bootloader for HPS                                                                                                                                                                                                                                                        |  |

| *.jic                | JTAG Indirect Configuration file that allows programming through JTAG                                                                                                                                                                                                                 |  |

| OS                   | Operating system                                                                                                                                                                                                                                                                      |  |

| *.rbf                | Raw binary file representing the FPGA bitstream                                                                                                                                                                                                                                       |  |

| *.rpd                | Raw Programming Data file for AS devices                                                                                                                                                                                                                                              |  |

|                      | continued                                                                                                                                                                                                                                                                             |  |

| Term  | Definition                                                                                                                                                                      |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| *.sof | SRAM object file which contains the bitstream for the primary FPGA design. Firmware is not part of the *.sof.                                                                   |  |

| SSBL  | Second-stage Bootloader for HPS                                                                                                                                                 |  |

| SDM   | Secure Device Manager; a triple-redundant processor-based block that manages FPG configuration and hard processor system (HPS) secure boot process in Intel Stratix 10 devices. |  |

## 1.2. Intel Stratix 10 SoC FPGA Boot Overview

The Intel Stratix 10 SoC FPGA combines an FPGA with a hard processor system (HPS) that is capable of booting Bare Metal applications or operating systems such as  $Linux^*$ .

When booting the device from a power-on reset, you can choose between two different methods of booting:

FPGA Configuration First Mode—When you select the FPGA First option, the SDM fully configures the FPGA, then configures the HPS SDRAM pins, loads the HPS first-stage bootloader (FSBL) and takes the HPS out of reset.

Note: The FPGA and all of the I/Os are fully configured before the HPS is released from reset. Thus, when the HPS boots, the FPGA is in user mode and is ready to interact with the HPS. Optionally, the SDM can hold the HPS in reset until instructed by the user. To release the HPS from reset, you can use soft IP such as a mailbox client to send a mailbox request to the SDM.

HPS Boot First Mode—When you select the HPS First option, the SDM first

configures the HPS SDRAM pins, loads the HPS FSBL and takes the HPS out of

reset. Then the HPS configures the FPGA I/O and FPGA fabric at a later time.

Note: This mode is also referred to as Early I/O Release Mode or Early I/O Configuration. After power-on, the device configures a minimal amount of I/O required by the HPS before releasing the HPS from reset. This mode allows the HPS to boot quickly without having to wait for the full configuration to complete. Subsequently, the HPS may trigger an FPGA configuration request during the SSBL or OS stage.

# 2. FPGA Configuration First Mode

## 2.1. Boot Flow Overview for FPGA Configuration First Mode

You can program the Intel Stratix 10 SoC device to configure the FPGA first and then boot the HPS. The available configuration data sources configure the FPGA core and periphery first in this mode. After completion, you may optionally boot the HPS. All of the I/O, including the HPS-allocated I/O, are configured and brought out of tri-state. If the HPS is not booted:

- The HPS is held in reset.

- HPS-dedicated I/O are held in reset.

- HPS-allocated I/O are driven with reset values from the HPS.

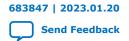

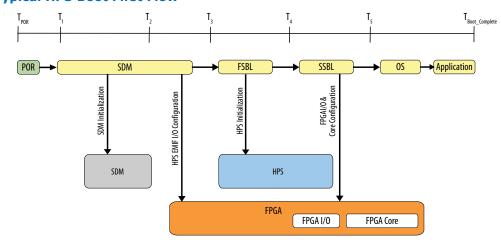

If the FPGA is configured before the HPS boots, the boot flow looks like the example figure below. The flow includes the time from power-on-reset  $(T_{POR})$  to boot completion  $(T_{Boot\_Complete})$ .

Figure 1. Typical FPGA Configuration First Boot Flow

#### **Table 2. FPGA Configuration First Stages**

The sections following this table describe each stage in more detail.

| Time                                         | Boot Stage                           | Device State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>POR</sub> to T <sub>1</sub>           | POR                                  | Power-on reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| T <sub>1</sub> to T <sub>2</sub>             | Secure Device Manager (SDM)-Boot ROM | <ol> <li>SDM samples the MSEL pins to determine the configuration scheme and boot source.</li> <li>SDM establishes the device security level based on eFuse values.</li> <li>SDM initializes the device by reading the configuration firmware (initial part of the bitstream) from the boot source.</li> <li>SDM authenticates and decrypts the configuration firmware (this process occurs as necessary throughout the configuration).</li> <li>SDM starts executing the configuration firmware.</li> </ol> |

| T <sub>2</sub> to T <sub>3</sub>             | SDM- configuration firmware          | <ol> <li>SDM I/O are enabled.</li> <li>SDM configures the FPGA I/O and core (full configuration) and enables the rest of your configured SDM I/O.</li> <li>SDM loads the FSBL from the bitstream into HPS on-chip RAM.</li> <li>SDM enables HPS SDRAM I/O and optionally enables HPS debug.</li> <li>FPGA is in user mode.</li> <li>HPS is released from reset. CPU1-CPU3 are in a wait-for-interrupt (WFI) state.</li> </ol>                                                                                |

| T <sub>3</sub> to T <sub>4</sub>             | First-Stage Bootloader (FSBL)        | <ol> <li>HPS verifies the FPGA is in user mode.</li> <li>The FSBL initializes the HPS, including the SDRAM.</li> <li>HPS loads SSBL into SDRAM.</li> <li>HPS peripheral I/O pin mux and buffers are configured. Clocks, resets, and bridges are also configured.</li> <li>HPS I/O peripherals are available.</li> </ol>                                                                                                                                                                                      |

| T <sub>4</sub> to T <sub>5</sub>             | Second-Stage Bootloader (SSBL)       | HPS bootstrap completes.     OS is loaded into SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| T <sub>5</sub> to T <sub>Boot_Complete</sub> | Operating System (OS)                | The OS boots and applications are scheduled for runtime launch.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Note:

The location of the source files for configuration, FSBL, SSBL, and OS can vary and are described in the *System Layout for FPGA Configuration First Mode* section.

#### **Related Information**

System Layout for FPGA Configuration First Mode on page 10

## 2.1.1. Power-On Reset (POR)

Ensure you power each of the power rails according to the power sequencing consideration until they reach the required voltage levels. In addition, the power-up sequence must meet either the standard or the fast power-on reset (POR) delay time.

#### **Related Information**

- Intel Stratix 10 Device Data Sheet

For information about the POR delay specification

- AN 692: Power Sequencing Considerations for Intel Cyclone<sup>®</sup> 10 GX, Intel Arria<sup>®</sup> 10, Intel Stratix 10, and Intel Agilex<sup>™</sup> Devices

## 2.1.2. Secure Device Manager

Once the Intel Stratix 10 SoC FPGA exits POR, the SDM samples the  $\mathtt{MSEL}[2:0]$   $\mathsf{pins}^{(1)}$  to determine the boot source. Next, the device configures the SDM I/Os according to the selected boot source interface and the SDM retrieves the configuration bitstream through the interface. SDM can boot from the following boot sources listed in the following table.

Table 3. Available SDM Boot Sources for the Intel Stratix 10 SoC FPGA

| SDM Boot Source              | Details                                                                                                                                                                                                                                       |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Avalon-ST (x8/x16/x32)       | Supported                                                                                                                                                                                                                                     |

| JTAG                         | Supported                                                                                                                                                                                                                                     |

| Active Serial (AS)/ Quad SPI | Supported. SDM only boots in x4 mode for active serial flash and Micron* MT25Q flash. Other supported quad SPI flash devices boot in x1 mode. After the configuration firmware loads into the SDM, the SDM can switch the flash into x4 mode. |

The typical configuration bitstream for FPGA configuration first contains:

- 1. Configuration firmware for the SDM

- 2. FPGA I/O and HPS external memory interface (EMIF) I/O configuration data

- 3. FPGA core configuration data

- 4. HPS FSBL code and FSBL hardware handoff binary data

The SDM completes the configuration of the FPGA core and I/O, and then copies the HPS FSBL code and HPS FSBL hardware handoff binary to the HPS on-chip RAM.

#### **Related Information**

- System Layout for HPS Boot First Mode on page 19

- Intel Stratix 10 Configuration User Guide

#### 2.1.3. First-Stage Bootloader

The first-stage bootloader (FSBL) is the first boot stage for the HPS. In FPGA Configuration First mode, the SDM extracts and loads the FSBL into the on-chip RAM of the HPS. The SDM releases the HPS from reset after the FPGA has entered user mode. After the HPS exits reset, it uses the FSBL hardware handoff file to setup the clocks, HPS dedicated I/Os, and peripherals. Typically, the FSBL then loads the SSBL into HPS SDRAM and passes control to the SSBL.

<sup>(1)</sup> The MSEL[2:0] pins are multiplexed with the SDM\_IO[9], SDM\_IO[7], SDM\_IO[5] pins respectively.

683847 | 2023.01.20

You can create the FSBL from one of the following sources:

- U-Boot secondary program loader (SPL)

- Intel provides the source code for U-Boot on GitHub.

- Arm Trusted Firmware

- Intel provides the source code for the Arm Trusted Firmware on GitHub.

#### **Related Information**

- Creating the Configuration Files on page 23

- U-Boot Source Code on GitHub

- Arm Trusted Firmware Source Code on GitHub

## 2.1.4. Second-Stage Bootloader

The second-stage bootloader (SSBL) is the second boot stage for the HPS. The FSBL initiates the copy of the SSBL to the HPS SDRAM. The SSBL typically enables more advanced peripherals such as Ethernet and supports command line interface.

You can create the SSBL from one of the following sources:

- U-Boot

- Intel provides the source code for U-Boot on GitHub.

- UEFI

- Intel provides the source code for UEFI on GitHub.

- RTOS

- · Bare Metal application

#### **Related Information**

- UEFI Source Code on GitHub

- U-Boot Source Code on GitHub

- Arm Trusted Firmware Source Code on GitHub

## 2.1.5. Operating System

Typically, the SSBL loads the operating system (OS) stage into SDRAM. The OS executes from SDRAM. Depending on your application requirements, you may implement a conventional OS or an RTOS.

Intel provides the Golden System Reference Design (GSRD) which includes the Linux kernel and a root filesystem built with Yocto recipes.

#### **Related Information**

Golden System Reference Design and Design Examples on page 53

#### 2.1.6. Application

The application that runs on the OS is the last boot stage. The application can also replace the OS stage as a dedicated, Bare Metal runtime code.

## 2.2. System Layout for FPGA Configuration First Mode

The following sections describe the supported system layout for FPGA Configuration First mode. The OS is assumed to be Linux in the following examples, but you may replace Linux with other supported operating systems.

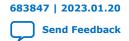

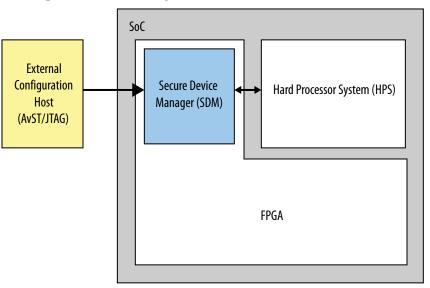

## 2.2.1. External Configuration Host Only

Figure 2. External Configuration Host Only

In this example, the external configuration host (Avalon® streaming or JTAG) provides the SDM with a configuration bitstream that consist of:

- SDM configuration firmware

- FPGA I/O and HPS EMIF I/O configuration data

- FPGA core configuration data

- HPS FSBL code and HPS FSBL hardware handoff binary

Because the HPS SSBL (or subsequent OS) is not part of the bitstream, the HPS can only boot up to the FSBL stage. This setup is applicable if you are using the FSBL to run simple applications (for example, Bare Metal applications).

You can use the FSBL to retrieve the SSBL from other sources, such as through the HPS Ethernet MAC interface. To implement these modes of access, you must create a working Ethernet software stack in the FSBL.

**Table 4.** Supported Configuration Boot and SSBL Source

| SDM Configuration Host | SSBL Source  | Details                           |

|------------------------|--------------|-----------------------------------|

| Avalon streaming       | HPS Ethernet | Not supported in U-Boot FSBL code |

| JTAG                   |              | provided by Intel.                |

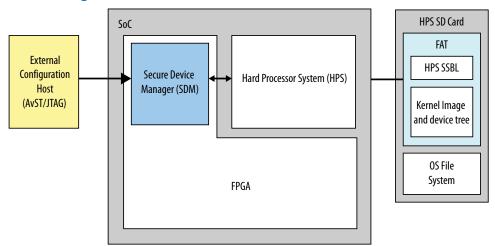

#### 2.2.2. External Configuration Host with HPS Flash

Figure 3. External Configuration Host with HPS Flash

An external configuration host with HPS flash provides an SDM configuration bitstream containing:

- SDM configuration firmware

- FPGA I/O and HPS EMIF I/O configuration data

- FPGA core configuration data

- HPS FSBL code and HPS FSBL hardware handoff binary

In this system layout, you can use the HPS flash to store the HPS SSBL, Linux image device tree information and OS file system. This layout enables the device to boot into an OS such as Linux.

All HPS flash devices are supported:

- SD Card

- eMMC

- NAND

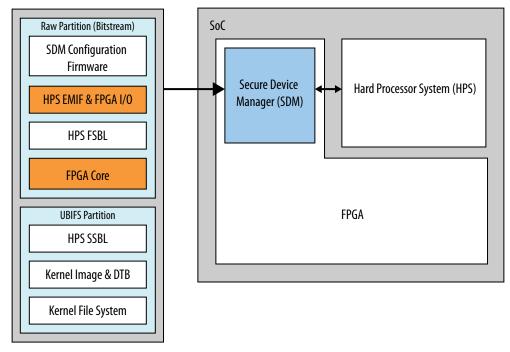

#### 2.2.3. Single SDM Flash

In this case, the Quad SPI flash connected to the SDM contains all the data required for configuring and booting the system, including the configuration bitstream, bootloader and OS files.

Note:

When you use the HPS to access the SDM Quad SPI, it operates at a lower bandwidth of  $\sim$ 4-6 MB/s. This is due to the high latency of the PSI link between HPS and SDM, and the fact that all transfers are done in Programmed IO (PIO) mode, instead of DMA mode.

Software running on the HPS must request permission from the SDM to get exclusive access to the QSPI before using it. This is already implemented in the U-Boot and UEFI bootloaders supported by Intel.

Figure 4. FPGA Configuration First Layout with Quad SPI

#### **Related Information**

- Intel Stratix 10 Hard Processor System Technical Reference Manual For more information, refer to the Booting and Configuration Appendix

- Intel Stratix 10 SoC FPGA First Single QSPI Flash Boot

## 2.2.4. FPGA Configuration - First Dual Flash System

In a dual flash system, the SDM flash stores the configuration bitstream, while the HPS flash stores the HPS SSBL and the rest of the OS files.

Figure 5. FPGA Configuration First - Dual Flash devices (SDM and HPS)

683847 | 2023.01.20

#### **Related Information**

- RocketBoards: Intel Stratix 10 SoC GSRD

- Golden System Reference Design and Design Examples on page 53

## 3. HPS Boot First Mode

#### 3.1. Boot Flow Overview

You can boot the HPS and HPS EMIF I/O first before configuring the FPGA core and periphery. The MSEL[2:0] settings determine the source for booting the HPS. In this mode, any of the I/O allocated to the FPGA remain tri-stated while the HPS is booting. The HPS can subsequently request the SDM to configure the FPGA core and periphery, excluding the HPS EMIF I/O. Software determines the configuration source for the FPGA core and periphery. In HPS First Boot mode, you have the option of configuring the FPGA core during the SSBL stage or after the operating system boots.

Note:

Configuring the HPS EMIF I/O for the first time and then loading the HPS FSBL is called "Phase 1 configuration". The subsequent configuration of FPGA core and periphery by HPS is called "Phase 2 configuration". The phase 1 and phase 2 configuration files must be generated from the same Intel Quartus Prime Pro Edition software version, this includes patches installed if applicable.

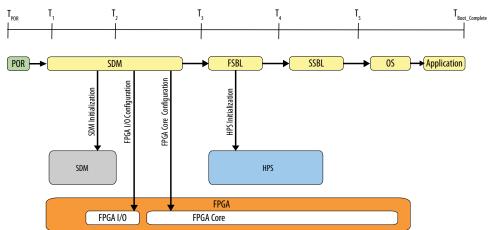

A typical HPS First Boot flow may look like the following figure. You can use U-Boot, Unified Extensible Firmware Interface (UEFI), or a custom bootloader for your FSBL or SSBL. An example of an OS is Linux or an RTOS. The flow includes the time from power-on-reset ( $T_{POR}$ ) to boot completion ( $T_{Boot\ Complete}$ ).

Figure 6. Typical HPS Boot First Flow

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

**Table 5. HPS Boot First Stages**

| Time                                         | Boot Stage                     | Device State                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>POR</sub>                             | POR                            | Power-on reset                                                                                                                                                                                                                                                                                                                                                                                                  |

| T <sub>1</sub> to T <sub>2</sub>             | SDM- Boot ROM                  | <ol> <li>SDM samples the MSEL pins to determine the configuration and boot source. It also establishes the device security level based on eFuse values.</li> <li>SDM firmware initializes the device.</li> <li>SDM authenticates and decrypts the bitstream (this process occurs as necessary throughout the configuration).</li> </ol>                                                                         |

| T <sub>2</sub> to T <sub>3</sub>             | SDM- Configuration Firmware    | <ol> <li>SDM configures the HPS EMIF I/O and the rest of the user-configured SDM I/O.</li> <li>SDM loads the FSBL from the bitstream into HPS on-chip RAM.</li> <li>SDM enables HPS SDRAM I/O and optionally enables HPS debug.</li> <li>HPS is released from reset.</li> </ol>                                                                                                                                 |

| T <sub>3</sub> to T <sub>4</sub>             | First Stage Bootloader (FSBL)  | <ol> <li>The FSBL initializes the HPS, including the SDRAM.</li> <li>FSBL obtains the SSBL from HPS flash or by requesting flash access from the SDM.</li> <li>FSBL loads the SSBL into SDRAM.</li> <li>HPS peripheral I/O pin multiplexer and buffers are configured. Clocks, resets and bridges are also configured.</li> <li>HPS I/O peripherals are available.</li> <li>HPS bootstrap completes.</li> </ol> |

| T <sub>4</sub> to T <sub>5</sub>             | Second Stage Bootloader (SSBL) | After bootstrap completes, any of the following steps may occur:  1. The FPGA core configuration loads into SDRAM from one of the following sources:  • SDM flash  • HPS alternate flash  • EMAC interface  2. HPS requests that the SDM configure the FPGA core. (2)  3. FPGA enters user mode.  4. OS is loaded into SDRAM.                                                                                   |

| T <sub>5</sub> to T <sub>Boot_Complete</sub> | Operating System (OS)          | OS boot occurs and the OS schedules applications for runtime launch.     (Optional step)The OS initiates FPGA configuration through a secure monitor call (SMC) to the resident SMC handler (typically SSBL), which then initiates the request to the SDM.                                                                                                                                                      |

Note: The location of the source files for configuration, FSBL, SSBL and OS can vary. For more information, refer to the System Layout for HPS Boot First Mode section.

<sup>(2)</sup> FPGA I/O and FPGA core configuration can occur at the SSBL or OS stage, but is typically configured during the SSBL stage.

Note:

To avoid configuration failures, the Intel Stratix 10 device requires clocks for the PCIe\* and all E-tile transceiver reference clocks. You must provide the input reference clock, refclk, and it must be free-running and stable at device power up for a successful device configuration.

L- and H-tile (does not apply to E-tile)—the refclk requirement is mandatory if you are configuring your Intel Stratix 10 device over a PCIe link; otherwise the refclk requirement is not mandatory for a non PCIe use case.

- For PCIe use case, the firmware waits for the PLL calibration code to ensure the PLL is calibrated properly in order to release the device for entering into user mode. Therefore, refclk is mandatory for PLL calibration.

- For non PCIe use case, without refclk supply during configuration, the firmware does not gate device configuration without a proper PLL calibration code. You can calibrate the XCVR PLL in user mode for XCVR channels to operate properly.

E-tile (does not apply to L- and H-tile)—the refclk requirement is mandatory. E-tile does not support the PCIe use case.

The E-tile refclk is needed to load the firmware (from the FPGA configuration bit stream) into the E-Tile.

#### **Related Information**

- System Layout for HPS Boot First Mode on page 19

- Intel Stratix 10 Configuration User Guide

## 3.1.1. Power-On Reset (POR)

Ensure you power each of the power rails according to the power sequencing consideration until they reach the required voltage levels. In addition, the power-up sequence must meet either the standard or the fast power-on reset (POR) delay time.

#### **Related Information**

- Intel Stratix 10 Device Data Sheet

For information about the POR delay specification

- AN 692: Power Sequencing Considerations for Intel Cyclone<sup>®</sup> 10 GX, Intel Arria<sup>®</sup> 10, Intel Stratix 10, and Intel Agilex<sup>™</sup> Devices

#### 3.1.2. Secure Device Manager

After the Intel Stratix 10 SoC FPGA exits POR, the SDM samples the MSEL[2:0] pins to determine the boot source. Next, the device configures the SDM I/Os according to the selected boot source interface and the SDM retrieves the configuration bitstream through the interface.

Table 6. Available SDM Boot Sources for the Intel Stratix 10 SoC FPGA

| SDM Boot Source              | Details                                                                                                                                                                                                                                           |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Avalon-ST (x8/x16/x32)       | Supported                                                                                                                                                                                                                                         |

| JTAG                         | Supported                                                                                                                                                                                                                                         |

| Active Serial (AS)/ Quad SPI | Supported. SDM only boots in x4 mode for active serial flash and Micron MT25Q flash. Other supported quad SPI flash devices boot in x1 mode. Once the device initialization code loads into the SDM, the SDM can switch these flash into x4 mode. |

The typical configuration bitstream for HPS boot first mode contains:

- SDM configuration firmware

- HPS external memory interface (EMIF) I/O configuration data

- HPS FSBL code and HPS FSBL hardware handoff binary

The SDM completes the configuration of the HPS EMIF I/O and then copies the HPS FSBL to the HPS on-chip RAM.

#### **Related Information**

- System Layout for HPS Boot First Mode on page 19

- Intel Stratix 10 Configuration User Guide

## 3.1.3. First-Stage Bootloader

After the SDM releases the HPS from reset, the FSBL initializes the HPS. Initialization includes configuring clocks, HPS dedicated I/Os, and peripherals.

Note:

In HPS first boot mode, the SDM, HPS OSC and HPS EMIF clocks must be running stable and set at the correct frequency before you begin any part of the configuration sequence.

In HPS first boot mode, phase 1 configuration is successful as long as HPS OSC and HPS EMIF clocks are running stable.

For a generic transceiver use case, if the XCVR ref clock is not running during phase 2 configuration, the phase 2 configuration still succeeds.

For a PCIe use case, if the PCIe ref clock is not running during phase 2 configuration, the configuration fails.

You can create the FSBL from one of the following sources:

- U-Boot secondary program loader (SPL)

- Intel provides the source code for U-Boot on GitHub.

- Arm Trusted Firmware

- Intel provides the source code for the Arm Trusted Firmware on GitHub.

The latest source code is also available on the Intel public git repository.

#### **Related Information**

Creating the Configuration Files on page 23

- U-Boot Source Code on GitHub

- Arm Trusted Firmware Source Code on GitHub

## 3.1.4. Second-Stage Bootloader

The second-stage bootloader (SSBL) is the second boot stage for the HPS. The FSBL initiates the copy of the SSBL to the HPS SDRAM. The SSBL typically enables more advance peripherals such as Ethernet and supports the command line interface.

You can create the HPS SSBL from one of the following sources:

- U-Boot

- Intel provides the source code for U-Boot on GitHub.

- UEFI

- Intel provides the source code for UEFI on GitHub.

- RTOS

- Bare Metal application

You can optionally perform FPGA core and I/O configuration in during the SSBL stage. The SSBL copies the FPGA configuration files from one of the following sources to the HPS SDRAM:

- HPS Flash

- SDM Flash

- External host via the HPS Ethernet (for example, TFTP)

After the SSBL copies the FPGA configuration files to the HPS SDRAM, the SSBL can initiate a configuration request to the SDM to begin the configuration process. Refer to the Configuring the FPGA from SSBL and OS section for more details.

#### **Related Information**

- Configuring the FPGA Fabric from HPS Software on page 55

- UEFI Source Code on GitHub

- U-Boot Source Code on GitHub

- Arm Trusted Firmware Source Code on GitHub

## 3.1.5. Operating System

The SSBL loads the operating system (OS) stage into SDRAM. The OS executes from SDRAM. Depending on your application requirements you may implement a conventional OS or an RTOS.

Intel provides the Golden System Reference Design (GSRD) which includes the Linux kernel and a root filesystem built with Yocto recipes.

#### **Related Information**

Golden System Reference Design and Design Examples on page 53

## 3.1.6. Application

The application that runs on the OS is the last boot stage. The application can also replace the OS stage as a dedicated, Bare Metal runtime code.

## 3.2. System Layout for HPS Boot First Mode

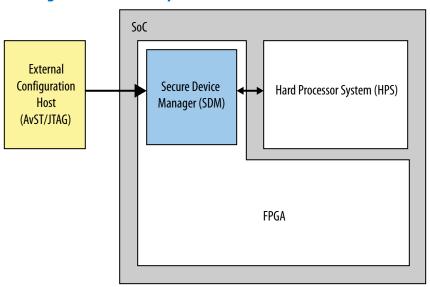

## 3.2.1. External Configuration Host Only

Figure 7. External Configuration Host Only

In this example, the external configuration host (Avalon Streaming or JTAG) provides the SDM a configuration bitstream that consists of the following components:

- SDM configuration firmware

- HPS EMIF I/O configuration data

- HPS FSBL code and HPS FSBL hardware handoff binary

However, because the HPS SSBL or subsequent OS files are not part of the bitstream, the HPS can only boot up to the FSBL stage. This setup is applicable if you are using the FSBL to run simple applications such as Bare Metal applications.

Because the FPGA core is not configured, the FSBL must retrieve the SSBL from external sources, such as the HPS EMAC interface. The U-Boot FSBL source code that Intel provides does not include source code to support SSBL retrieval through the HPS EMAC interface. You must implement the Ethernet software stack in the FSBL separately. Similarly, after the SSBL loads, the SSBL must retrieve the FPGA core and I/O configuration file from an external source as well.

Table 7. Supported Configuration Boot and SSBL Sources

| SDM Configuration Host | SSBL Source  | Details                                                |

|------------------------|--------------|--------------------------------------------------------|

| Avalon streaming       | HPS Ethernet | Not supported in U-Boot FSBL code that Intel provides. |

| JTAG                   |              | triat friter provides.                                 |

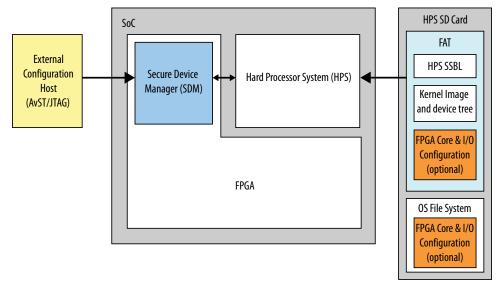

## 3.2.2. External Configuration Host with HPS Flash

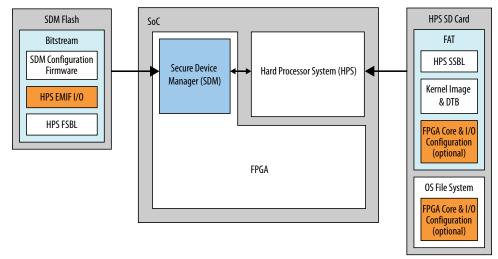

Figure 8. External Configuration Host with HPS Flash

An external configuration host provides an SDM configuration bitstream containing the following components:

- SDM configuration firmware

- HPS EMIF I/O configuration data

- HPS FSBL code and HPS FSBL hardware handoff binary

In this system layout, the HPS flash, contains the HPS SSBL, Linux image device tree information, and the OS file system.

Depending on the boot stage that performs the FPGA configuration, you have the following options for storing the FPGA core and I/O configuration file:

- In the HPS flash partition—The SSBL initiates configuration.

- In the OS file system—The OS initiates configuration

All HPS flash devices are supported:

- SD Card

- eMMC

- NAND

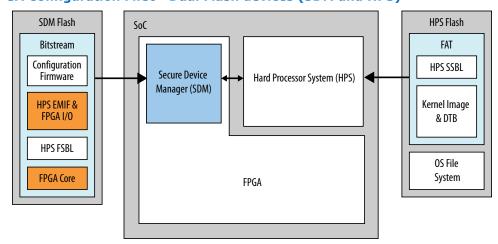

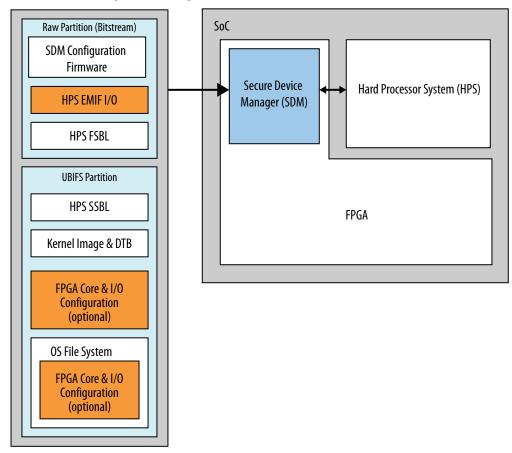

## 3.2.3. Single SDM Flash

In this case, the Quad SPI flash connected to the SDM contains all the data required for configuring and booting the system, including the configuration bitstream, bootloader and OS files.

Note:

When you use the HPS to access the SDM Quad SPI, it operates at a lower bandwidth of  $\sim$ 4-6 MB/s. This is due to the high latency of the PSI link between HPS and SDM, and the fact that all transfers are done in Programmed IO (PIO) mode, instead of DMA mode.

Software running on the HPS must request permission from the SDM to get exclusive access to the QSPI before using it. This is already implemented in the U-Boot and UEFI bootloaders supported by Intel.

Depending on the boot stage that performs the FPGA configuration, you have the following options for storing the FPGA core and I/O configuration file:

- An SDM flash storage partition—In this case the SSBL initiates configuration

- In the OS file system—In this case the OS initiates configuration

Figure 9. HPS Boot First Layout with Quad SPI

#### **Related Information**

- Intel Stratix 10 Hard Processor System Technical Reference Manual For more information, refer to the Booting and Configuration Appendix

- Intel Stratix 10 SoC FPGA First Single QSPI Flash Boot

- Creating the Configuration Files on page 23

- Intel Stratix 10 Hard Processor System Technical Reference Manual

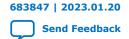

## 3.2.4. HPS Boot First - Dual Flash System

In a dual flash system, the SDM flash such as an active serial flash stores the configuration bitstream. The HPS flash such as an SD card stores the HPS SSBL and the rest of the OS files.

All the HPS flash devices are supported:

- SD Card

- eMMC

- NAND

Depending on the boot stage that performs the FPGA configuration, you have the following options for storing the FPGA core and I/O configuration file:

- In the HPS flash partition—The SSBL initiates configuration.

- In the OS file system—The OS initiates configuration

Figure 10. HPS Boot First - Dual Flash Devices (SDM and HPS)

# 4. Creating the Configuration Files

There are several different configuration methods available:

- Configuration over JTAG

- Configuration from QSPI

- Configuration over AVST

- Configuration via Protocol

- Remote System Update (RSU)

This chapter describes how to create the configuration files for all these configuration methods.

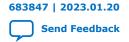

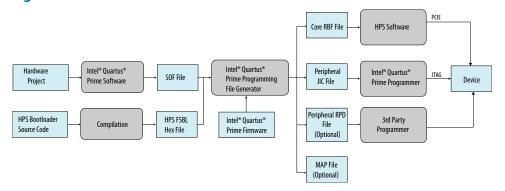

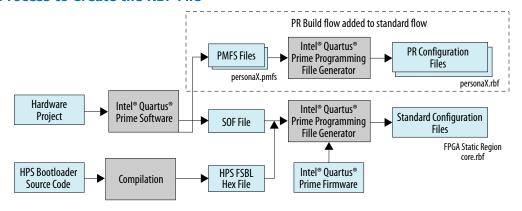

### 4.1. Overview

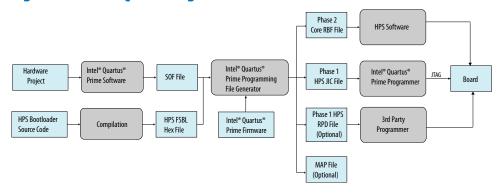

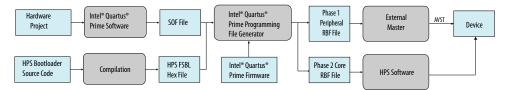

The configuration files are created by the Intel Quartus Prime Programming File Generator, using the following inputs:

- SOF file resulted from compilation of the hardware project in Intel Quartus Prime Software

- HPS First Stage Bootloader (FSBL) hex file resulted from compiling an HPS bootloader

- Intel Quartus Prime Firmware, which ends up running on the SDM

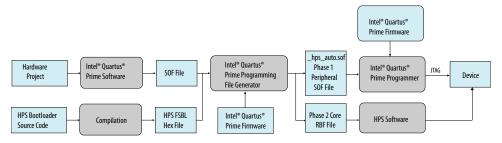

Figure 11. Overview of Configuration File Generation

The resulted configuration files contain the following components which are required for configuring the device:

**Table 8.** Components for Configuring the Device

\*Other names and brands may be claimed as the property of others.

| Source   | Component                      | Description                                    |  |

|----------|--------------------------------|------------------------------------------------|--|

| SOF File | HPS IO Configuration Data      | Used for configuring HPS IOs including HPS DDR |  |

|          | FPGA IO Configuration Data     | Used for configuring FPGA IOs                  |  |

|          | FPGA Fabric Configuration Data | Used for configuring the FPGA fabric           |  |

|          |                                | continued.                                     |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

| Source              | Component                     | Description                                                                                           |

|---------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|

|                     | Handoff Data for SDM Firmware | Used to pass parameters to SDM firmware                                                               |

|                     | Handoff Data for HPS FSBL     | Used to pass parameter to HPS FSBL                                                                    |

| Intel Quartus Prime | SDM Firmware                  | Located at the beginning of configuration bitstream and can be executed as part of the configuration. |

| Your HPS Software   | HPS FSBL                      | First software ran on HPS after SDM takes it out of reset                                             |

## 4.2. Intel Quartus Prime Hardware Project Compilation

There are various settings that need to be provided in Intel Quartus Prime for the hardware project, which impact the device configuration, and HPS booting. This section presents a summary of these options.

## 4.2.1. Device and Pin Options

The device and pin options can be accessed from Intel Quartus Prime, by going to **Assignments** ➤ **Device** ➤ **Device and Pin Options**. The most important options related to configuration and HPS boot are:

- General > Configuration Clock Source : allows using an internal oscillator or an external input clock for configuration purposes.

- Configuration > Configuration Scheme: allows selecting the configuration source:

- Active Serial x4

- AVST x8

- AVST x16

- AVST x32

- Configuration ➤ Active Serial Clock Source: allows selecting the QSPI clock speed when Active Serial x4 mode is selected

- **Configuration** ➤ **Configuration Pin Options**: allows selecting SDM pin behavior for configuration purposes

- Configuration ➤ HPS/FPGA Configuration Order: allows selecting FPGA Configuration First (called After INIT\_DONE) or HPS Boot First (called HPS First) modes.

- Configuration ➤ HPS Debug Access Port (DAP): allows the HPS JTAG port to be connected to HPS Pins, FPGA Pins or Disabled. It is typically connected to SDM pins, so you can have a single JTAG connection covering both SDM and HPS.

- CvP Settings ➤ Configuration via Protocol: can be selected as Initialization and update or Off.

For more information about these options, refer to the *Intel Stratix 10 Configuration User Guide*.

#### **Related Information**

- System Layout for HPS Boot First Mode on page 19

- Intel Stratix 10 Configuration User Guide

683847 | 2023.01.20

## 4.2.2. Platform Designer Options

The HPS component instantiated in Platform Designer has various selectable HPS settings. You can access them by doing the following:

- 1. Open the hardware project in the Intel Quartus Prime GUI.

- 2. In the Intel Quartus Prime GUI, to **Tools ➤ Platform Designer** to open the Platform Designer.

- 3. When asked by Platform Designer, select and open the file instantiating the HPS component.

- 4. In Platform Designer, click the HPS component and access the **Parameters** panel.

The available settings are grouped as follows:

- FPGA Interfaces

- General

- Bridges

- DMA Requests

- Interrupts

- HPS Clocks and Resets

- Input Clocks

- Internal Clocks and Output Clocks

- Resets

- SDRAM

- IO Delays

- Pin Mux and Peripherals

For more information about these settings, refer to the *Intel Stratix 10 HPS Component User Guide*.

#### **Related Information**

Intel Stratix 10 Hard Processor System Component Reference Manual

# 4.3. Bootloader Software Compilation

Intel supports the following bootloaders:

- U-Boot

- UEFI

For more information about the bootloaders, including how to configure and build for the various booting scenarios, refer to the BuildingBootloader web page on RocketBoards.

#### **Related Information**

RocketBoards: BuildingBootloader

## 4.4. Programming File Generator

The tool that is used for creating the configuration files is called Programming File Generator. This tool is part of the Intel Quartus Prime Programmer, which is included with the full Intel Quartus Prime software installation. The Intel Quartus Prime Programmer can also be downloaded and installed separately as a standalone application, in which case less disk space would be required.

The Programming File Generator tool can be called from command line using the quartus\_pfg command, or as a graphical user interface application using qpfgw command. Both command line version and graphical interface version offer the same functionality with a couple of exceptions:

- Adding an HPS FSBL hex file to a SOF file is only supported by the command line version.

- Creating the initial flash contents for a Remote System Update (RSU) system is only supported by the graphical interface version.

The command line version is typically more convenient to use, as it requires less parameters to be entered than the graphical interface version. The graphical interface version also has the capability of saving all the selected options in a .pfg file, by going to **File > Save** or **File > Save As** menus. The saved .pfg file can later be used to re-create the configuration files by running the quartus\_pfg -c filename.pfg command. The .pfg file is an XML file, typically not editable by hand. One useful edit though is to replace absolute filenames with relative ones, so that the tool could be ran in a different folder than the one where the .pfg file was originally created.

The following table summarizes the file types handled by the Intel Quartus Prime Programming File Generator:

Table 9. Intel Quartus Prime Programming File Generator File Types

| File<br>Extension | File Type                           | Description                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .jic              | JTAG Indirect<br>Configuration File | These files are intended to be written to QSPI flash by using the Intel Quartus Prime Programmer tool. They contain the actual flash data, and also a flash loader, which is a small FPGA design used by the Intel Quartus Prime Programmer to write the data.                                                                                                 |

| .rpd              | Raw Programming<br>Data File        | These files contain actual binary content for the flash and no additional metadata. They can contain the full content of the flash, similar with the <code>.jic</code> file—this is typically used in the case where an external tool is used to program the initial flash image. They can also contain an RSU application image, or RSU factory update image. |

| .rbf              | Raw Binary File                     | These files are binary files which can be used typically to configure the FPGA fabric for HPS configuration first mode. They can also be used for passively configuring the FPGA device through Avalon Streaming Interface. They are also used for configuring the FPGA fabric for CvP case.                                                                   |

|                   |                                     | The maximum size of the .core.rbf file for the FPGA core fabric from the HPS does not exceed the bit-stream size for the FPGA from a configuration device.  The maximum size of bit-stream can be found in the Configuration Bit Stream Sizes section in the Intel Stratix 10 Device Data Sheet.                                                               |

| .map              | Memory Map File                     | These files contain details about where the input data was placed in the output file. This file is human readable.                                                                                                                                                                                                                                             |

#### **Related Information**

Intel Stratix 10 Device Data Sheet

683847 | 2023.01.20

## 4.5. Configuration over JTAG

In this case, the configuration bitstream is sent to the device over JTAG with the help of the Intel Quartus Prime Programmer.

## 4.5.1. FPGA Configuration First

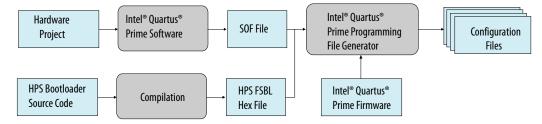

The following figure shows an overview of the process:

Figure 12. Configuration over JTAG with FPGA Configuration First

The following steps are involved:

- 1. Compile hardware project with Intel Quartus Prime to obtain the SOF file.

- 2. Compile the HPS FSBL source code to obtain the HPS FSBL hex file or use a precompiled HPS FSBL hex file.

- 3. Add the HPS FSBL hex file to the SOF file to obtain the HPS SOF File. SOF files resulted from compiling hardware designs that have HPS instantiated cannot be used directly to configure the device.

- 4. Use the Intel Quartus Prime Programmer to configure the device over JTAG with the resulted HPS SOF file. The required firmware to run on the SDM must be downloaded on the device by the Intel Quartus Prime Programmer.

Run the following command to add the HPS FSBL hex file to the SOF file to create the HPS SOF file:

```

quartus_pfg -c design.sof design_hps.sof -o hps_path=fsbl.hex

```

The input and output files for this command are:

- Input Files:

- design.sof

- fsbl.hex

- Output File:

- design hps.sof

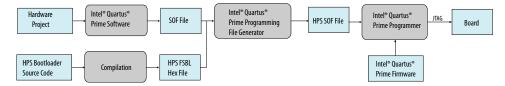

#### 4.5.2. HPS Boots First

In order to obtain the SOF file to be used to configure the device through JTAG with the HPS Boots First option, you need to generate a bitstream intended for another configuration method, such as AVST. An SOF file called design\_hps\_auto.sof is expected to be created automatically, and it can be used to configure the device. You discard or ignore the Phase 1 AVST bitstream, and use the Phase 2 bitstream to later configure the FPGA fabric from HPS software.

The following figure shows an overview of the process:

Figure 13. Configuration over JTAG with HPS Boots First

The following steps are involved:

- 1. Compile hardware project with Intel Quartus Prime to obtain the SOF file.

- 2. Compile the HPS FSBL source code to obtain the HPS FSBL hex file, or use a precompiled one.

- 3. Use Programming File Generator to create the following files:

- Raw Binary File (RBF): contains the small phase 1 configuration bitstream.

Discard this file.

- hps\_auto SOF File: contains the phase 1 configuration data, and the HPS FSBL.

- Core RBF File: contains the typically much larger phase 2 configuration bitstream. To be used by HPS software later to configure the fabric.

- 4. Use Intel Quartus Prime Programmer to configure the device using the phase 1 hps\_auto SOF file. HPS software starts running, beginning with HPS FSBL.

- 5. At a later time, HPS software configures the FPGA fabric by using the phase 2 Core RBF bitstream.

The following example creates the files for HPS boot first:

```

quartus_pfg -c design.sof design.rbf -o hps_path=fsbl.hex -o hps=on

```

The input and output files for this command are:

- Input Files:

- design.sof

- fsbl.hex

- Output Files:

- design.hps.rbf—to be discarded

- design hps.auto.sof-Phase 1 SOF

- design.core.rbf—Phase 2 Core RBF

# 4.6. Configuration from QSPI

The device configures itself with the bitstream which it reads from QSPI flash. This configuration method is also called "Active Serial x4" or "ASx4".

683847 | 2023.01.20

## 4.6.1. Supported QSPI Devices

For the list of supported QSPI devices, refer to the Intel Supported Configuration Devices web page.

## 4.6.2. FPGA Configuration First

The following figure shows an overview of configuring from QSPI when using FPGA configuration first:

#### Figure 14. Configuration from QSPI using FPGA Configuration First

The following steps are involved:

- 1. Compile hardware project with Intel Quartus Prime to obtain the SOF file.

- 2. Compile the HPS FSBL source code to obtain the HPS FSBL hex file or use a precompiled one.

- 3. Use Programming File Generator to create the following files:

- JTAG Indirect Configuration (JIC) File: contains the configuration bitstream to be written to flash and SDM helper image used by the Intel Quartus Prime Programmer to write the bitstream to flash.

- [Optional] Raw Programming Data (RPD) File: contains the configuration bitstream in plain binary format. Can be written to flash with a 3rd party programmer, such as U-Boot.

- [Optional] Map File: describes the actual flash usage in human-readable text format.

- 4. Use the Intel Quartus Prime Programmer to write the JIC image to QSPI flash. Alternatively, use a 3rd party programmer to write the RPD image to flash.

- 5. Set MSEL to QSPI, then power up, power cycle or toggle nCONFIG to cause the device to configure itself from QSPI.

- 6. FPGA device is configured, and after INIT DONE the HPS FSBL is also executed.

#### 4.6.2.1. Creating Configuration Files from Command Line

The following example command creates the QSPI configuration files for FPGA configuration first mode:

```

quartus_pfg -c design.sof design.jic design.rpd design.map \

-o hps_path=fsbl.hex \

-o device=MT25QU128 \

-o flash_loader=1SX280LU2 \

-o mode=ASX4 \

-o bitswap=on

```

The input and output files for this command are:

- Input Files:

- design.sof

- fsbl.hex

- Output Files:

- design.jic

- design.rpd

- design.map

The command parameters are listed below:

#### **Table 10.** Command Parameters

| Parameter    | Description                                                                                                                                                                 |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| hps_path     | Location of HPS FSBL file in hex format                                                                                                                                     |  |

| device       | Target QSPI device. Use a device listed in <i>Supported QSPI Devices</i> or use the graphical interface to determine available options.                                     |  |

| flash_loader | Which helper image to be used for writing JIC to flash. It is typically a prefix of your FPGA part number. Use the graphical interface mode to determine available options. |  |

| mode         | ASX4 for QSPI                                                                                                                                                               |  |

| bitswap      | Set to "on" to create RPD with plain binary format, usable by 3rd party tools.                                                                                              |  |

#### Note:

If your design is small, you can target a QSPI device that is smaller than what you have on board. When programming the resulted JIC file, a warning is displayed, but the resulted file size and erasing and programming times are reduced accordingly.

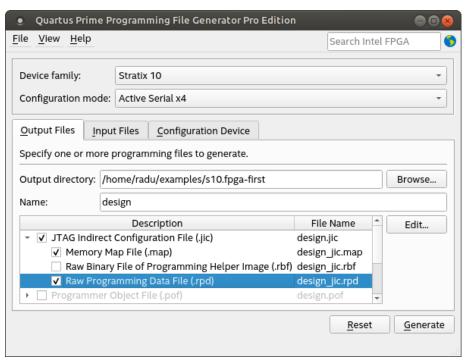

## 4.6.2.2. Creating Configuration Files Using Graphical Interface

The following example creates the QSPI configuration files for FPGA configuration first mode using the Programming File Generator in GUI mode:

- Start the Programming File Generator in GUI mode by running the qpfgw command.

- 2. Select the **Device Family** to be Intel Stratix 10.

- 3. Select the Configuration mode to be Active Serial x4.

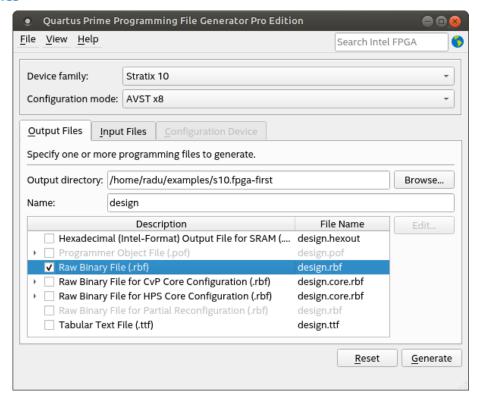

- 4. In the **Output Files** tab:

- a. Change the output file Name to "design"

- b. Check JTAG Indirect Configuration File (.jic) option the others are grayed out.

- c. Optionally check the Memory Map File (.map) sub-option

- d. Optionally check the **Raw Programming Data (.rpd)** sub-option.

- e. Click the **Raw Programming Data (.rpd)** sub-option (if checked above) then click on **Edit** button and select the **Bit swap** option to be "on". This ensures the file uses the natural byte format that can be used by 3rd party tools like U-Boot.

Figure 15. Intel Quartus Prime Programming File Generator Pro Edition Window: Output Files

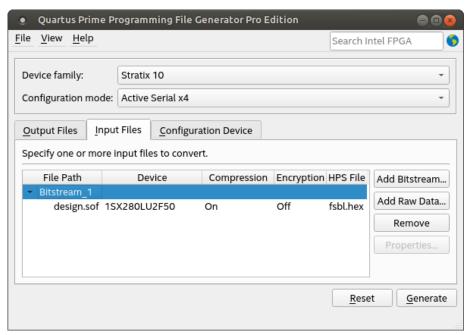

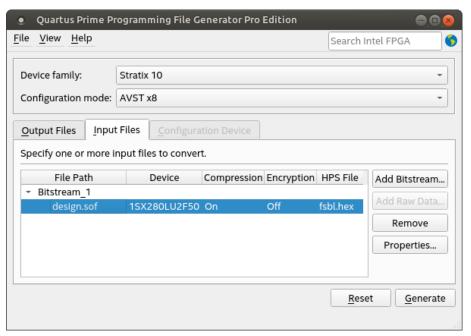

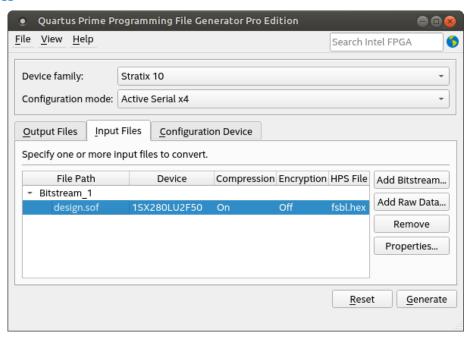

- 5. Switch to **Input Files** tab by clicking it. In the **Input Files** tab, do the following:

- a. Click the Add Bitstream button, browse to your SOF file, then click Open.

- b. Click the newly added design.sof file, then click Properties. In the HPS settings ➤ Bootloader section, click the ".." browse button, go to the location of your HPS FSBL hex file, select it and click Open.

Figure 16. Intel Quartus Prime Programming File Generator Pro Edition Window: Input Files

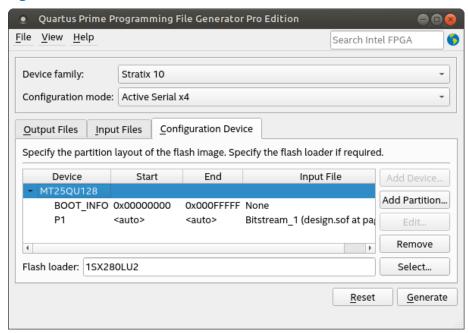

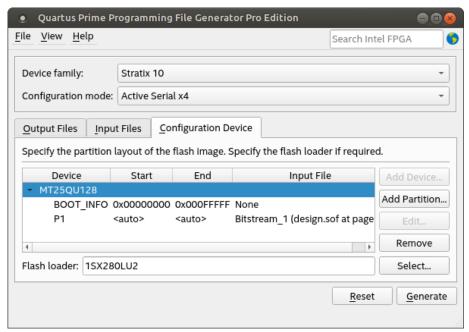

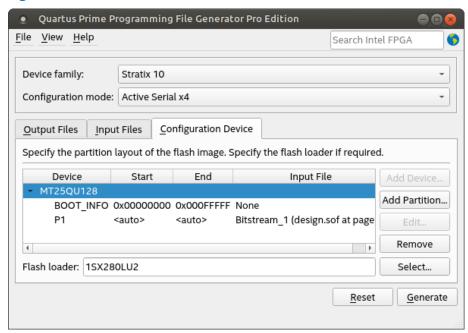

- 6. Switch to the **Configuration Device** tab by clicking it. In the **Configuration Device** tab, do the following:

- a. Click **Add device**, select your desired flash device (in this example MT250U128) then click **OK**

- b. Click the newly added device, then click **Add Partition**. In the partition window, leave **Name** as "P1", **select Input file** to be "Bitstream\_1 (design.sof)" and leave **Page** as "0", **Address Mode** as "Auto", then click **OK**.

- c. Under Flash Loader, click the Select.. button, then select Intel Stratix 10 under Device Family, and 1SX280LU2 under Device Name. Click OK.

Figure 17. Intel Quartus Prime Programming File Generator Pro Edition Window: Configuration Device

- Click the **Generate** button. Once the files are generated, a confirmation message is received.

- 8. Optionally, go to **File > Save** or **File > Save As** to save the configuration in a .pfg file. You can generate the output again by applying the same options by running the command line version of the tool like this: "quartus\_pfg -c <filename.pfg>".

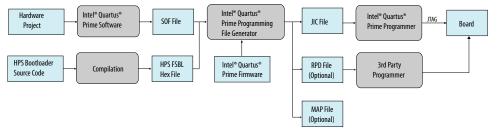

#### 4.6.3. HPS Boot First

In this case, the device reads a small phase 1 bitstream from QSPI flash and uses it to configure the HPS IO, HPS DDR, and bring up the HPS software. Then later the HPS software can configure the FPGA fabric using the typically much larger phase 2 configuration bitstream. The following figure shows an overview of the process:

Figure 18. Configuration from QSPI using HPS Boot First

The following steps are involved:

- 1. Compile hardware project with Intel Quartus Prime to obtain the SOF file.

- Compile the HPS FSBL source code to obtain the HPS FSBL hex file, or use a precompiled one.

- 3. Use Programming File Generator to create the following files:

- HPS JTAG Indirect Configuration (JIC) file: contains the small phase 1 configuration bitstream and a small SDM helper firmware image used by the Intel Quartus Prime Programmer to write the bitstream to flash.

- [Optional] HPS Raw Programming Data (RPD) File: contains the small phase 1 configuration bitstream in simple binary format. Can be written to flash with a 3rd party programmer, such as U-Boot.

- Core RBF file: contains the phase 2 configuration bitstream, to be used by HPS software to configure the FPGA fabric.

- [Optional] Map file: describes the flash placement and usage in humanreadable text format.

- 4. Use the Intel Quartus Prime Programmer to write the JIC image to QSPI flash. Alternatively use a 3rd party programmer to write the RPD image to flash.

- 5. Set MSEL to QSPI, then power up, power cycle or toggle nCONFIG to cause the device to configure itself from QSPI.

- 6. HPS software starts running, beginning with HPS FSBL.

- Later HPS software configures the FPGA fabric by using the phase 2 Core RBF bitstream.

Note:

The phase 1 and phase 2 configuration bitstreams must be created by the exact same Intel Quartus Prime Programming File Generator version, including the same firmware patches. Also, the phase 1 and phase 2 configuration bitstreams must have the same HPS IO settings, including the HPS DDR settings. If these conditions are not both met, the phase 2 configuration fails.

#### 4.6.3.1. Creating Configuration Files from Command Line

The following example creates the QSPI configuration files for HPS boot first mode:

```

quartus_pfg -c design.sof design.jic design.rpd design.map \

-o hps_path=fsbl.hex \

-o device=MT25QU128 \

-o flash_loader=1SX280LU2 \

-o mode=ASX4 \

-o hps=on \

-o bitswap=on

```

The input and output files for this command are:

- Input Files:

- design.sof

- fsbl.hex

- Output Files:

- design.hps.jic

- design.core.rbf

- design.rpd (optional)

- design.map (optional)

The command parameters are listed below:

#### **Table 11. Command Parameters**

| Parameter    | Description                                                                                                                                                                 |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| hps_path     | Location of HPS FSBL file in hex format                                                                                                                                     |  |

| device       | Target QSPI device. Use a device listed in <i>Supported QSPI Devices</i> or use the graphical interface to determine available options.                                     |  |

| flash_loader | Which helper image to be used for writing JIC to flash. It is typically a prefix of your FPGA part number. Use the graphical interface mode to determine available options. |  |

| mode         | ASX4 for QSPI                                                                                                                                                               |  |

| bitswap      | Set to "on" to create RPD with plain binary format, usable by 3rd party tools.                                                                                              |  |

| hps          | Set to "on" to enable HPS boot first mode, omit for FPGA configuration first mode                                                                                           |  |

Note:

When using HPS boot first your JIC is small, and you can target a QSPI device that is smaller than what you have on board. When programming the resulted JIC file, a warning is displayed, but the resulted file size and erasing and programming times are reduced accordingly.

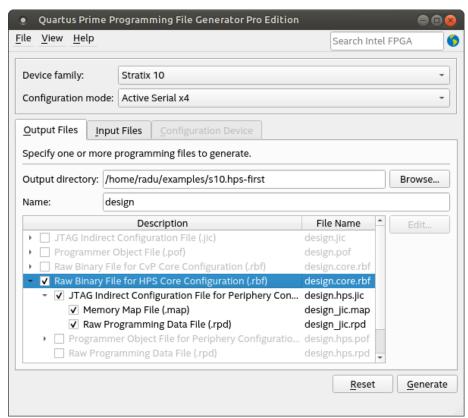

## 4.6.3.2. Creating Configuration Files Using Graphical Interface

The following example creates the QSPI configuration files for HPS boot first mode using the Programming File Generator in GUI mode:

- Start the Programming File Generator in GUI mode by running the qpfgw command.

- 2. Select the **Device Family** to be Intel Stratix 10.

- 3. Select the Configuration mode to be Active Serial x4.

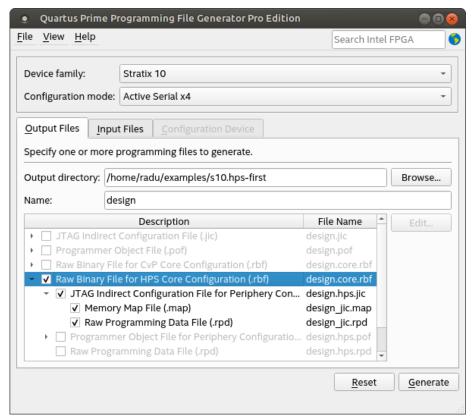

- 4. In the **Output Files** tab:

- a. Change the output file Name to "design".

- Check Raw Binary File for HPS Core Configuration (.rbf) option the others are grayed out.

- c. Check the JTAG Indirect Configuration File for Periphery Configuration (.jic) sub-option

- d. Optionally check the Memory Map File (.map) sub-option

- e. Optionally check the Raw Programming Data (.rpd) sub-option.

- f. Click the Raw Programming Data (.rpd) sub-option (if checked above) then click on Edit button and select the Bit swap option to be "on". This ensures the file uses the natural byte format that can be used by 3rd party tools like U-Boot.

The Intel Quartus Prime Programming File Generator window is displayed:

Figure 19. Intel Quartus Prime Programming File Generator Pro Edition Window: Output Files

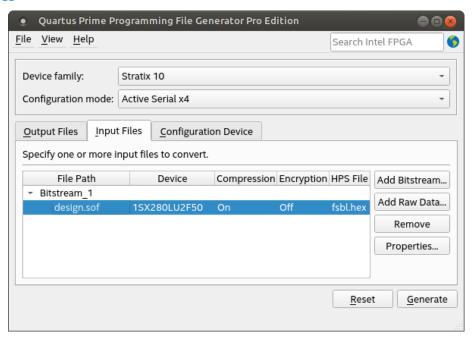

- 5. Switch to **Input Files** tab by clicking it. In the **Input Files** tab, do the following:

- a. Click the Add Bitstream button, browse to your SOF file, then click Open.

- b. Click the newly added design.sof file, then click Properties. In the HPS settings ➤ Bootloader section, click the ".." browse button, go to the location of your HPS FSBL hex file, select it and click Open.

Figure 20. Intel Quartus Prime Programming File Generator Pro Edition Window: Input Files

- 6. Switch to the **Configuration Device** tab by clicking it. In the **Configuration Device** tab, do the following:

- a. Click Add device, select your desired flash device (in this example MT250U128) then click OK

- b. Click the newly added device, then click **Add Partition**. In the partition window, leave **Name** as "P1", **select Input file** to be "Bitstream\_1 (design.sof)" and leave **Page** as "0", **Address Mode** as "Auto", then click **OK**.

- c. Under Flash Loader, click the Select.. button, then select Intel Stratix 10 under Device Family, and 1SX280LU2 under Device Name. Click OK.

Figure 21. Intel Quartus Prime Programming File Generator Pro Edition Window: Configuration Device

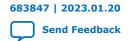

- Click the **Generate** button. Once the files are generated, a confirmation message is received.

- 8. Optionally, go to **File > Save** or **File > Save As** to save the configuration in a .pfg file. You can generate the output again by applying the same options by running the command line version of the tool like this: "quartus\_pfg -c <filename.pfg>".

### 4.7. Configuration over AVST

An external master sends the configuration data to the device over an Avalon Streaming Interface bus. There are three different supported widths for the Avalon Streaming Interface bus: AVST x8, AVST x16 and AVST x32.

Note:

On Configuration over AVST, the QSPI access from the HPS software is not supported and the QSPI component must be disabled in both the bootloader (for example: U-Boot configuration and device tree) and the OS (for example: Linux device tree).

# 4.7.1. FPGA Configuration First

The following figure shows an overview of the process:

Figure 22. Configuration over Avalon Streaming Using FPGA Configuration First

683847 | 2023.01.20

The following steps are involved:

- 1. Compile hardware project with Intel Quartus Prime to obtain the SOF file.

- 2. Compile the HPS FSBL source code to obtain the HPS FSBL hex file, or use a precompiled file.

- Use Programming File Generator to create the following files:

Raw Binary File (RBF): contains the configuration bitstream in binary format.

- 4. Set MSEL to the AVST mode.

- 5. Power up, power cycle or toggle nCONFIG on the device.

- 6. Use an external master connected over AVST to configure the device using the RBF File.

### 4.7.1.1. Creating Configuration Files from Command Line

The following example creates the RBF file for FPGA configuration first:

```

quartus_pfg -c design.sof design.rbf -o hps_path=fsbl.hex

```

The input and output files for this command are:

- Input Files:

- design.sof

- fsbl.hex

- Output File:

- design.rbf

The command parameter is listed below:

### **Table 12. Command Parameters**

| Parameter                                        | Description |

|--------------------------------------------------|-------------|

| hps_path Location of HPS FSBL file in hex format |             |

### 4.7.1.2. Creating Configuration Files Using Graphical Interface

The following example creates the AVST configuration files for FPGA first mode using the Programming File Generator in GUI mode:

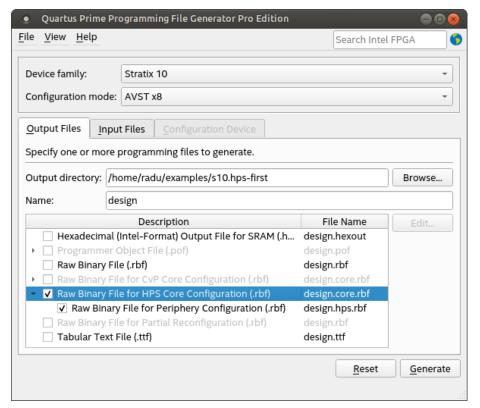

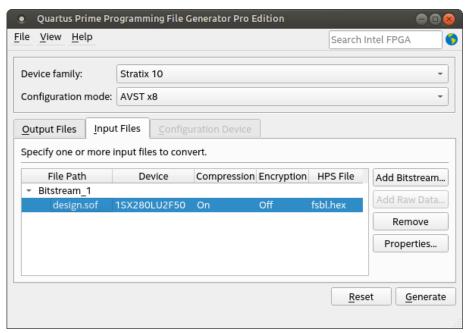

- Start the Programming File Generator in GUI mode by running the qpfgw command.