# HC32F120 系列

32 位 ARM® Cortex®-M0+ 微控制器

参考手册

### 声明

- ➤ 小华半导体有限公司(以下简称: "XHSC")保留随时更改、更正、增强、修改小华半导体产品和/或本文档的权利,恕不另行通知。用户可在下单前获取最新相关信息。XHSC产品依据购销基本合同中载明的销售条款和条件进行销售。

- ➤ 客户应针对您的应用选择合适的 XHSC 产品,并设计、验证和测试您的应用,以确保您的应用满足相应标准以及任何安全、安保或其它要求。客户应对此独自承担全部责任。

- > XHSC 在此确认未以明示或暗示方式授予任何知识产权许可。

- ▶ XHSC 产品的转售,若其条款与此处规定不同,XHSC 对此类产品的任何保修承诺无效。

- ➤ 任何带有"®"或"TM"标识的图形或字样是 XHSC 的商标。所有其他在 XHSC 产品上显示的 产品或服务名称均为其各自所有者的财产。

- ▶ 本通知中的信息取代并替换先前版本中的信息。

©2022 小华半导体有限公司 - 保留所有权利

# 目 录

| 声  | 明2   |          |                            |    |  |  |

|----|------|----------|----------------------------|----|--|--|

| 目  | 录    |          |                            |    |  |  |

| 简介 | か(Ov | verview) |                            | 19 |  |  |

| 1  | 存储   | 器映射      | (Memory Mapping)           | 20 |  |  |

|    | 1.1  | 存储       | 背器映射                       | 20 |  |  |

|    | 1.2  | 位段       | 당空间                        | 22 |  |  |

| 2  | 总线   | 架构(B     | BUS)                       | 24 |  |  |

|    | 2.1  | 概述       | <u> </u>                   | 24 |  |  |

|    | 2.2  | 总线       | è架构                        | 24 |  |  |

|    | 2.3  | 总线       | 讨能                         | 25 |  |  |

| 3  | 复位   | 控制(R     | <b>CMU</b> )               | 26 |  |  |

|    | 3.1  | 简介       | `                          | 26 |  |  |

|    | 3.2  |          | Z方式和复位标志位                  |    |  |  |

|    | 3.3  | 复位       | 过时序                        | 29 |  |  |

|    |      | 3.3.1    | 上电复位                       | 29 |  |  |

|    |      | 3.3.2    | RESET 引脚复位                 | 30 |  |  |

|    |      | 3.3.3    | 低电压检测复位                    |    |  |  |

|    |      | 3.3.4    | 专用看门狗复位                    | 31 |  |  |

|    |      | 3.3.5    | 软件复位                       | 31 |  |  |

|    |      | 3.3.6    | RAM 奇偶校验复位                 |    |  |  |

|    |      | 3.3.7    | M0+ Lockup 复位              |    |  |  |

|    |      | 3.3.8    | 外部高速振荡器异常停振复位              |    |  |  |

|    |      | 3.3.9    | 复位方式的判断                    |    |  |  |

|    | 3.4  | 寄存       | 7器说明                       |    |  |  |

|    |      | 3.4.1    | 复位标志寄存器 0(RMU_RSTF0)       |    |  |  |

| 4  | 时钟   |          | (CMU)                      |    |  |  |

|    | 4.1  |          | `                          |    |  |  |

|    | 4.2  |          | 在图                         |    |  |  |

|    |      | 4.2.1    | 系统框图                       |    |  |  |

|    | 4.3  |          | 中源规格                       |    |  |  |

|    | 4.4  |          | 三时钟规格                      |    |  |  |

|    | 4.5  |          | 長电路                        |    |  |  |

|    |      | 4.5.1    | 外部高速振荡器                    |    |  |  |

|    |      |          | .5.1.1 振荡器模式               |    |  |  |

|    |      |          | .5.1.2 时钟输入模式              |    |  |  |

|    |      | 4.5.2    | 外部高速振荡器故障检测                |    |  |  |

|    |      |          | .5.2.1 检测到 XTAL 故障检测动作     |    |  |  |

|    | 4.6  |          | .5.2.2 检测到 XTAL 振荡故障产生中断复位 |    |  |  |

|    | 4.6  |          | 『RC 时钟                     |    |  |  |

|    |      | 4.6.1    | HRC 时钟                     | 45 |  |  |

|   |     | 4.6.2  | LRC 时钟                            | 46 |

|---|-----|--------|-----------------------------------|----|

|   | 4.7 | 时钟台    | 切换步骤                              | 46 |

|   |     | 4.7.1  | 时钟源切换                             | 47 |

|   | 4.8 | 时钟轴    | 输出功能                              | 48 |

|   | 4.9 | 寄存品    | 器说明                               | 49 |

|   |     | 4.9.1  | CMU XTAL 配置寄存器器(CMU_XTALCFGR)     | 50 |

|   |     | 4.9.2  | CMU XTAL 配置寄存器器(CMU_XTALSTBCR)    | 50 |

|   |     | 4.9.3  | CMU XTAL 控制寄存器(CMU_XTALCR)        | 51 |

|   |     | 4.9.4  | CMU XTAL 振荡故障控制寄存器(CMU_XTALSTDCR) | 51 |

|   |     | 4.9.5  | CMU XTAL 振荡故障状态寄存器(CMU_XTALSTDSR) | 52 |

|   |     | 4.9.6  | CMU HRC 控制寄存器(CMU_HRCCR)          | 53 |

|   |     | 4.9.7  | CMU HRC 频率配置寄存器(CMU_HRCCFGR)      | 53 |

|   |     | 4.9.8  | CMU LRC 控制寄存器(CMU_LRCCR)          | 54 |

|   |     | 4.9.9  | CMU 时钟源稳定状态器(CMU_OSCSTBSR)        | 54 |

|   |     | 4.9.10 | CMU 系统时钟源切换寄存器(CMU_CKSWR)         | 55 |

|   |     | 4.9.11 | CMU 时钟分频配置存器(CMU_SCKDIVR)         | 55 |

|   |     | 4.9.12 | CMU AD 时钟配置存器(CMU_PERICKSEL)      | 56 |

|   |     | 4.9.13 | CMU 功能时钟控制寄存器(CMU_FCG)            | 57 |

|   |     | 4.9.14 | CMU MCO1 配置存器(CMU_MCO1CFGR)       | 59 |

| 5 | 电源  | 控制(PV  | WC)                               | 60 |

|   | 5.1 | 简介     |                                   | 60 |

|   | 5.2 | 电源绘    | 分布                                | 61 |

|   | 5.3 | 低电点    | 压检测单元(LVD)说明                      | 62 |

|   |     | 5.3.1  | 上电复位/掉电复位动作说明                     | 62 |

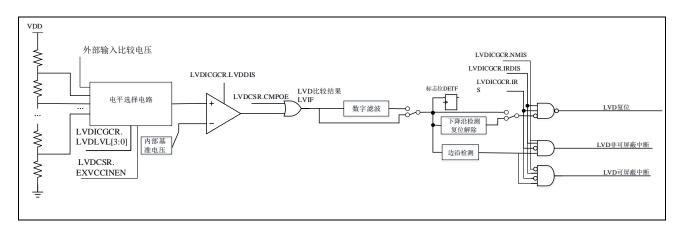

|   |     | 5.3.2  | 低电压检测(LVD)                        | 63 |

|   |     | 5.3.3  | LVD 中断/复位框图                       | 65 |

|   |     | 5.3.4  | 输入/输出引脚                           | 65 |

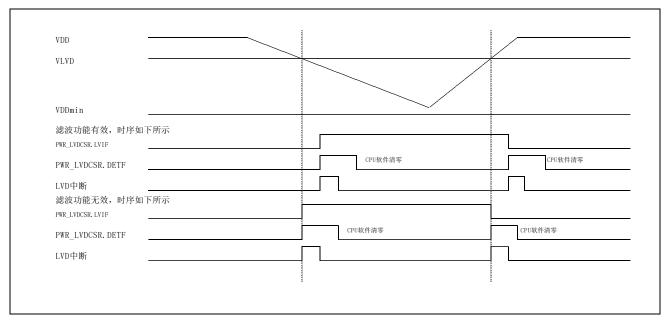

|   |     | 5.3.5  | LVD 中断和复位                         | 66 |

|   | 5.4 | 动作构    | 模式与低功耗模式                          | 67 |

|   |     | 5.4.1  | 运行模式                              | 69 |

|   |     | 5.4.2  | 睡眠模式                              | 70 |

|   |     | 5.4.3  | 停止模式                              | 71 |

|   | 5.5 | 降低。    | 功耗的方法                             | 73 |

|   |     | 5.5.1  | 降低系统时钟速度                          |    |

|   |     | 5.5.2  | 关闭不使用的时钟源                         |    |

|   |     | 5.5.3  | 功能时钟停止                            |    |

|   | 5.6 | 寄存品    | 器保护功能                             | 74 |

|   | 5.7 | 寄存品    | 器说明                               | 75 |

|   |     | 5.7.1  | 停止模式控制寄存器(PWR_STPMCR)             | 76 |

|   |     | 5.7.2  | 电源模式控制寄存器(PWR_PWRC)               | 77 |

|   |     | 5.7.3  | RAM 保护寄存器(PWR_RAMCR)              | 78 |

|   |     | 5.7.4  | 功能保护控制寄存器(PWR FPRC)               | 79 |

|   |     | 5.7.5    | LVD ICG 控制寄存器 (PWR_LVDICGCR) | 80  |

|---|-----|----------|------------------------------|-----|

|   |     | 5.7.6    | LVD 控制状态寄存器 (PWR_LVDCSR)     | 82  |

|   |     | 5.7.7    | 调试模式控制寄存器(PWR_DBGC)          | 83  |

| 6 | 初始  | 化配置(I    | ICG)                         | 84  |

|   | 6.1 | 简介.      |                              | 84  |

|   | 6.2 | 寄存器      | 器说明                          | 85  |

|   |     | 6.2.1    | 初始化配置寄存器 0(ICG0)             | 85  |

|   |     | 6.2.2    | 初始化配置寄存器 1(ICG1)             | 88  |

|   |     | 6.2.3    | 初始化配置寄存器 n(ICGn)n=2~6        | 90  |

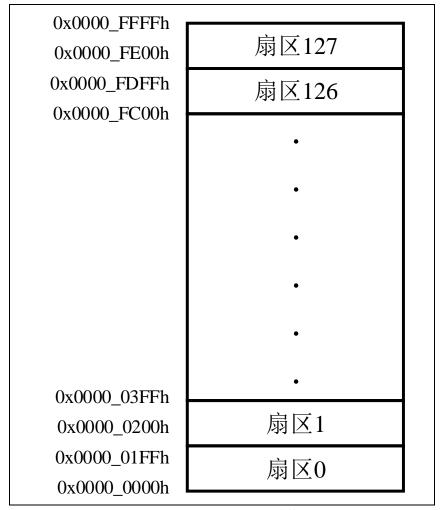

| 7 | 嵌入  | 式 FLASH  | I (EFM)                      | 91  |

|   | 7.1 | 简介.      |                              | 91  |

|   | 7.2 | 主要特      | 寺性                           | 91  |

|   | 7.3 | 嵌入式      | 式 FLASH                      | 92  |

|   | 7.4 | 读接口      | □                            | 93  |

|   |     | 7.4.1    | CPU 时钟和 FLASH 读取时间之间的关系      | 93  |

|   | 7.5 | FLAS     | H 读预取                        | 94  |

|   | 7.6 | FLAS     | H 编程和擦除操作                    | 94  |

|   |     | 7.6.1    | 单次编程无回读模式                    | 94  |

|   |     | 7.6.2    | 单编程回读模式                      | 94  |

|   |     | 7.6.3    | 连续编程操作                       | 95  |

|   |     | 7.6.4    | 擦除操作                         | 95  |

|   |     | 7.6.5    | 总线保持功能                       | 96  |

|   |     | 7.6.6    | FLASH 擦除、编程窗口保护              | 96  |

|   |     | 7.6.7    | 中断                           | 97  |

|   | 7.7 | 寄存署      | 器说明                          | 98  |

|   |     | 7.7.1    | 访问保护寄存器 EFM_FAPRT            | 99  |

|   |     | 7.7.2    | FLASH 停止寄存器 EFM_FSTP         | 99  |

|   |     | 7.7.3    | 读模式寄存器 EFM_FRMC              | 100 |

|   |     | 7.7.4    | 擦写模式寄存器 EFM_FWMC             |     |

|   |     | 7.7.5    | 状态寄存器 EFM_FSR                | 102 |

|   |     | 7.7.6    | 状态清除寄存器 EFM_FSCLR            | 103 |

|   |     | 7.7.7    | 中断许可寄存器 EFM_FITE             | 104 |

|   |     | 7.7.8    | FLASH 窗口保护起始地址寄存器 EFM_FPMTSW | 104 |

|   |     | 7.7.9    | FLASH 窗口保护结束地址寄存器 EFM_FPMTEW | 105 |

|   |     | 7.7.10   | UNIQUE ID 寄存器 EFM_UQID 0     | 105 |

|   |     | 7.7.11   | UNIQUE ID 寄存器 EFM_UQID 1     | 106 |

|   |     | 7.7.12   | UNIQUE ID 寄存器 EFM_UQID 2     | 106 |

|   | 7.8 | 注意       | 事项                           | 107 |

| 8 | 内置  | SRAM (S  | SRAM)                        | 108 |

|   | 8.1 | 简介.      |                              | 108 |

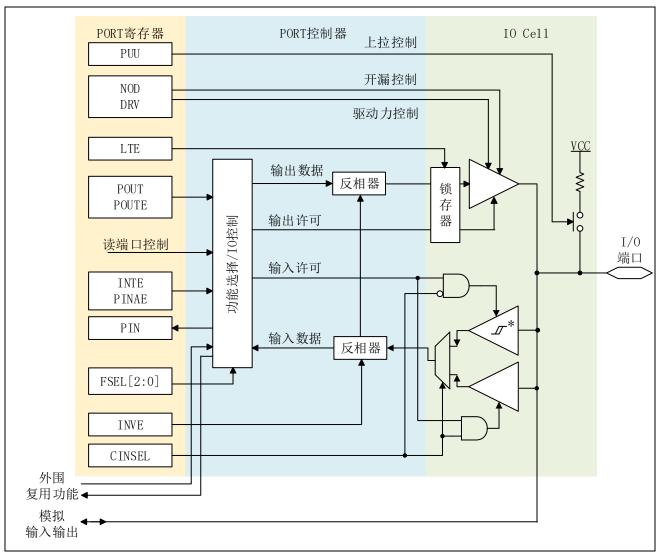

| 9 | 通用  | IO (GPIC | O)                           | 109 |

|   | 0.1 | 符介       |                              | 100 |

|    | 9.2  | 2 端口功能概要 |                       | 110 |

|----|------|----------|-----------------------|-----|

|    | 9.3  | 动作说      | 兑明                    | 111 |

|    |      | 9.3.1    | 通用输入输出 GPIO 功能        | 111 |

|    |      | 9.3.2    | 外围功能                  | 112 |

|    |      | 9.3.3    | 外部中断 EIRQ 输入功能        | 112 |

|    |      | 9.3.4    | 模拟功能                  | 112 |

|    |      | 9.3.5    | 通用控制                  | 112 |

|    | 9.4  | 寄存器      | <b>晕说明</b>            | 114 |

|    |      | 9.4.1    | 通用输入寄存器(PIDRx)        | 115 |

|    |      | 9.4.2    | 通用输出数据寄存器(PODRx)      | 115 |

|    |      | 9.4.3    | 通用输出许可寄存器(POERx)      | 116 |

|    |      | 9.4.4    | 通用输出置位寄存器(POSRx)      | 116 |

|    |      | 9.4.5    | 通用输出复位寄存器(PORRx)      | 117 |

|    |      | 9.4.6    | 通用输出翻转寄存器(POTRx)      | 117 |

|    |      | 9.4.7    | 通用控制寄存器(PCRxy)        | 118 |

|    |      | 9.4.8    | 特殊控制寄存器(PSPCR)        | 120 |

|    |      | 9.4.9    | 公共控制寄存器(PCCR)         | 120 |

|    |      | 9.4.10   | 输入控制寄存器(PINAER)       | 121 |

|    |      | 9.4.11   | 写保护寄存器(PWPR)          | 122 |

|    |      | 9.4.12   | 访问位宽                  | 122 |

|    | 9.5  | 注意事      | <b>F项</b>             | 123 |

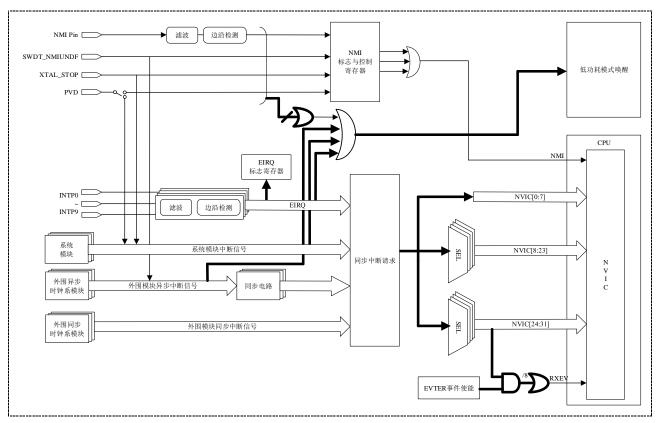

| 10 | 中断排  | 空制器(I    | NTC)                  | 124 |

|    | 10.1 | 简介       |                       | 124 |

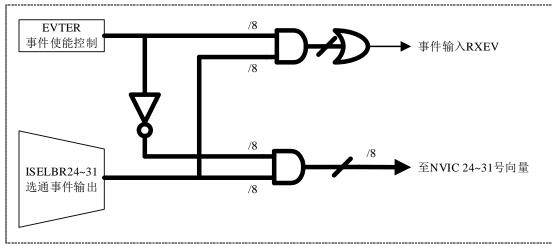

|    | 10.2 | INTC     | 系统框图                  | 126 |

|    |      | 10.2.1   | 系统框图                  | 126 |

|    | 10.3 | 向量表      | ₹                     | 127 |

|    |      | 10.3.1   | 中断向量表                 |     |

|    |      | 10.3.2   | 中断事件请求序号              |     |

|    | 10.4 | 功能说      | 兑明                    | 134 |

|    |      | 10.4.1   | 不可屏蔽中断                |     |

|    |      | 10.4.2   | EIRQ 管脚中断             |     |

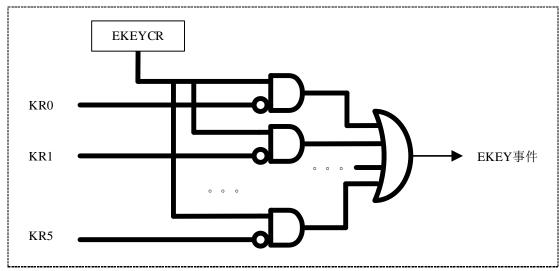

|    |      | 10.4.3   | EKEY 管脚事件             |     |

|    |      | 10.4.4   | 软件触发事件                |     |

|    |      | 10.4.5   | 中断源选择                 |     |

|    |      | 10.4.6   | WFE 事件选择              |     |

|    |      | 10.4.7   | WFE 唤醒事件管理            |     |

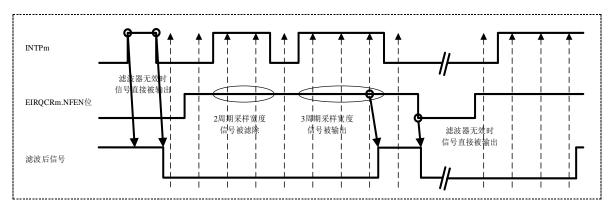

|    |      | 10.4.8   | 数字滤波器                 |     |

|    |      | 10.4.9   | 低功耗模式返回               | 140 |

|    |      | 10.4     | 4.9.1 休眠模式返回          | 140 |

|    |      | 10.4     | 4.9.2 停止模式返回          | 140 |

|    | 10.5 | 寄存器      | <b>晕说明</b>            | 141 |

|    |      | 10.5 1   | 功能保护控制寄存器(INTC FPRCR) | 143 |

|    |      | 10.5.2  | NMI 管脚中断控制寄存器(INTC_NMICR)           | 143 |

|----|------|---------|-------------------------------------|-----|

|    |      | 10.5.3  | 不可屏蔽中断使能寄存器(INTC_NMIER)             | 144 |

|    |      | 10.5.4  | 不可屏蔽中断标志寄存器(INTC_NMIFR)             | 145 |

|    |      | 10.5.5  | 不可屏蔽中断标志清除寄存器(INTC_NMICLR)          | 146 |

|    |      | 10.5.6  | EIRQ 管脚中断控制寄存器(INTC_EIRQCRm)(m=0~9) | 147 |

|    |      | 10.5.7  | EIRQ 管脚中断标志寄存器(INTC_EIRQFR)         | 147 |

|    |      | 10.5.8  | EIRQ 管脚中断标志清除寄存器(INTC_EIRQCLR)      | 148 |

|    |      | 10.5.9  | EKEY 管脚事件控制寄存器(INTC_EKEYCR)         | 148 |

|    |      | 10.5.10 | 软件触发事件控制寄存器(INTC_STRGCR)            | 149 |

|    |      | 10.5.11 | 中断选择 A 寄存器(INTC_ISELARm)(m=8~23)    | 149 |

|    |      | 10.5.12 | 中断选择 B 寄存器(INTC_ISELBRm)(m=24~31)   | 150 |

|    |      | 10.5.13 | WFE 事件使能寄存器(INTC_EVTER)             | 151 |

|    |      | 10.5.14 | 唤醒事件使能寄存器(INTC_WUPENR)              | 152 |

|    | 10.6 | 使用汽     | 主意事项                                | 153 |

| 11 | 内部的  | 付钟校准器   | 器(CTC)                              | 154 |

|    | 11.1 | 简介.     |                                     | 154 |

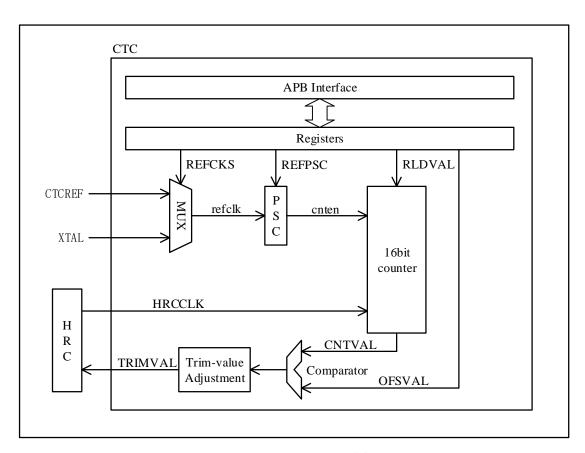

|    | 11.2 | 结构机     | 匡图                                  | 154 |

|    | 11.3 | 功能说     | 兑明                                  | 155 |

|    |      | 11.3.1  | 参考时钟                                | 155 |

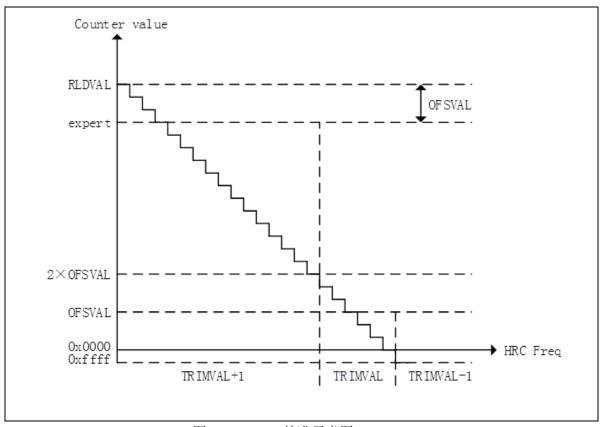

|    |      | 11.3.2  | 频率校准                                | 157 |

|    |      | 11.3.3  | 编程指南                                | 159 |

|    | 11.4 | 寄存器     | 器说明                                 | 160 |

|    |      | 11.4.1  | 时钟校准控制寄存器 1(CTC_CR1)                | 161 |

|    |      | 11.4.2  | 时钟校准控制寄存器 2(CTC_CR2)                | 163 |

|    |      | 11.4.3  | 时钟校准状态寄存器(CTC_STR)                  |     |

| 12 | 模数轴  | 专换模块    | (ADC)                               | 165 |

|    | 12.1 | 简介.     |                                     | 165 |

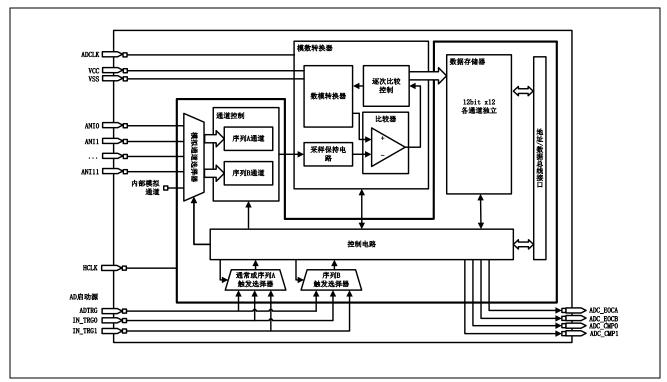

|    | 12.2 | ADC .   | 系统框图                                | 167 |

|    | 12.3 | 功能说     | 兑明                                  | 168 |

|    |      | 12.3.1  | ADC 时钟                              | 168 |

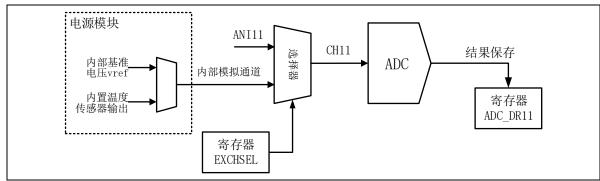

|    |      | 12.3.2  | 通道选择                                | 168 |

|    |      | 12.3.3  | 触发源选择                               | 169 |

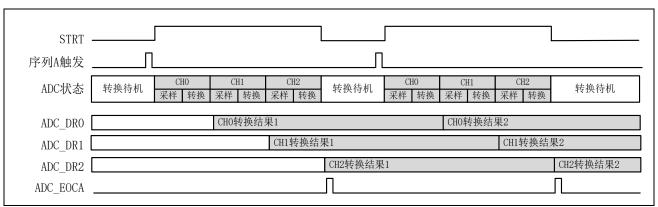

|    |      | 12.3.4  | 序列 A 单次扫描模式                         | 169 |

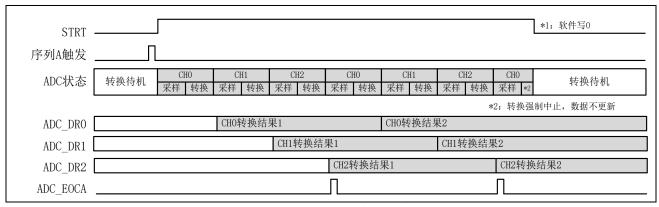

|    |      | 12.3.5  | 序列 A 连续扫描模式                         | 170 |

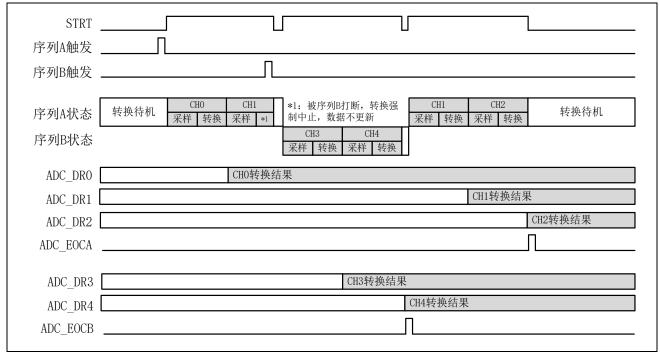

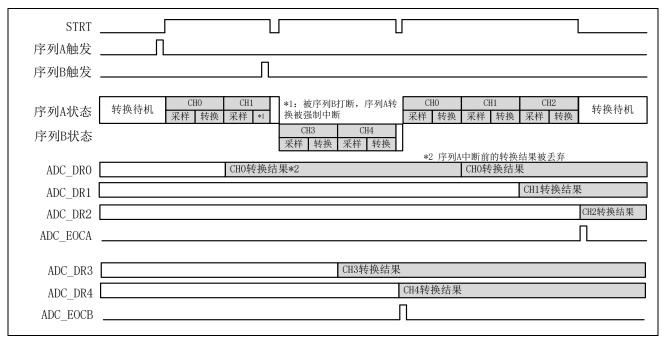

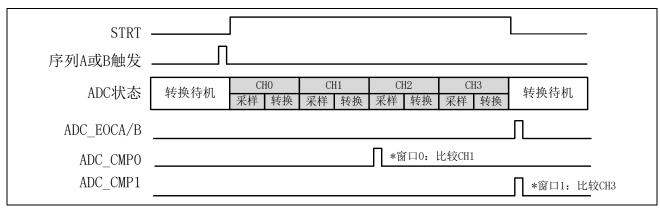

|    |      | 12.3.6  | 双序列扫描模式                             | 171 |

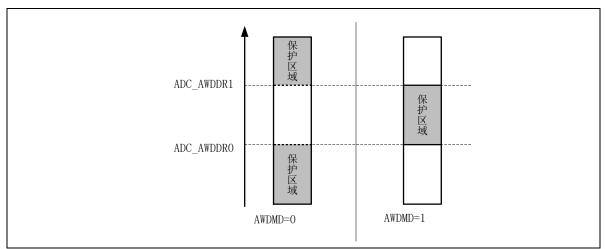

|    |      | 12.3.7  | 模拟看门狗功能                             | 173 |

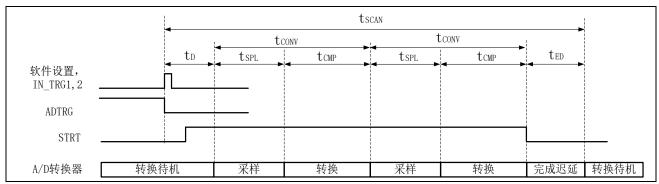

|    |      | 12.3.8  | 模拟输入的采样时间和转换时间                      |     |

|    |      | 12.3.9  | A/D 数据寄存器自动清除功能                     | 176 |

|    |      | 12.3.10 | 中断和事件信号输出                           | 176 |

|    | 12.4 | 寄存器     | <b>器说明</b>                          | 178 |

|    |      | 12.4.1  | A/D 启动寄存器 ADC_STR                   |     |

|    |      | 12.4.2  | A/D 控制寄存器 0 ADC_CR0                 | 181 |

|    |      | 12.4.3  | A/D 控制寄存器 1 ADC_CR1                             | 182 |

|----|------|---------|-------------------------------------------------|-----|

|    |      | 12.4.4  | A/D 转换开始触发寄存器 ADC_TRGSR                         | 183 |

|    |      | 12.4.5  | A/D 转换开始片内触发源选择寄存器 ADC_ITRGSELR0, ADC_ITRGSELR1 | 184 |

|    |      | 12.4.6  | A/D 通道选择寄存器 A ADC_CHSELRA0                      | 185 |

|    |      | 12.4.7  | A/D 通道选择寄存器 B ADC_CHSELRB0                      | 186 |

|    |      | 12.4.8  | A/D 扩展通道选择寄存器 ADC_EXCHSELR                      | 186 |

|    |      | 12.4.9  | A/D 采样状态寄存器 ADC_SSTR                            | 187 |

|    |      | 12.4.10 | A/D 中断状态寄存器 ADC_ISR                             | 187 |

|    |      | 12.4.11 | A/D 中断许可寄存器 ADC_ICR                             | 188 |

|    |      | 12.4.12 | A/D 中断状态复位寄存器 ADC_ISCLRR                        | 188 |

|    |      | 12.4.13 | A/D 数据寄存器 ADC_DR                                | 189 |

|    |      | 12.4.14 | 模拟看门狗控制寄存器 ADC_AWDCR                            | 190 |

|    |      | 12.4.15 | 模拟看门狗状态寄存器 ADC_AWDSR                            | 191 |

|    |      | 12.4.16 | 模拟看门狗状态复位寄存器 ADC_AWDSCLRR                       | 191 |

|    |      | 12.4.17 | 模拟看门狗阀值寄存器 ADC_AWD0DR0、ADC_AWD0DR1、ADC_AWD1DR0  | )、  |

|    |      | ADC_AW  | D1DR1                                           | 192 |

|    |      | 12.4.18 | 模拟看门狗比较通道选择寄存器 ADC_AWD0CHSR、ADC_AWD1CHSR        | 193 |

|    | 12.5 | 使用注     | 意事项                                             | 194 |

|    |      | 12.5.1  | 数据寄存器读取时注意事项                                    | 194 |

|    |      | 12.5.2  | 扫描完成中断处理注意事项                                    |     |

|    |      | 12.5.3  | 模块停止功能设定                                        | 194 |

|    |      | 12.5.4  | 切换低功耗模式的注意事项                                    | 194 |

|    |      | 12.5.5  | A/D 转换模拟通道输入的引脚设定                               | 194 |

|    |      | 12.5.6  | 噪声控制                                            | 194 |

| 13 | 通用知  | 定时器(Ti  | merB)                                           | 195 |

|    | 13.1 | 简介      |                                                 | 195 |

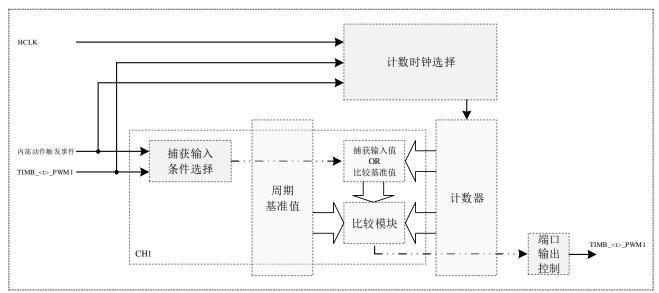

|    | 13.2 | 基本框     | 图                                               | 195 |

|    | 13.3 | 功能说     | 明                                               | 197 |

|    |      | 13.3.1  | 基本动作                                            | 197 |

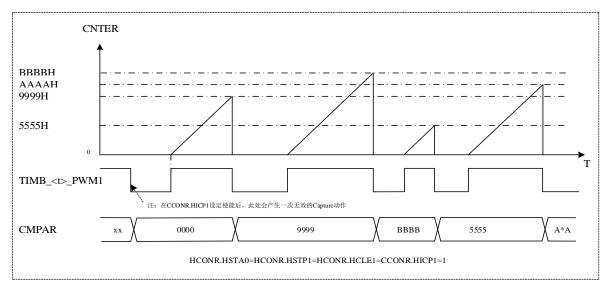

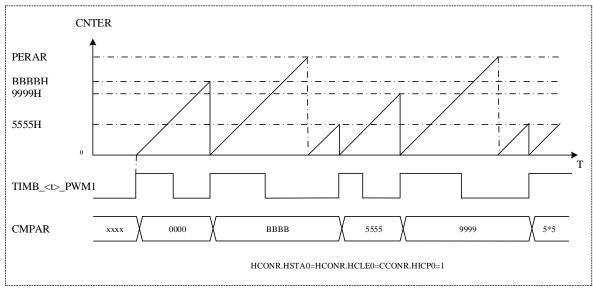

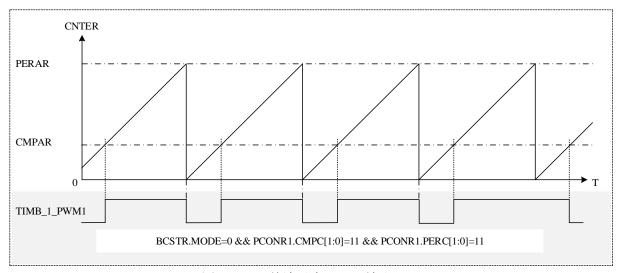

|    |      | 13.3.   | 1.1 波形模式                                        | 197 |

|    |      | 13.3.   | 1.2 比较输出                                        | 198 |

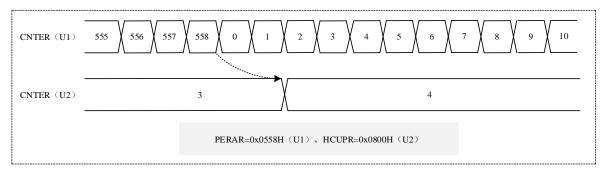

|    |      | 13.3.   | 1.3 捕获输入                                        | 199 |

|    |      | 13.3.2  | 时钟源选择                                           | 200 |

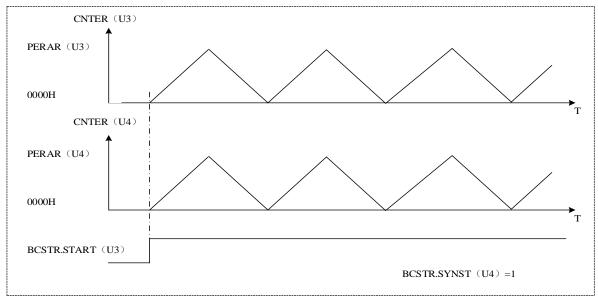

|    |      | 13.3.3  | 同步启动                                            | 201 |

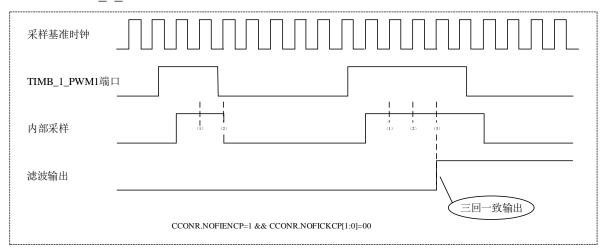

|    |      | 13.3.4  | 数字滤波                                            | 202 |

|    |      | 13.3.5  | 级联计数                                            | 203 |

|    |      | 13.3.6  | 脉宽测量                                            | 204 |

|    |      | 13.3.7  | 周期测量                                            | 205 |

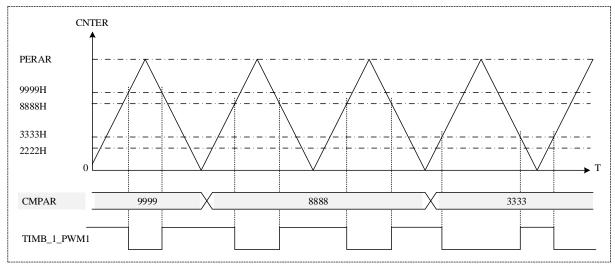

|    |      | 13.3.8  | PWM 输出                                          | 206 |

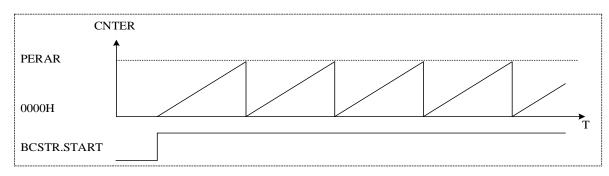

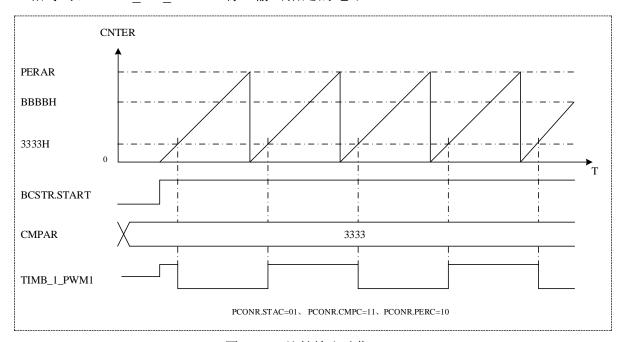

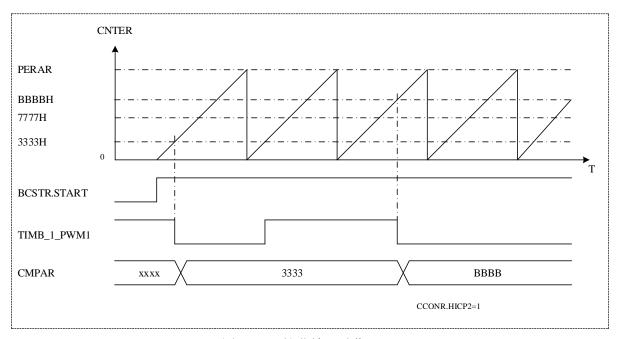

|    |      | 13.3.   | 8.1 单边对齐 PWM 输出                                 | 206 |

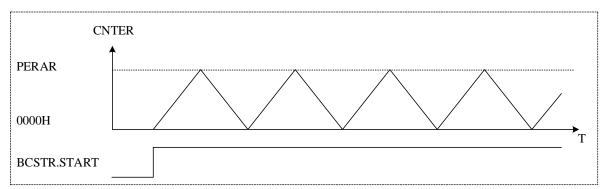

|    |      | 13.3.   | 8.2 双边对称 PWM 输出                                 | 207 |

|    | 13.4 | 中新及     | 事件说明                                            | 208 |

|    |      | 13.4.1  | 比较匹配中断及事件               | 208 |

|----|------|---------|-------------------------|-----|

|    |      | 13.4.2  | 周期匹配中断及事件               | 208 |

|    | 13.5 | 寄存器     | 器说明                     | 209 |

|    |      | 13.5.1  | 通用计数值寄存器(TMRB_CNTER)    | 210 |

|    |      | 13.5.2  | 周期基准值寄存器(TMRB_PERAR)    | 210 |

|    |      | 13.5.3  | 比较基准值寄存器(TMRB_CMPAR)    | 210 |

|    |      | 13.5.4  | 控制状态寄存器(TMRB_BCSTR)     | 211 |

|    |      | 13.5.5  | 中断控制寄存器(TMRB_ICONR)     | 213 |

|    |      | 13.5.6  | 事件控制寄存器(TMRB_ECONR)     | 213 |

|    |      | 13.5.7  | 状态标志寄存器(TMRB_STFLR)     | 214 |

|    |      | 13.5.8  | 捕获控制寄存器(TMRB_CCONR)     | 214 |

|    |      | 13.5.9  | 端口控制寄存器(TMRB_PCONR)     | 215 |

|    |      | 13.5.10 | 硬件触发事件选择寄存器(TMRB_HCONR) | 216 |

|    |      | 13.5.11 | 硬件递加事件选择寄存器(TMRB_HCUPR) | 218 |

|    |      | 13.5.12 | 硬件递减事件选择寄存器(TMRB_HCDOR) |     |

|    |      | 13.5.13 | 内部触发事件选择寄存器(TMRB_HTSSR) | 220 |

| 14 | 通用領  | 定时器()   | Гіmer0)                 | 221 |

|    | 14.1 | 简介.     |                         | 221 |

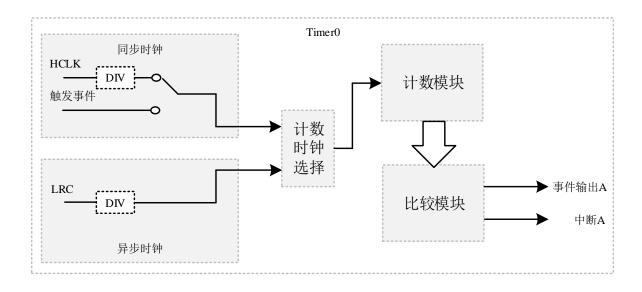

|    | 14.2 | 基本相     | 匡图                      | 221 |

|    | 14.3 | 功能证     | 兑明                      | 222 |

|    |      | 14.3.1  | 时钟源选择                   | 222 |

|    |      |         | 3.1.1 同步计数时钟源           |     |

|    |      | 14.     | 3.1.2 异步计数时钟源           | 222 |

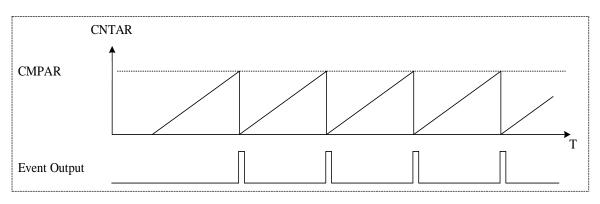

|    |      | 14.3.2  | 基本计数动作                  |     |

|    |      | 14.3.3  | 硬件触发动作                  |     |

|    | 14.4 | 中断及     | 及事件说明                   |     |

|    |      | 14.4.1  | 中断输出                    | 224 |

|    |      | 14.4.2  | 事件输出                    | 224 |

|    | 14.5 | 寄存器     | 器说明                     |     |

|    |      | 14.5.1  | 计数值寄存器(TMR0_CNTAR)      |     |

|    |      | 14.5.2  | 基准值寄存器(TMR0_CMPAR)      |     |

|    |      | 14.5.3  | 基本控制寄存器(TMR0_BCONR)     |     |

|    |      | 14.5.4  | 触发选择寄存器(TMR0_HTSSR)     |     |

|    |      | 14.5.5  | 状态标志寄存器(TMR0_STFLR)     |     |

|    | 14.6 |         | 主意事项                    |     |

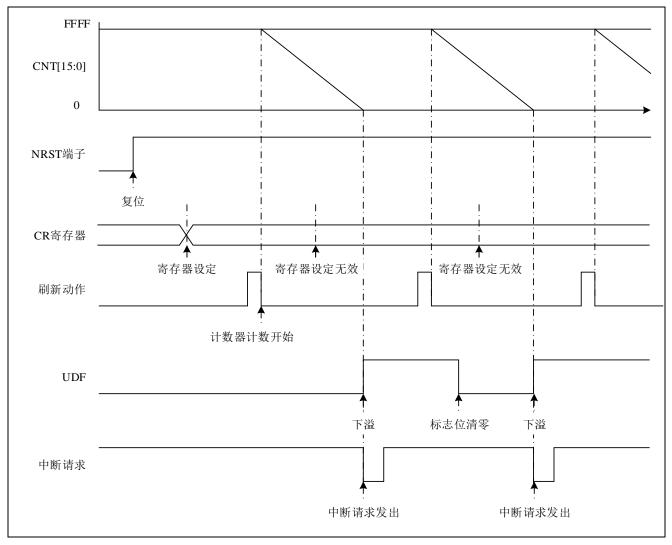

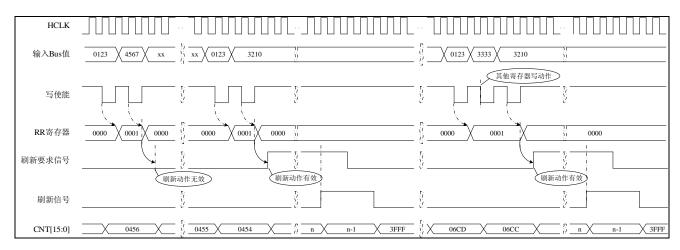

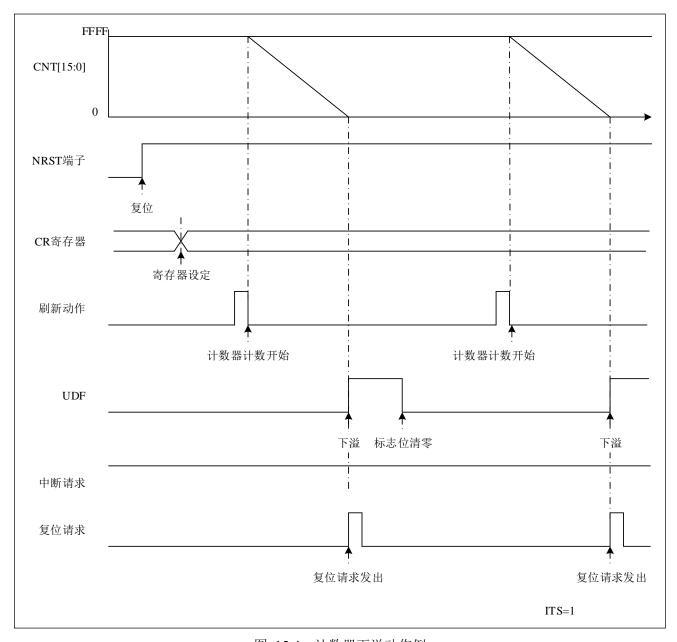

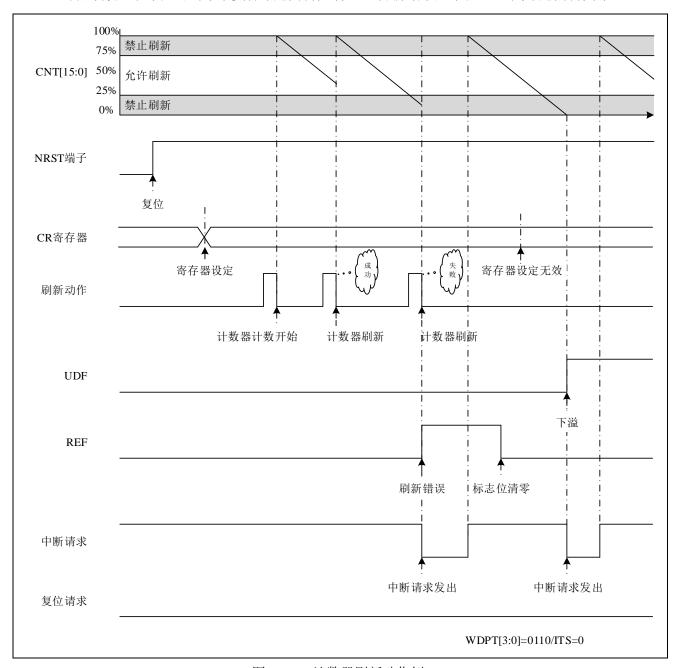

| 15 | 看门   |         | (SWDT)                  |     |

|    | 15.1 |         |                         |     |

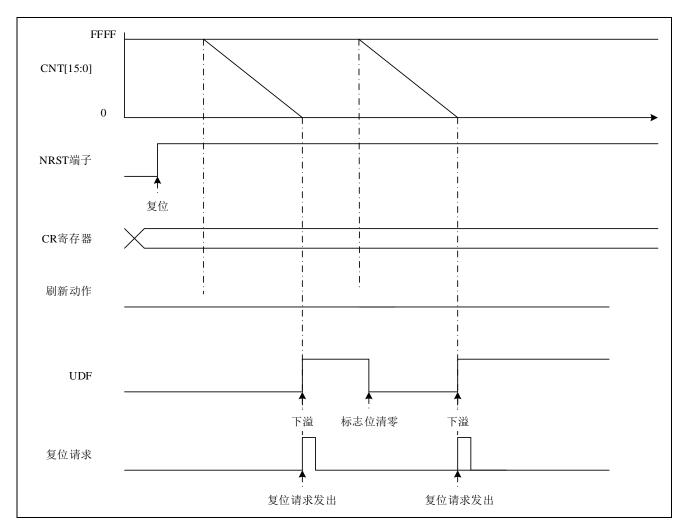

|    | 15.2 |         | 兑明                      |     |

|    |      | 15.2.1  | 启动看门狗                   |     |

|    |      | 15.2.2  | 硬件启动方式                  |     |

|    |      | 15.2.3  | 软件启动方式                  |     |

|    |      | 1524    | 副新动作                    | 235 |

|    |      | 15.2.5      | 标志位                | 235 |

|----|------|-------------|--------------------|-----|

|    |      | 15.2.6      | 中断复位               | 236 |

|    |      | 15.2.7      | 计数下溢               | 237 |

|    |      | 15.2.8      | 刷新错误               | 238 |

|    | 15.3 | 寄存          | 器说明                | 239 |

|    |      | 15.3.1      | 控制寄存器(SWDT_CR)     | 240 |

|    |      | 15.3.2      | 状态寄存器(SWDT_SR)     | 242 |

|    |      | 15.3.3      | 刷新寄存器(SWDT_RR)     | 242 |

|    | 15.4 | 使用泡         | 注意事项               | 243 |

| 16 | 通用   | 司步异步        | 收发器(USART)         | 244 |

|    | 16.1 | 简介          |                    | 244 |

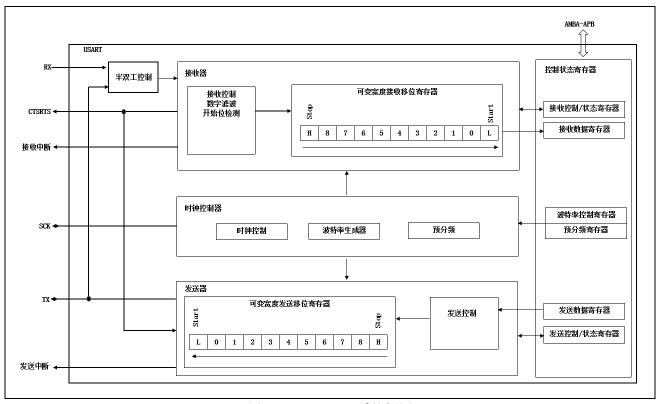

|    | 16.2 | USAI        | RT 系统框图            | 245 |

|    | 16.3 | 管脚          | 说明                 | 246 |

|    | 16.4 | 功能          | 说明                 | 247 |

|    |      | 16.4.1      | UART               | 247 |

|    |      | 16.         | .4.1.1 时钟          | 247 |

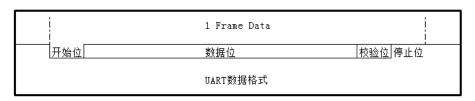

|    |      | 16.         | .4.1.2 数据格式        | 248 |

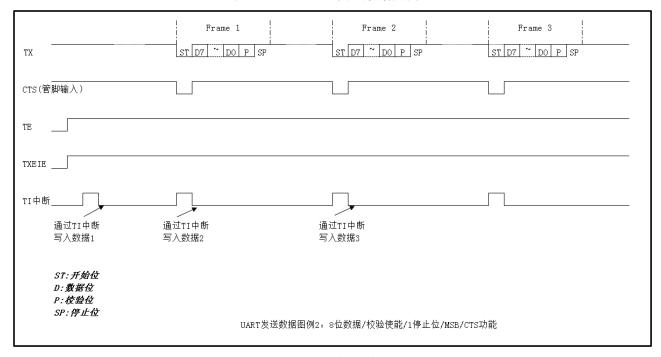

|    |      | 16.         | .4.1.3 调制解调器操作     | 248 |

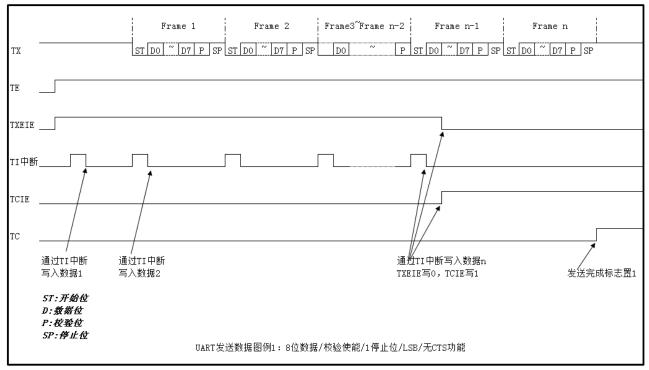

|    |      | 16.         | .4.1.4 发送器         | 249 |

|    |      | 16.         | .4.1.5 接收器         | 251 |

|    |      | 16.         | .4.1.6UART 半双工通信方式 | 254 |

|    |      | 16.         | .4.1.7UART 中断和事件   | 254 |

|    |      | 16.4.2      | 多处理器通信             | 255 |

|    |      | 16.         | .4.2.1 功能简介        |     |

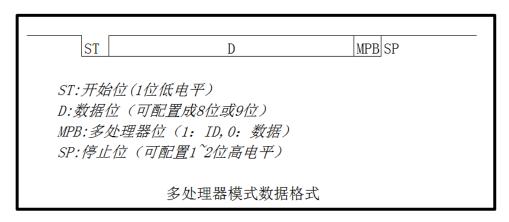

|    |      | 16.         | .4.2.2 数据格式        |     |

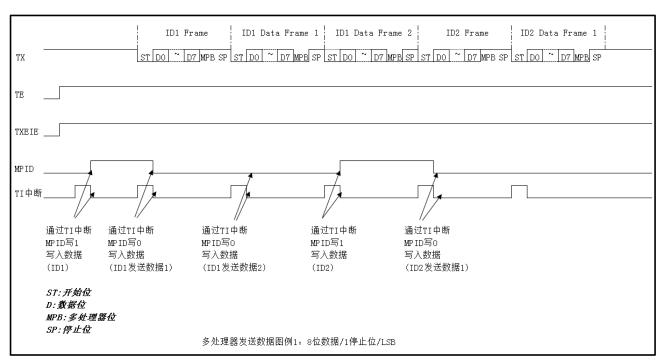

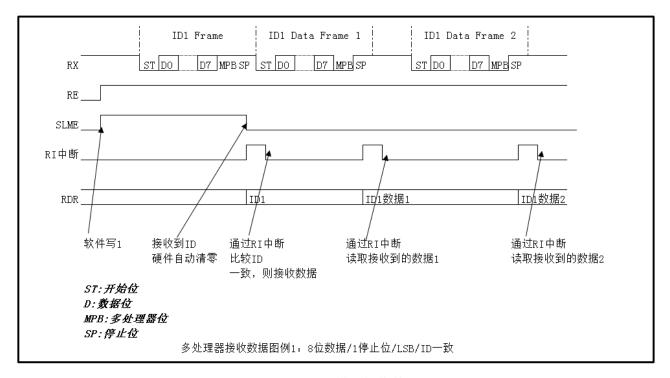

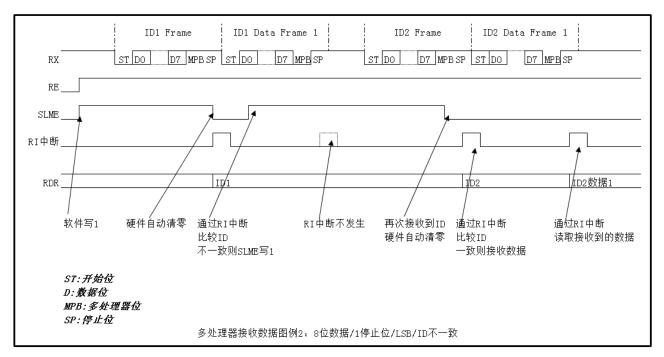

|    |      | 16.         | .4.2.3 动作说明        | 256 |

|    |      | 16.         | .4.2.4 中断和事件       | 259 |

|    |      | 16.4.3      | UART_LIN           |     |

|    |      | 16.         | .4.3.1 功能简介        |     |

|    |      |             | .4.3.2 LIN 数据格式    |     |

|    |      |             | .4.3.3 LIN 发送      |     |

|    |      | 16.         | .4.3.4LIN 接收       |     |

|    |      | 16.4.4      | 时钟同步模式             |     |

|    |      |             | .4.4.1 时钟          |     |

|    |      |             | .4.4.2 数据格式        |     |

|    |      | 16.         | .4.4.3 调制解调器操作     |     |

|    |      |             | .4.4.4 发送器         |     |

|    |      |             | .4.4.5 接收器         |     |

|    |      |             | .4.4.6 同时发送接收数据    |     |

|    |      | 16.         | .4.4.7 时钟同步模式中断和事件 |     |

|    |      | 16.4.5      | 数字滤波功能             |     |

|    | 165  | <b>玄</b> 方! | <u> </u>           | 272 |

|    |      | 16.5.1             | 状态寄存器(USART_SR)        | 273 |

|----|------|--------------------|------------------------|-----|

|    |      | 16.5.2             | 数据寄存器(USART_DR)        | 275 |

|    |      | 16.5.3             | 波特率寄存器(USART_BRR)      | 276 |

|    |      | 16.5.4             | 控制寄存器 1(USART_CR1)     | 277 |

|    |      | 16.5.5             | 控制寄存器 2(USART_CR2)     | 280 |

|    |      | 16.5.6             | 控制寄存器 3(USART_CR3)     | 281 |

|    |      | 16.5.7             | 预分频寄存器(USART_PR)       | 282 |

|    | 16.6 | 使用                 | 注意事项                   | 283 |

|    |      | 16.6.1             | UART 注意事项              |     |

|    |      | 16.6.2             | 时钟同步模式注意事项             |     |

|    |      | 16.6.3             | 其他注意事项                 |     |

| 17 | 集成日  | 电路总线               | (I <sup>2</sup> C)     | 284 |

|    | 17.1 | 简介                 |                        | 284 |

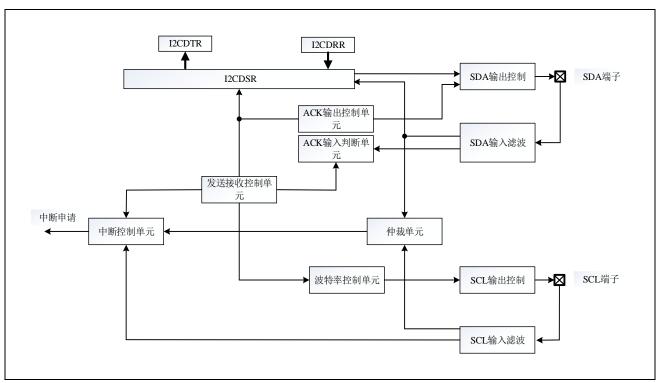

|    | 17.2 | I <sup>2</sup> C 系 | 系统框图                   | 285 |

|    |      | 17.2.1             | 系统框图                   |     |

|    |      | 17.2.2             | 结构图                    |     |

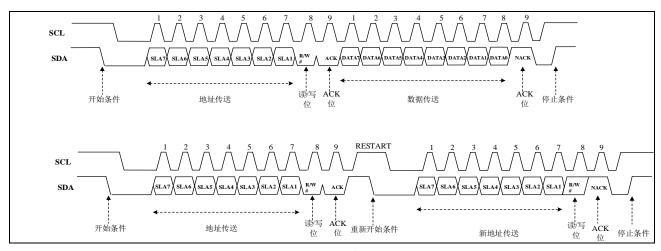

|    | 17.3 | 动作                 | 说明                     | 287 |

|    |      | 17.3.1             | PC 协议                  |     |

|    |      | 17                 | 7.3.1.1 开始条件           |     |

|    |      | 17                 | 7.3.1.2 地址传送           |     |

|    |      | 17                 | 7.3.1.3 数据传送           |     |

|    |      | 17                 | 7.3.1.4 停止条件           |     |

|    |      | 17                 | 7.3.1.5 重新开始条件         |     |

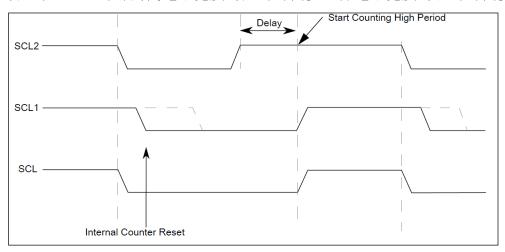

|    |      | 17                 | 7.3.1.6 SCL 时钟同步       | 294 |

|    |      | 17                 | 7.3.1.7 仲裁             | 294 |

|    |      | 17                 | 7.3.1.8 握手             |     |

|    |      | 17.3.2             |                        |     |

|    |      | 17                 | 7.3.2.1 从机地址匹配         | 298 |

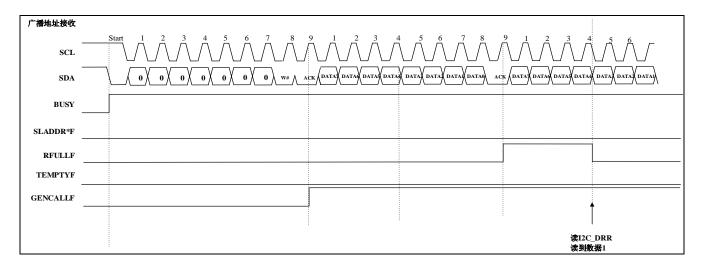

|    |      |                    | 7.3.2.2 广播地址匹配         |     |

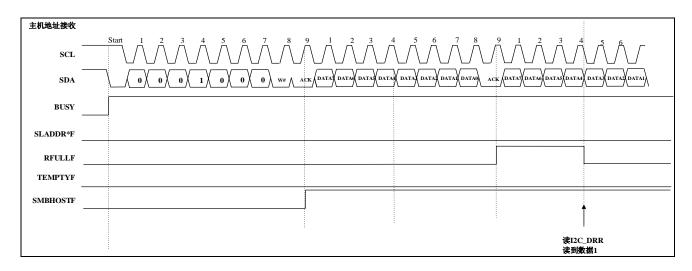

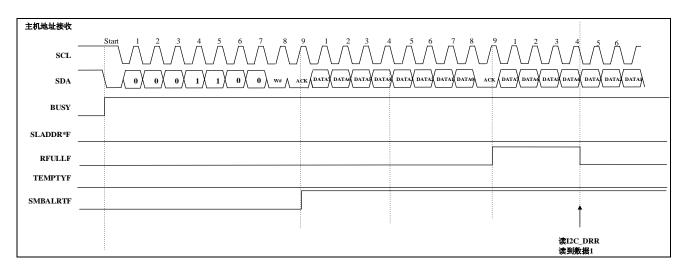

|    |      |                    | 7.3.2.3 SMBus 主机地址匹配   |     |

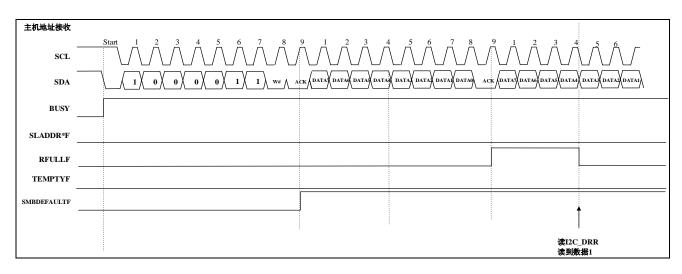

|    |      | 17                 | 7.3.2.4 SMBus 报警响应地址匹配 |     |

|    |      | 17                 | 7.3.2.5 SMBus 默认地址匹配   |     |

|    |      | 17.3.3             | SMBus 动作               |     |

|    |      | 17                 | 7.3.3.1 SMBus 超时测量     |     |

|    |      | 17                 | 7.3.3.2 数据包错误码(PEC)    |     |

|    |      | 17.3.4             | 复位                     |     |

|    |      | 17.3.5             | 中断和事件信号输出              |     |

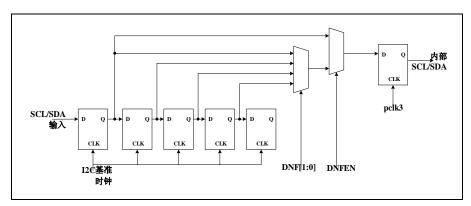

|    |      | 17.3.6             | 可编程数字滤波                |     |

|    | 17.4 | 应用:                | 软件设定 I2C 初始化流程         | 310 |

|    | 17.5 | 寄存                 | 器说明                    | 311 |

|    |      | 17.5.1             | I2C 控制寄存器 1(I2C_CR1)   |     |

|    |      | 1752               | I2C 均制                 | 314 |

|    |       | 17.5.3  | I2C 从机地址寄存器 0(I2C_SLR0) | 316 |

|----|-------|---------|-------------------------|-----|

|    |       | 17.5.4  | I2C 从机地址寄存器 1(I2C_SLR1) | 317 |

|    |       | 17.5.5  | I2C 状态寄存器(I2C_SR)       | 318 |

|    |       | 17.5.6  | I2C 状态清零寄存器(I2C_CLR)    |     |

|    |       | 17.5.7  | I2C 数据发送寄存器(I2C_DTR)    |     |

|    |       | 17.5.8  | I2C 数据接收寄存器(I2C_DRR)    |     |

|    |       | 17.5.9  | I2C 数据移位寄存器(I2C_DSR)    |     |

|    |       | 17.5.10 | I2C 时钟控制寄存器(I2C_CCR)    |     |

|    |       | 17.5.11 | I2C 滤波控制寄存器(I2C_FLTR)   | 328 |

| 18 | 串行外   | 小设接口    | (SPI)                   | 329 |

|    | 18.1  | 简介.     |                         | 329 |

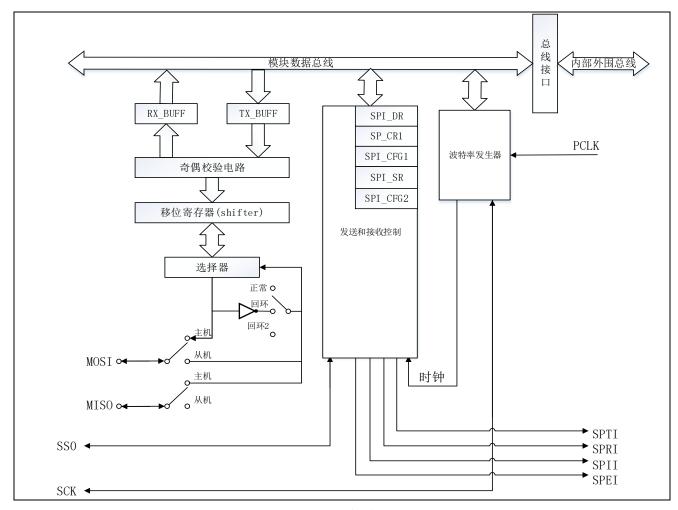

|    | 18.2  | SPI 系   | <b> </b>                | 331 |

|    | 18.3  | 管脚设     | 说明                      | 332 |

|    | 18.4  | SPI 컷   | <b>力作系统说明</b>           | 333 |

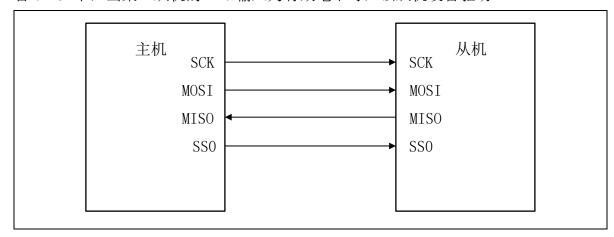

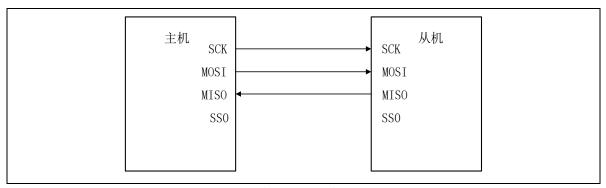

|    |       | 18.4.1  | 主机模式的管脚状态               |     |

|    |       | 18.4.2  | 从机模式的管脚状态               |     |

|    |       | 18.4.3  | SPI 系统连接实例              |     |

|    | 18.5  | 数据证     | 通信说明                    | 336 |

|    |       | 18.5.1  | 波特率                     |     |

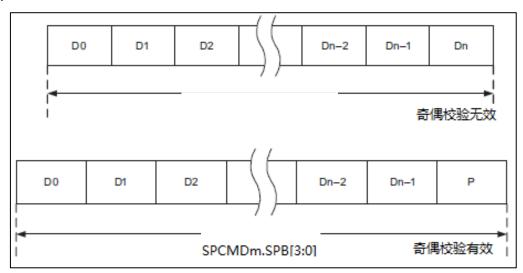

|    |       | 18.5.2  | 数据格式                    |     |

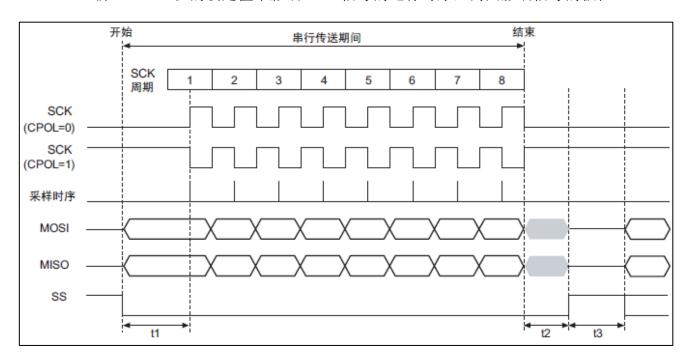

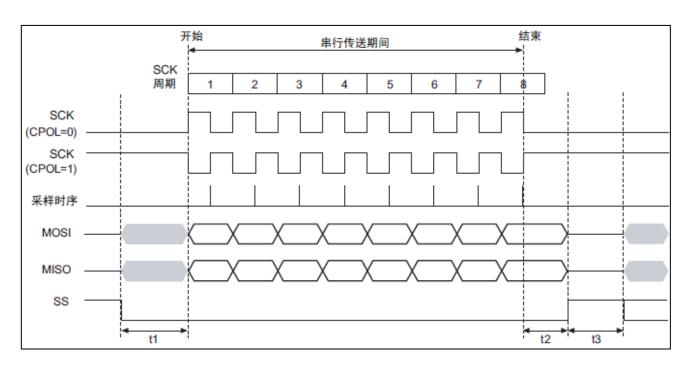

|    |       | 18.5.3  | 传送格式                    |     |

|    |       | 18.5.4  | 通信方式                    |     |

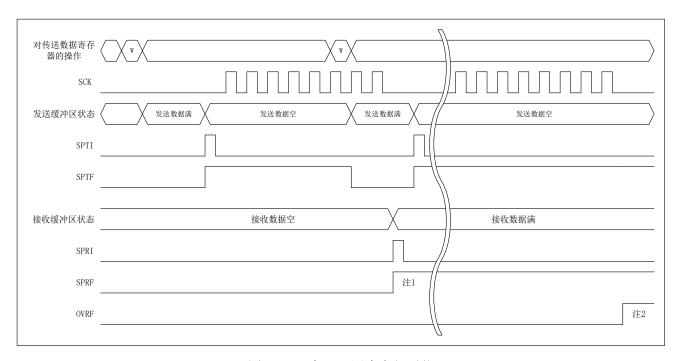

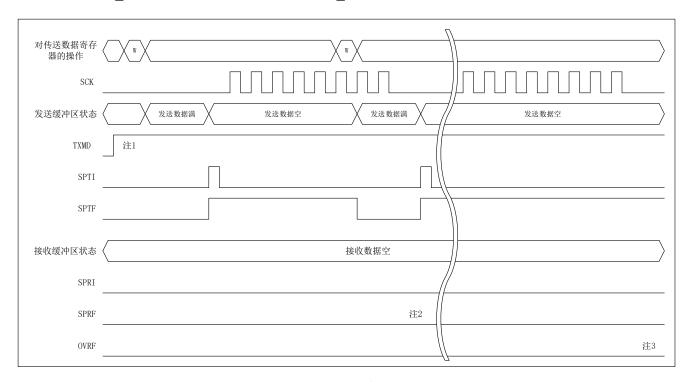

|    | 18.6  | 运行证     | 说明                      | 343 |

|    |       | 18.6.1  | 运行模式概要                  |     |

|    |       | 18.6.2  | SPI 运行模式时的主机动作          |     |

|    |       | 18.6.3  | SPI 运行模式时的从机动作          |     |

|    |       | 18.6.4  | 时钟同步运行模式中的主机动作          |     |

|    |       | 18.6.5  | 时钟同步运行模式中的从机动作          |     |

|    |       | 18.6.6  | 几种 SPI 动作的处理流程          |     |

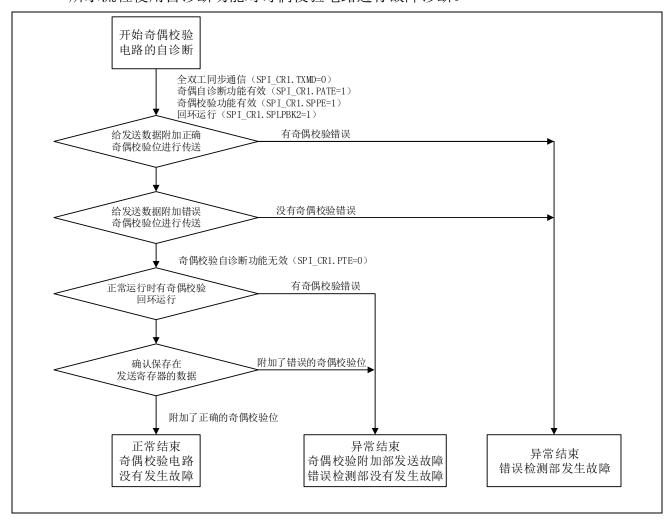

|    | 18.7  | 奇偶构     | 交验位自诊断                  | 351 |

|    | 18.8  | 错误机     | <u> </u>                | 352 |

|    |       | 18.8.1  | 欠载错误                    | 353 |

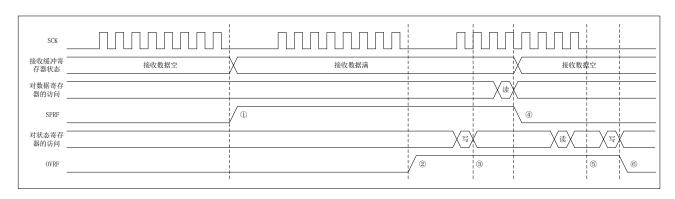

|    |       | 18.8.2  | 过载错误                    | 353 |

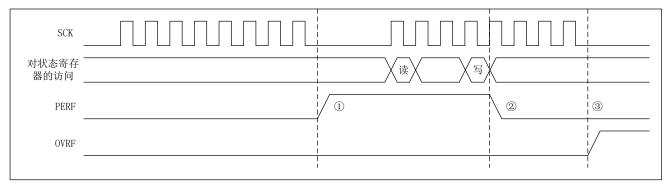

|    |       | 18.8.3  | 奇偶校验错误                  | 353 |

|    | 18.9  | SPI 的   | 的初始化                    | 355 |

|    |       | 18.9.1  | 清除 SPE 位进行初始化           |     |

|    |       | 18.9.2  | 系统复位初始化                 |     |

|    | 18.10 |         | 原                       |     |

|    | 18.11 | 可供值     | 使用的事件触发源                | 357 |

|    | 18.12 | 多 寄存器   | 器说明                     | 358 |

|    |       | 18.12.1 | SPI 数据寄存器(SPI_DR)       |     |

|    |       | 18.12.2 | SPI 控制寄存器(SPI_CR1)      | 360 |

|    |      | 18.12.3 | SPI 通信配置寄存器 1(SPI_CFG1) |     |

|----|------|---------|-------------------------|-----|

|    |      | 18.12.4 | SPI 状态寄存器(SPI_SR)       |     |

|    |      | 18.12.5 | SPI 通信配置寄存器 2(SPI_CFG2) |     |

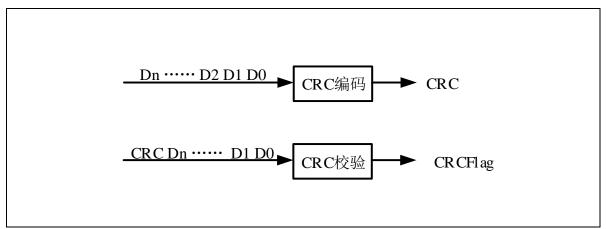

| 19 | CRC  | 运算(CR   | (C)                     | 365 |

|    | 19.1 | 简介      |                         | 365 |

|    | 19.2 | 功能框     | 图                       | 365 |

|    | 19.3 | 功能说     | 台明                      | 366 |

|    |      | 19.3.1  | CRC16 编码模式              |     |

|    |      | 19.3.2  | CRC16 校验模式              | 366 |

|    |      | 19.3.3  | CRC32 编码模式              | 367 |

|    |      | 19.3.4  | CRC32 校验模式              | 367 |

|    | 19.4 | 寄存器     | <b>晕说明</b>              | 368 |

|    |      | 19.4.1  | 控制寄存器(CRC_CR)           |     |

|    |      | 19.4.2  | 结果寄存器(CRC_RESLT)        |     |

|    |      | 19.4.3  | 数据寄存器(CRC_DAT)          |     |

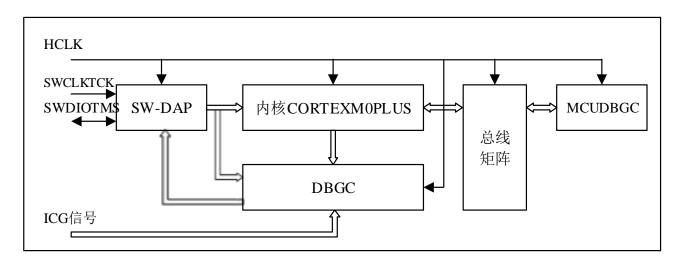

| 20 | 调试   | 控制器(D   | OBGC)                   | 370 |

|    | 20.1 | 简介      |                         | 370 |

|    | 20.2 | DBGC    | こ系统框图                   | 370 |

|    | 20.3 | 调试引     | 脚                       | 371 |

|    |      | 20.3.1  | SWD 调试引脚                | 371 |

|    |      | 20.3.2  | SWD 引脚分配                |     |

|    |      | 20.3.3  | SWD 引脚上的内部上拉和下拉         |     |

|    | 20.4 | 寄存器     |                         | 372 |

|    |      | 20.4.1  | DBG 状态寄存器(MCUDBGSTAT)   |     |

|    |      | 20.4.2  | 外设调试暂停寄存器(MCUSTPCTL)    |     |

|    | 20.5 | SW 调    | 试端口                     | 375 |

|    |      | 20.5.1  | SW 协议简介                 |     |

|    |      | 20.5.2  | SW 协议简介                 |     |

| 版ス |      | & 联系方   | 5式                      | 376 |

# 表目录

| 表 | 1-1  | 存储器映射                    | 22  |

|---|------|--------------------------|-----|

| 表 | 3-1  | 复位方式及产生条件                | 27  |

| 表 | 3-2  | 复位方式及复位标志                | 28  |

| 表 | 3-3  | RMU 寄存器一览                | 34  |

| 表 | 4-1  | 各个内部时钟的规格                | 39  |

| 表 | 5-1  | LVD 特性                   | 63  |

| 表 | 5-2  | LVD 电压选择                 | 64  |

| 表 | 5-3  | 低功耗模式的运行条件及各模块在低功耗模式下的状态 | 68  |

| 表 | 5-4  | 运行模式说明                   | 69  |

| 表 | 5-5  | 寄存器保护列表                  | 74  |

| 表 | 5-6  | 寄存器一览表                   | 75  |

| 表 | 6-1  | 寄存器一览表                   | 84  |

| 表 | 7-1  | CPU 时钟频率和 FLASH 读等待周期对照表 | 93  |

| 表 | 7-2  | 寄存器一览表                   | 98  |

| 表 | 8-1  | SRAM 空间分配                | 108 |

| 表 | 9-1  | PORT 寄存器一览               | 114 |

| 表 | 10-1 | 中断向量表                    | 129 |

| 表 | 10-2 | 中断事件请求序号与选择              | 133 |

| 表 | 10-3 | 寄存器列表                    | 142 |

| 表 | 11-1 | HRC 目标频率为 48MHz 时的测量误差   | 155 |

| 表 | 11-2 | HRC 目标频率为 32MHz 时的测量误差   | 156 |

| 表 | 11-3 | CTC 寄存器一览表               | 160 |

| 表 | 12-1 | 各 ADC 输入信号说明             | 167 |

| 表 | 12-2 | 序列 A 和 B 的各种竞争           | 172 |

| 表 | 12-3 | AD 转换时间                  | 175 |

| 表 | 12-4 | ADC 寄存器一览 1/2            | 178 |

| 表 | 12-5 | ADC 寄存器一览 2/2            | 179 |

| 表 | 13-1 | TimerB 的基本功能及特性          | 195 |

| 表 | 13-2 | TimerB 端口列表              | 196 |

| 表 | 13-3 | 寄存器列表                    | 209 |

| 表 | 14-1 | 寄存器列表                    | 225 |

| 表 | 15-1 | 看门狗计数器的基本特性              | 231 |

| 表 | 15-2 | 寄存器列表                    | 239 |

| 表 | 16-1 | USART 管脚说明               | 246 |

| 表 | 16-2 | UART 中断/事件表              | 254 |

| 表 | 16-3 | 多处理器模式中断/事件表             | 259 |

| 表 | 16-4 | 时钟同步模式中断/事件表             | 270 |

| 表 | 16-5 | USART 寄存器一览表             | 272 |

| 表 | 17-1 | 输入/输出引脚                  | 286 |

| 表 | 17-2 | 寄存器一览表                   | 311 |

#### XHSC 小华半导体 XIAOHUA SEMICONDUCTOR

| 表 1 | 18-1 | SPI 的特性要点        | . 330 |

|-----|------|------------------|-------|

| 表 1 | 18-2 | 管脚说明             | . 332 |

|     |      | 主机模式时 SPI 管脚状态说明 |       |

|     |      | 从机模式时 SPI 管脚状态说明 |       |

| 表 1 | 18-5 | 部分设定值下位速         | . 336 |

|     |      | SPI 模式和寄存器设定关系   |       |

| 表 1 | 18-7 | 错误检测对应表          | 352   |

| 表 1 | 18-8 | SPI 中断源说明        | . 356 |

| 表 1 | 19-1 | CRC 寄存器列表        | . 368 |

| 表 2 | 20-1 | SWJ 调试端口引脚       | . 371 |

# 图目录

| 冬 | 2-1  | 总线架构                               | 24  |

|---|------|------------------------------------|-----|

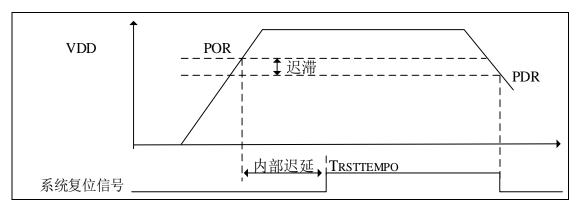

| 图 | 3-1  | 上电复位                               | 29  |

| 图 | 3-2  | RESET 复位时序                         | 30  |

| 图 | 3-3  | LVD 复位                             | 30  |

| 图 | 3-4  | 专用看门狗复位                            | 31  |

| 图 | 3-5  | 软件复位                               | 31  |

| 图 | 3-6  | RAM 奇偶校验复位                         | 32  |

| 图 | 3-7  | M0+ Lockup 复位                      | 32  |

| 图 | 3-8  | 外部高速振荡异常复位                         | 33  |

| 图 | 4-1  | 时钟系统框图                             | 37  |

| 图 | 4-2  | 外部高速振荡器连接事例                        | 40  |

| 图 | 4-3  | 外部时钟输入的连接事例图                       | 41  |

| 图 | 4-4  | 外部高速振荡器故障检测例                       | 42  |

| 图 | 4-5  | 系统时钟选择 XTAL,检测到 XTAL 振荡故障例         | 43  |

| 图 | 5-1  | 电源构成图                              | 61  |

| 图 | 5-2  | 上电复位、掉电复位波形                        | 62  |

| 图 | 5-3  | LVD 中断/复位框图                        | 65  |

| 图 | 5-4  | LVD 中断时序图                          | 66  |

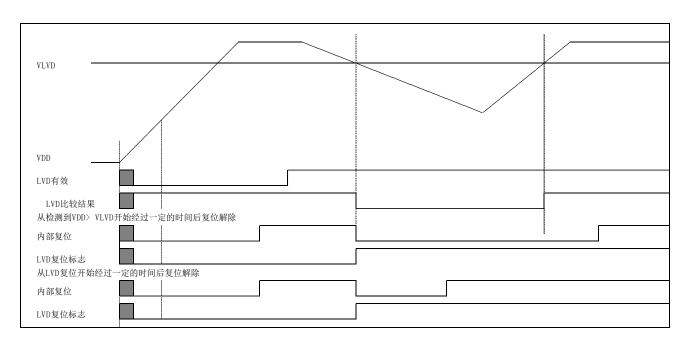

| 图 | 5-5  | LVD 复位时序图                          | 66  |

| 图 | 7-1  | FLASH 地址结构                         | 92  |

| 图 | 9-1  | 端口基本结构示意图                          | 110 |

| 图 | 10-1 | 中断系统框图                             | 126 |

| 图 | 11-1 | CTC 的基本框图                          | 154 |

| 图 | 11-2 | CTC 校准示意图                          | 157 |

| 图 | 12-1 | ADC 框图                             | 167 |

| 图 | 12-2 | 内部模拟通道选择                           | 168 |

| 图 | 12-3 | 序列 A 单次扫描模式                        | 169 |

| 图 | 12-4 | 序列 A 连续扫描                          | 170 |

| 图 | 12-5 | 双序列扫描模式(RSCHSEL=0 序列 A 从被中断通道重新启动) | 172 |

|   |      | 双序列扫描模式(RSCHSEL=1 序列 A 从第一个通道重新启动) |     |

| 图 | 12-7 | 模拟看门狗保护区域(比较条件)                    | 174 |

| 图 | 12-8 | A/D 转换时间                           |     |

| 图 | 12-9 |                                    |     |

| 图 | 13-1 | = , ,=, ,                          |     |

| 图 | 13-2 |                                    |     |

|   | 13-3 |                                    |     |

|   | 13-4 |                                    |     |

|   | 13-5 |                                    |     |

|   | 13-6 | ********                           |     |

| 冬 | 13-7 | PWM 输入端口的滤波功能                      | 202 |

#### X出SC小华半导体 Xiaohua semiconductor

| 图 | 13-8  | 32 位级联计数动作                   |     |

|---|-------|------------------------------|-----|

| 图 | 13-9  | 脉宽测量                         | 204 |

| 图 | 13-10 | 周期测量                         | 205 |

| 图 | 13-11 | 单边对齐 PWM 输出                  | 206 |

| 图 | 13-12 | 双边对称 PWM 输出                  | 207 |

| 图 | 14-1  | Timer() 基本框图                 | 221 |

| 图 | 14-2  | Timer0 计数时序图                 |     |

| 图 | 15-1  | 硬件启动例                        |     |

| 图 | 15-2  | 软件启动例                        |     |

| 图 | 15-3  | 各种刷新动作时序示例(动作确认,刷新要求信号的下降沿等) |     |

| 图 | 15-4  | 计数器下溢动作例                     | 237 |

| 图 | 15-5  | 计数器刷新动作例                     | 238 |

| 图 | 16-1  | USART 系统框图                   | 245 |

| 图 | 16-2  | UART 数据格式                    | 248 |

| 图 | 16-3  | UART 发送数据图例 1                |     |

| 图 | 16-4  | UART 发送数据图例 2                |     |

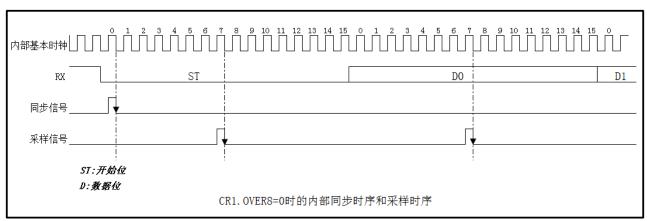

| 图 | 16-5  | UART 内部同步和采样时序               | 251 |

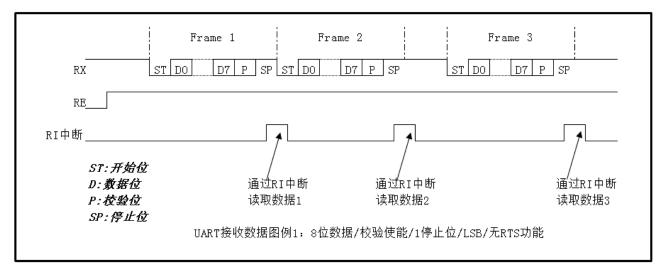

| 图 | 16-6  | UART 接收数据图例 1                | 253 |

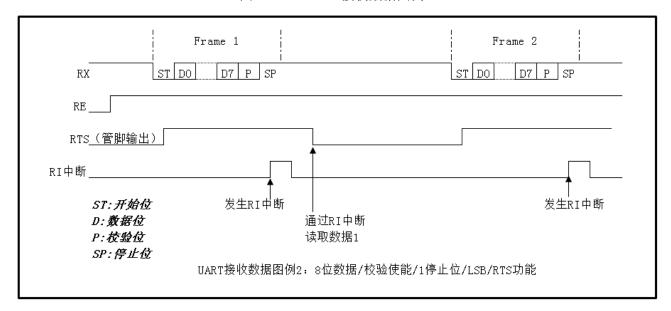

| 图 | 16-7  | UART 接收数据图例 2                |     |

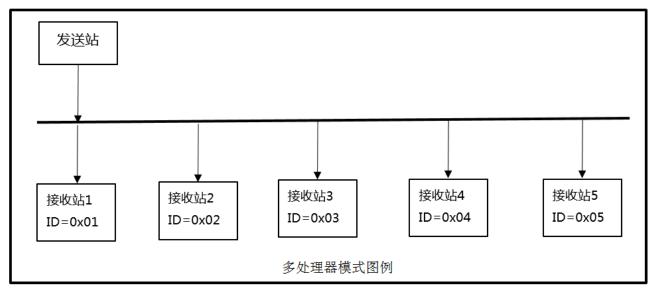

| 图 | 16-8  | 多处理器通信图例                     |     |

| 图 | 16-9  | 多处理器模式数据格式                   |     |

| 图 | 16-10 | 多处理器模式发送数据图例                 |     |

| 图 | 16-11 | 多处理器模式接收数据图例 1               |     |

| 图 | 16-12 | 多处理器模式接收数据图例 2               |     |

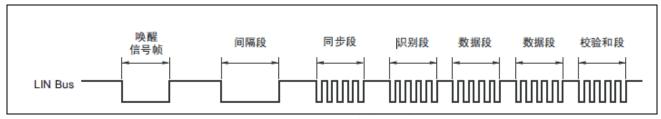

|   | 16-13 | LIN 总线数据行为                   |     |

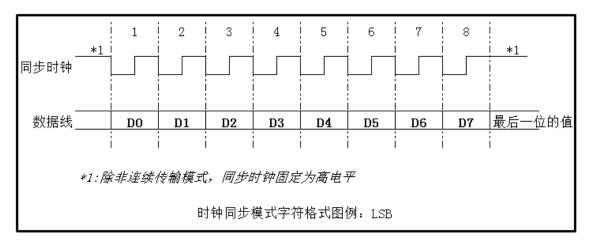

| 图 | 16-14 | 时钟同步模式数据格式                   |     |

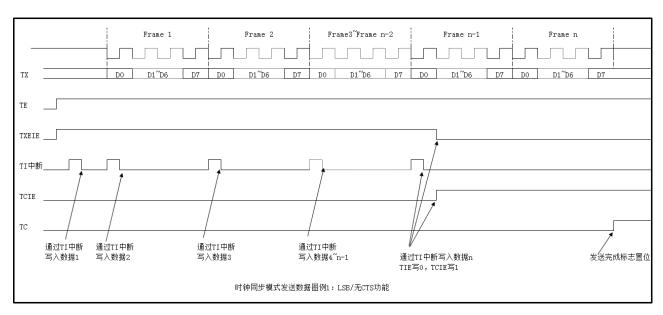

|   | 16-15 | 时钟同步模式发送数据图例 1               |     |

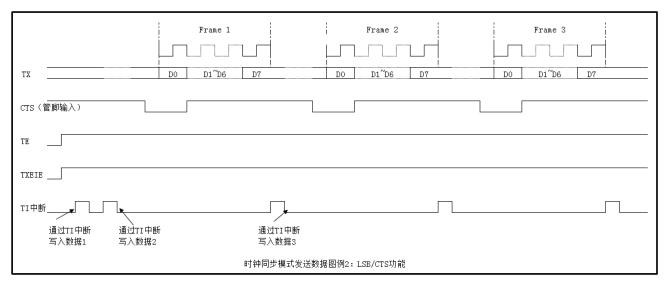

| 图 | 16-16 | 时钟同步模式发送数据图例 2               |     |

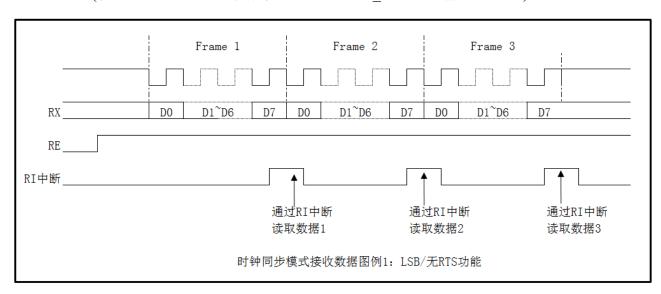

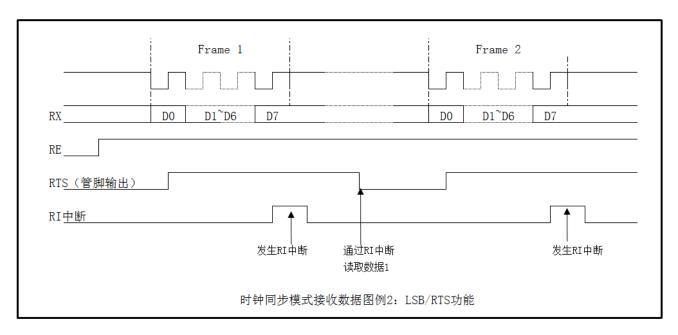

| 图 | 16-17 |                              |     |

|   | 16-18 |                              |     |

|   |       | PC 系统框图                      |     |

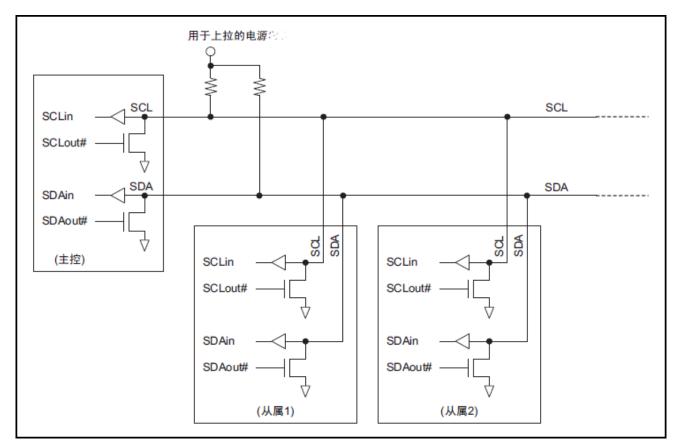

| 图 |       | I <sup>2</sup> C 总线的结构例      |     |

|   |       | I <sup>2</sup> C 总线的时序图      |     |

|   |       | I <sup>2</sup> C 总线的数据格式     |     |

|   |       | 7 位地址格式的主机发送数据时序图(例)         |     |

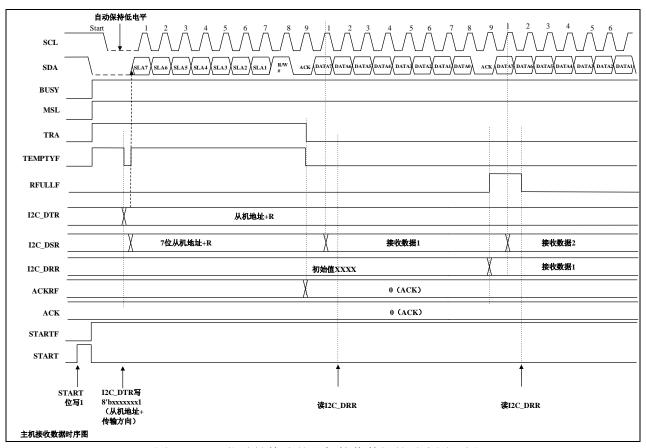

|   | 17-6  | 7位地址格式的主机接收数据的时序图(例)         |     |

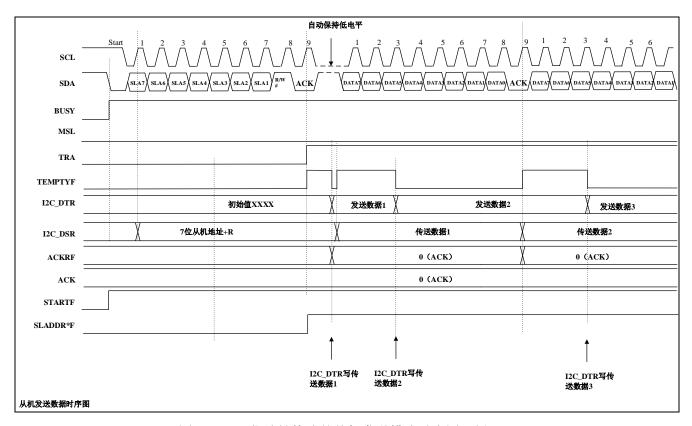

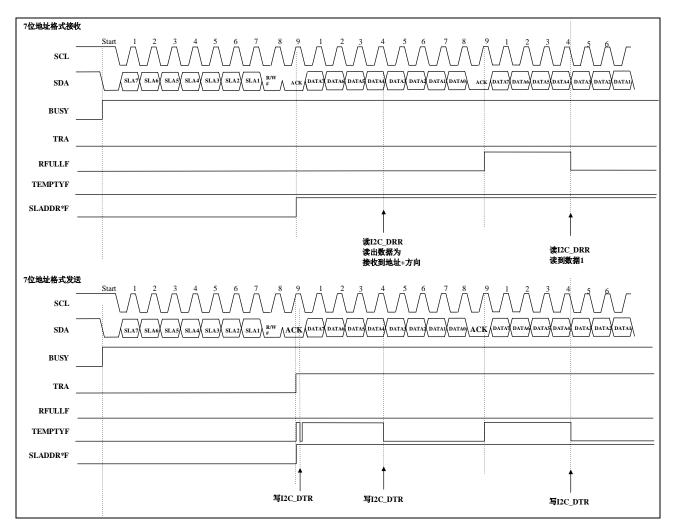

|   |       | 7 位地址格式的从机发送模式时序图(例)         |     |

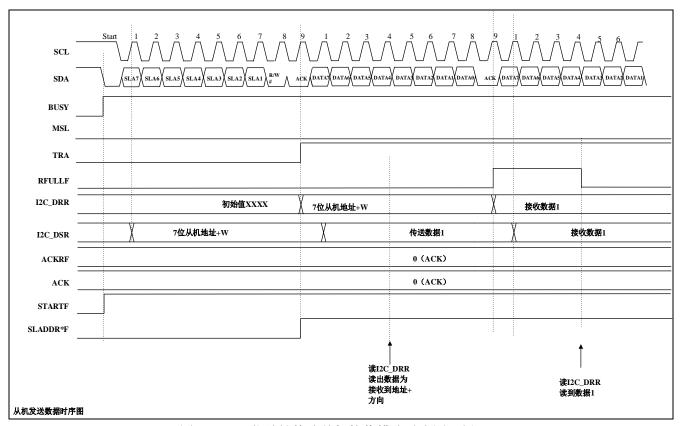

|   |       | 7位地址格式从机接收模式时序图(例)           |     |

|   | 17-9  | SCL 同步时序                     |     |

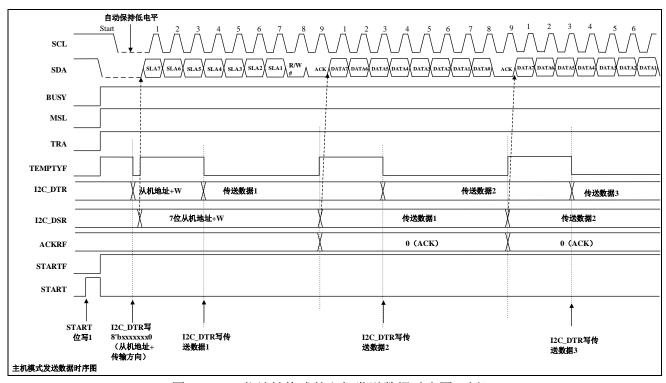

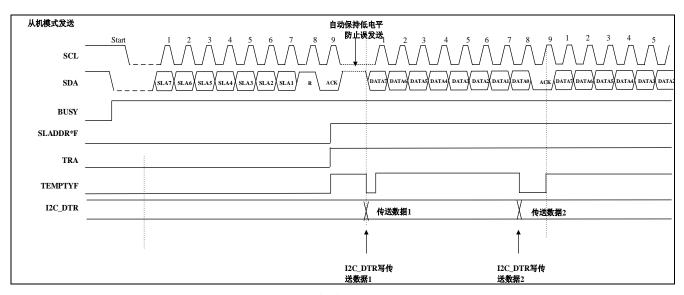

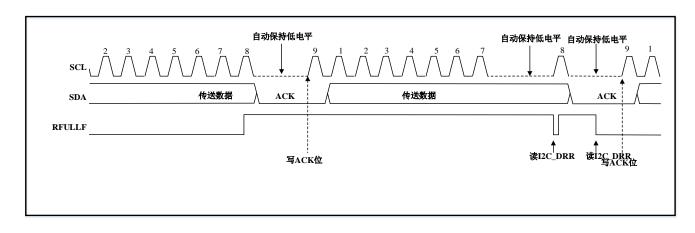

|   | 17-10 | 从机发送时序图(1)                   |     |

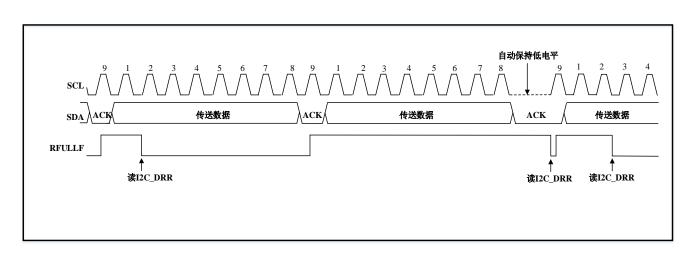

|   | 17-11 |                              |     |

| 夂 | 17 12 | 选择 7 位州州权式时的时序               | 200 |

#### XHSC 小华半导体 XIAOHUA SEMICONDUCTOR

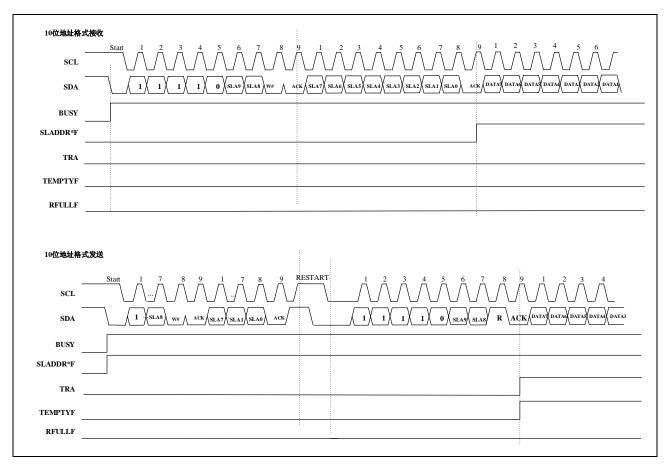

| 图 | 17-13 | 选择 10 位地址格式时的时序 | . 300 |

|---|-------|-----------------|-------|

| 图 | 17-14 | 数字滤波电路框图        | . 310 |

| 图 | 18-1  | 系统框图            | . 331 |

| 图 | 18-2  | 主机模式结构          | . 335 |

| 图 | 18-3  | 三线式时钟同步运行       | . 335 |

| 图 | 18-4  | 数据格式            | . 337 |

| 图 | 18-5  | 数据传送格式图(CPHA=0) |       |

| 图 | 18-6  | 数据传送格式(CPHA=1)  | . 340 |

| 图 | 18-7  | 全双工同步串行通信       | . 341 |

| 图 | 18-8  | 只进行发送通信         |       |

| 图 | 18-9  | 奇偶校验流程          | . 351 |

| 图 | 18-10 | 过载错误处理          |       |

| 图 | 18-11 | 奇偶校验错误          | . 354 |

| 图 | 19-1  | CRC 应用示意图       | . 365 |

| 冬 | 20-1  | 调试控制系统          | . 370 |

# 简介(Overview)

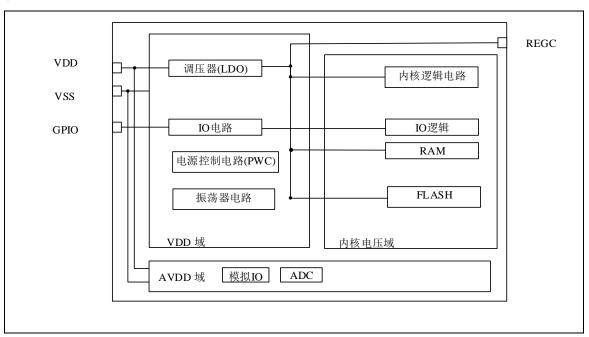

HC32F120 系列是基于 ARM® Cortex®-M0+ 32-bit RISC CPU,最高工作频率 48MHz 的高性能 MCU。Cortex-M0+内核支持 2 级流水线,运算能力达到 0.95 Dhrystone MIPS/MHz,硬件调试 电路支持 2-pin 的 SWD 调试界面。

HC32F120 系列集成了片上存储器,包括最大 64KB 的 Flash,最大 4KB 的 SRAM。集成了 Flash 访问预取指加速单元(Prefetch),提高 Flash 访问效率。支持外设间事件相互触发,可以显著降低 CPU 的事务处理负荷。

HC32F120 系列集成了丰富的外设功能。包括最大 12 通道的 12bit 1MSPS ADC, 8 个多功能 16bit Timer(TimerB)支持输入捕捉、输出比较、PWM 输出, 1 个 16bit Timer(Timer0)支持 异步计数, 1 个 I2C 通信接口, 1 个 SPI 通信接口, 4 个 USART 通信接口, 其中 1 个 USART 支持 LIN 通信功能,

HC32F120 系列支持宽电压范围 (2.7-5.5V), 宽温度范围 (-40-85℃) 和低功耗模式。

# 典型应用

HC32F120 系列提供 Pin Pitch 0.8mm 的 44pin、32pin 的 LQFP 封装,适用于家电控制、智能硬件等领域。

### 关于本手册

本手册主要介绍芯片的功能、操作事项和使用方法。关于芯片的规格,请参阅对应的"数据手册"。

# 1 存储器映射(Memory Mapping)

# 1.1 存储器映射

该 MCU 支持 4GB 的线性地址空间,地址从 0000 0000h 到 FFFF FFFFh,其中包含程序和数据。详细存储器映射请参阅下表。

| 存储器分   | 存储器分类*1             |            | 结束地址       | 空间大小   | 模块*2        | 保护*3 | 说明                |

|--------|---------------------|------------|------------|--------|-------------|------|-------------------|

| 系统     |                     | 0xE0100000 | 0xFFFFFFFF | 511MB  | Reserved    |      | 自定义空间             |

|        | *1 <del>*    </del> | 0xE00FF000 | 0xE00FFFFF | 4KB    | ROMTABLE    |      |                   |

|        | 私有外                 | 0xE0042400 | 0xE00FEFFF | 755KB  |             |      |                   |

|        | 设<br>外部总            | 0xE0042000 | 0xE00423FF | 1KB    |             |      |                   |

|        | が 市 心<br>・ 线        | 0xE0041000 | 0xE0041FFF | 4KB    |             |      |                   |

|        | 54                  | 0xE0040000 | 0xE0040FFF | 4KB    |             |      |                   |

|        |                     | 0xE000F000 | 0xE003FFFF | 196KB  |             |      |                   |

|        | 私有外                 | 0xE000E000 | 0xE000EFFF | 4KB    | SCS         |      | 系统控制空间 NVIC 等     |

|        | 设                   | 0xE0003000 | 0xE000DFFF | 44KB   |             |      |                   |

|        | 内部总                 | 0xE0002000 | 0xE0002FFF | 4KB    | FPB         |      |                   |

|        | 线                   | 0xE0001000 | 0xE0001FFF | 4KB    | DWT         |      |                   |

|        |                     | 0xE0000000 | 0xE0000FFF | 4KB    |             |      |                   |

| 外部设备   | -                   | 0xA0000000 | 0xDFFFFFFF | 1024MB | Reserved    |      |                   |

| 外部 RAM |                     | 0x60000000 | 0x9FFFFFFF | 1024MB | Reserved    |      |                   |

| 外设     | -                   | 0x44000000 | 0x5FFFFFFF | 448MB  | Reserved    |      |                   |

|        |                     | 0x42000000 | 0x43FFFFFF | 32MB   | PeriBitBand |      | CPU 以外主机 Reserved |

|        |                     | 0x40100000 | 0x41FFFFFF | 31MB   | Reserved    |      |                   |

|        |                     | 0x40020000 | 0x400FFFFF | 896KB  | Reserved    |      |                   |

|        | AHB                 | 0x40015800 | 0x4001FFFF | 42KB   | BLANK       |      |                   |

|        |                     | 0x40015400 | 0x400157FF | 1KB    | CRC         |      |                   |

|        |                     | 0x40015000 | 0x400153FF | 1KB    | DBGC        |      |                   |

|        |                     | 0x40014800 | 0x40014FFF | 1KB    | BLANK       |      |                   |

|        |                     | 0x40014400 | 0x400147FF | 1KB    | CMU         |      |                   |

|        |                     | 0x40014000 | 0x400143FF | 1KB    | EMU         |      |                   |

|        |                     | 0x40013800 | 0x40013FFF | 2KB    | GPIO        |      | 开始 1K 与 FASTIO 共用 |

|        |                     | 0x40013400 | 0x400137FF | 1KB    | BLANK       |      |                   |

|        |                     | 0x40013000 | 0x400133FF | 1KB    | BLANK       |      |                   |

|        |                     | 0x40012800 | 0x40012FFF | 2KB    | BLANK       |      |                   |

|        |                     | 0x40012400 | 0x400127FF | 1KB    | BLANK       |      |                   |

|        |                     | 0x40012000 | 0x400123FF | 1KB    | BLANK       |      |                   |

|        |                     | 0x40011000 | 0x40011FFF | 4KB    | INTC        |      |                   |

|        |                     | 0x40010000 | 0x40010FFF | 4KB    | BLANK       |      |                   |

| 存储器分类*1 | 开始地址       | 结束地址       | 空间大小 | 模块*2    | 保护*3 | 说明 |

|---------|------------|------------|------|---------|------|----|

| APB     | 0x4000D800 | 0x4000FFFF | 10KB | BLANK   |      |    |

|         | 0x4000D400 | 0x4000D7FF | 1KB  | BLANK   |      |    |

|         | 0x4000D000 | 0x4000D3FF | 1KB  | BLANK   |      |    |

|         | 0x4000CC00 | 0x4000CFFF | 1KB  | SWDT    |      |    |

|         | 0x4000C800 | 0x4000CBFF | 1KB  | BLANK   |      |    |

|         | 0x4000BC00 | 0x4000C7FF | 3KB  | BLANK   |      |    |

|         | 0x4000B800 | 0x4000BBFF | 1KB  | ADC     |      |    |

|         | 0x40009800 | 0x4000B7FF | 8KB  | BLANK   |      |    |

|         | 0x40009400 | 0x400097FF | 1KB  | TIMB_8  |      |    |

|         | 0x40009000 | 0x400093FF | 1KB  | TIMB_7  |      |    |

|         | 0x40008C00 | 0x40008FFF | 1KB  | TIMB_6  |      |    |

|         | 0x40008800 | 0x40008BFF | 1KB  | TIMB_5  |      |    |

|         | 0x40008400 | 0x400087FF | 1KB  | TIMB_4  |      |    |

|         | 0x40008000 | 0x400083FF | 1KB  | TIMB_3  |      |    |

|         | 0x40007C00 | 0x40007FFF | 1KB  | TIMB_2  |      |    |

|         | 0x40007800 | 0x40007BFF | 1KB  | TIMB_1  |      |    |

|         | 0x40007400 | 0x400077FF | 1KB  | BLANK   |      |    |

|         | 0x40007000 | 0x400073FF | 1KB  | BLANK   |      |    |

|         | 0x40006C00 | 0x40006FFF | 1KB  | BLANK   |      |    |

|         | 0x40006800 | 0x40006BFF | 1KB  | BLANK   |      |    |

|         | 0x40006400 | 0x400067FF | 1KB  | BLANK   |      |    |

|         | 0x40006000 | 0x400063FF | 1KB  | BLANK   |      |    |

|         | 0x40005C00 | 0x40005FFF | 1KB  | BLANK   |      |    |

|         | 0x40005800 | 0x40005BFF | 1KB  | TIM0    |      |    |

|         | 0x40004C00 | 0x400057FF | 3KB  | BLANK   |      |    |

|         | 0x40004800 | 0x40004BFF | 1KB  | I2C     |      |    |

|         | 0x40003C00 | 0x400047FF | 1KB  | BLANK   |      |    |

|         | 0x40003800 | 0x40003BFF | 1KB  | SPI     |      |    |

|         | 0x40002800 | 0x400037FF | 4KB  | BLANK   |      |    |

|         | 0x40002400 | 0x400027FF | 1KB  | USART_4 |      |    |

|         | 0x40002000 | 0x400023FF | 1KB  | USART_3 |      |    |

|         | 0x40001C00 | 0x40001FFF | 1KB  | USART_2 |      |    |

|         | 0x40001800 | 0x40001BFF | 1KB  | USART_1 |      |    |

|         | 0x40001000 | 0x400017FF | 2KB  | BLANK   |      |    |

|         | 0x40000C00 | 0x40000FFF | 1KB  | AOS     |      |    |

|         | 0x40000800 | 0x40000BFF | 1KB  | EFM     |      |    |

|         | 0x40000400 | 0x400007FF | 1KB  | BLANK   |      |    |

|         | 0x40000000 | 0x400003FF | 1KB  | CTC     |      |    |

| 存储器分类*1 |       | 开始地址       | 结束地址       | 空间大小   | 模块*2        | 保护*3 | 说明                |

|---------|-------|------------|------------|--------|-------------|------|-------------------|

| SRAM    | SRAM  | 0x24000000 | 0x3FFFFFFF | 448MB  | Reserved    |      |                   |

|         |       | 0x22000000 | 0x23FFFFFF | 32MB   | SRAMBitBand |      | CPU 以外主机 Reserved |

|         |       | 0x20100000 | 0x21FFFFFF | 31MB   | Reserved    |      |                   |

|         |       | 0x20001000 | 0x200FFFFF | 1020KB | Reserved    |      |                   |

|         |       | 0x20000000 | 0x20000FFF | 4KB    | SRAM        | 保护   |                   |

| CODE    | FLASH | 0x00100000 | 0x1FFFFFF  | 511MB  | Reserved    |      |                   |

|         |       | 0x00010000 | 0x000FFFFF | 960KB  | Reserved    |      |                   |

|         |       | 0x00000000 | 0x0000FFFF | 64KB   | Flash       |      |                   |

表 1-1 存储器映射

- \*1 请参考 ARM Cortex-M0+说明手册 存储器系统

- \*2 Reserved:访问总线会引起总线错误;BLANK:写访问无视,读0。

- \*3 保护功能请参考 PWC 章节。

#### 1.2 位段空间

Cortex™-M0+ 存储器映射包括两个位段区域。这些区域将存储器别名区域中的每个字映射到存储器位段区域中的相应位。在别名区域写入字时,相当于对位段区域的目标位执行读-修改-写操作。

在该 MCU 中,外设寄存器和 SRAM 均映射到一个位段区域,这样可实现单个位段的 读写操作。这些操作仅适用于 Cortex™-M0+ 访问,对于其它总线主接口(如 DMA)无效。

在位段区域,每个字由位段别名地址区域 32 个字的 LSB 表示。实际情况是,当访问位段别名地址时,该地址就会被重映射到位段地址。对于读操作,字被读出且选定位的位置被移到读返回数据的 LSB。对于写操作,待写的位数据被移到所需的位置,然后执行读-修改-写操作。

可以进行位段操作的存储器区域有两个:

0x20000000~0x200FFFFF(SRAM, 1MB)

0x40000000~0x400FFFFF(外设,1MB)

举例说明如下:

- 1) 将地址 0x20000000 设置为 0x3355AACC。

- 2) 读地址 0x22000008。本次读访问被映射为到 0x20000000 的读访问,返回值为 1 (0x3355AACC 的 bit[2])。

- 3) 将 0x22000008 写为 0。本次写访问被重映射为到地址 0x20000000 的读-修改-写。数值 0x3355AACC 被从寄存器中读出来,清除第 2 位后,结果 0x3355AAC8 被写入地址 0x20000000。

- 4) 现在读取 0x20000000, 这样会得到返回值 0x3355AAC8(bit[2]被清除)。

- 5) 在访问位段别名地址时,只会用到数据的 LSB(bit[0])。另外,对位段别名区域的访问不应该是非对齐的。若非对齐访问在位段区域内执行,结果是不可预测的。

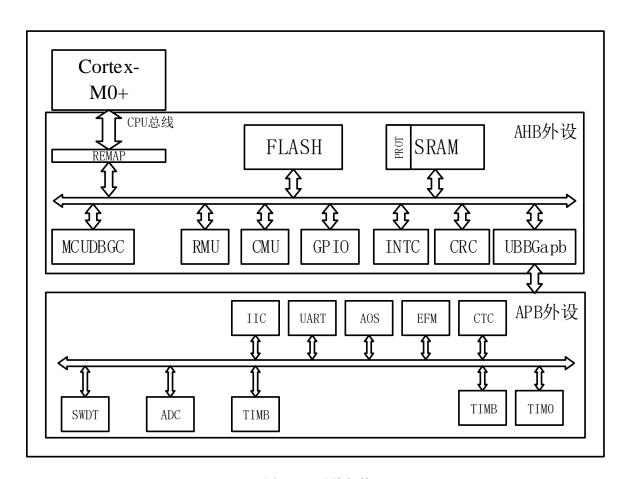

# 2 总线架构(BUS)

### 2.1 概述

主系统由 32 位 AHB 总线矩阵构成,可实现以下主机总线和从机总线的互连:

- 主机总线

- Cortex-M0+内核 CPU 总线

- 。 Cortex-M0+内核总线, CPU 通过该总线获取指令与数据。访问对象是包含内部存储器与外设。

- 从机总线

- AHB 外设总线

- APB 外设总线

### 2.2 总线架构

图 2-1 总线架构

# 2.3 总线功能

总线负责实现主机对从机的读写访问。通过总线可以实现对 AHB 与 APB 外设的访问。APB 外设通过总线桥与 AHB 连接。

# 3 复位控制(RMU)

# 3.1 简介

芯片配置了8种复位方式。

- 上电复位(POR)

- RESET 引脚复位(RESET)

- 低电压检测复位(LVD)

- 专用看门狗复位(SWDTR)

- 软件复位(SRST)

- M0+ Lockup 复位

- 外部高速振荡器异常停振复位(XTALER)

- RAM 奇偶校验复位

# 3.2 复位方式和复位标志位

复位方式及产生条件如表 3-1 所示。

| 复位方式          | 产生条件                            |

|---------------|---------------------------------|

| 上电复位          | VDD上电                           |

| RESET 引脚复位    | RESET 引脚输入低电平                   |

| 低电压检测复位       | VDD 电压降至低于 VLVD 电压              |

| 专用看门狗复位       | 看门狗定时器产生刷新错误或者溢出错误              |

| 软件复位          | 设置复位寄存器位(ARM 寄存器                |

|               | AIRCR.SYSRESETREQ 位)            |

| RAM 奇偶校验错误复位  | RAM 奇偶校验错误产生的复位                 |

| M0+ Lockup 复位 | 当 Cortex-M0+ 遇到严重的异常时,它会将自己的 PC |

|               | 指针停在当前地址处,并锁死自己,在几个时钟周期         |

|               | 延时之后复位整个芯片。                     |

| 外部高速振荡器异常停振复位 | 外部高速振荡器异常停振时产生的复位               |

表 3-1 复位方式及产生条件

发生复位时,芯片根据复位方式将对应的复位标志位进行置位,复位标志位如表 3-2 所示。比如发生引脚复位,引脚复位标志位 PINRF 被置 1,在 PINRF 被置位后通过写 CLRF 可以将 PINRF 清零。

| 复位标志                              | 复位方式 |      |         |         |      |            |               |               |

|-----------------------------------|------|------|---------|---------|------|------------|---------------|---------------|

|                                   | 上电复位 | 引脚复位 | 低电压检测复位 | 专用看门狗复位 | 软件复位 | RAM 奇偶校验复位 | M0+ Lockup 复位 | 外部高速振荡器异常停振复位 |

| 上电复位标志(RSTF0.PORF)                | √    | _    | _       | _       | _    | _          | _             | _             |

| 引脚复位标志(RSTF0.PINRF)               | _    | √    | _       | _       | _    | _          | _             | _             |

| 低电压检测复位标志(RSTF0.LVIRFRSTF0.LVIRF) | _    | _    | √       | _       | _    | _          | _             | _             |

| 专用看门狗复位标志(RSTF0.WDRF)             | _    | _    | _       | √       | _    | _          | _             | _             |

| 软件复位标志(RSTF0.SWRF)                | _    | _    |         |         | √    | _          |               | _             |

| RAM 奇偶校验错误复位(RSTF0.RPERF)         | _    | _    | _       |         | _    | √          | _             | _             |

| M0+ Lockup 复位(RSTF0.CPULKUPRF)    | _    | _    |         |         | _    |            | <b>√</b>      | _             |

| 外部高速振荡器异常停振复位(RSTF0.XTALERF)      | _    | _    |         |         | -    | _          | _             | √             |

√: 置位 一: 不变

表 3-2 复位方式及复位标志

### 3.3 复位时序

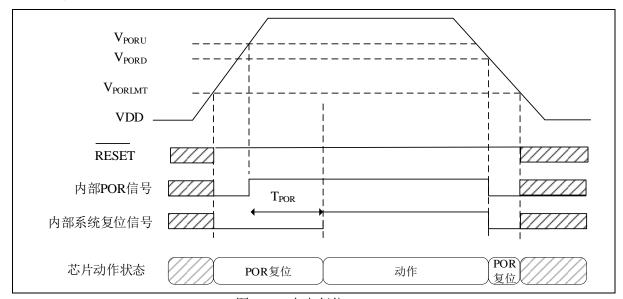

#### 3.3.1 上电复位

上电复位是上电复位电路引起的内部复位,时序如图 3-1。在将 RESET 引脚置为高电平的状态下接通电源,就产生上电复位。VDD 电压高于 VPORU 后经过一定的时间(TPOR)之后芯片内部复位解除,CPU 开始执行代码。产生上电复位时,上电复位标志 RMU\_RSTF0.PORF 被置位。上电复位的详细说明请参照【5.3.1 上电复位/掉电复位动作说明】。

图 3-1 上电复位

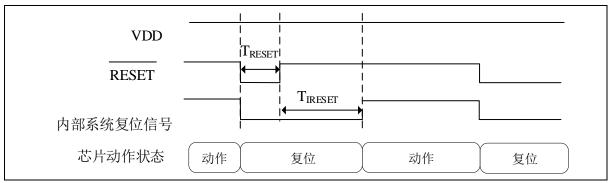

### 3.3.2 **RESET** 引脚复位

引脚复位是 RESET 引脚被驱动为低电平引起的复位,复位时序如图 3-2。RESET 管脚维持 TRESET 宽度以上的低电平后,经过一定的内部复位时间(TIRESET),解除内部复位。

产生 RESET 引脚复位时,引脚复为标志 RMU RSTF0.PINRF 被置位。

图 3-2 RESET 复位时序

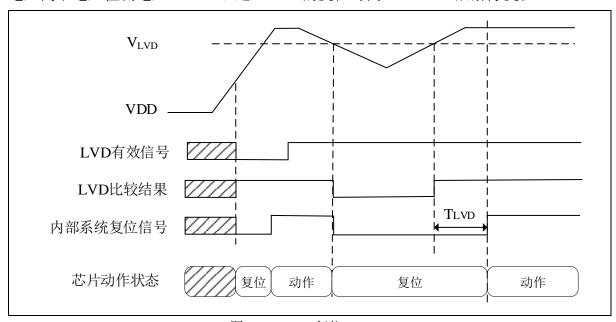

#### 3.3.3 低电压检测复位

低电压检测复位是低电压检测电路引起的内部复位,时序如图 3-3。LVD 设置为复位使能后,如果 VDD 电压低于电压检测电压 VLVD,RMU\_RSTF0.LVRF被置位。当 VDD 电压高于电压检测电压 VLVD 经过 VLVD 的复位时间(TLVD)后解除复位。

图 3-3 LVD 复位

#### 3.3.4 专用看门狗复位

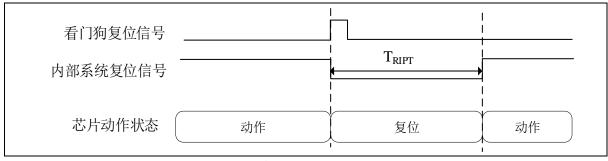

专用看门狗复位是看门狗定时器引起的内部复位,复位时序如图 3-4。

设定专用看门狗复位有效后,在看门狗定时器产生下溢或者在不允许刷新期间进行写操作时产生专用看门狗复位。专用看门狗复位将 RMU\_RSTF0.WDRF 置位。产生专用看门狗复位后,经过内部复位时间 TRIPT 之后,芯片解除复位。

有关专用看门狗复位的详细内容,请参考【看门狗计数器(SWDT)】。

图 3-4 专用看门狗复位

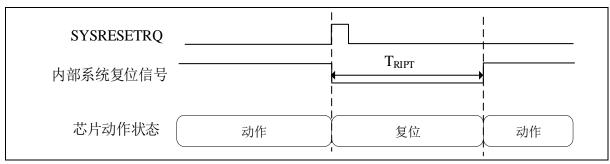

#### 3.3.5 软件复位

通过写 ARM 寄存器 AIRCR 的 SYSRESETREQ 位产生软件复位。产生软件复位时, RMU RSTF0.SWRF 位被置位。经过内部复位时间 TRIPT 之后, 芯片解除复位。

图 3-5 软件复位

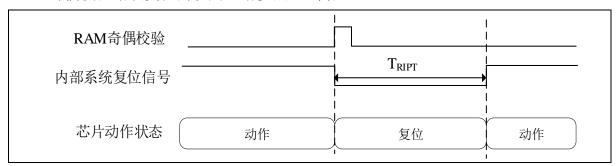

#### 3.3.6 RAM 奇偶校验复位

RAM 奇偶校验发生错误时,产生 RAM 奇偶校验复位,时序如图 3-6。RAM 奇偶校验错误将 RMU\_RSTF0.RAMPERF 置位。经过内部复位时间 TRIPT 之后,芯片解除复位。RAM 奇偶校验错误复位的设定,请参照【8 内置 SRAM(SRAM)】。

图 3-6 RAM 奇偶校验复位

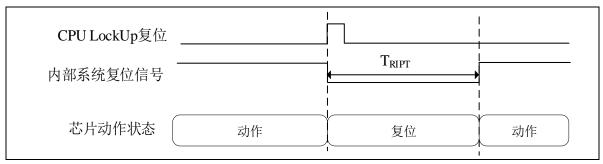

# 3.3.7 M0+ Lockup 复位

当 Cortex-M0+ 遇到严重的异常时,它会将自己的 PC 指针停在当前地址处,并锁死自己,并在几个时钟周期延时之后复位整个芯片,时序如图 3-7。M0+ Lockup 复位将RSTF0.CPULKUPRF置位。经过内部复位时间 T<sub>RIPT</sub>之后,芯片解除复位。

图 3-7 M0+ Lockup 复位

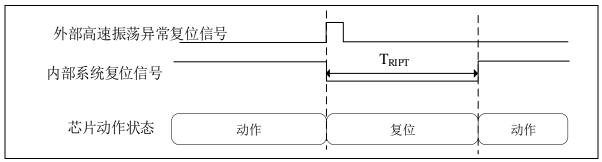

#### 3.3.8 外部高速振荡器异常停振复位

当芯片的震荡停止检测模块有效并且复位使能后,如果发生外部高速振荡器异常停振时,产生外部高速振荡器异常停振复位,RMU\_RSTF0.XTALERF被置位。经过内部复位时间 TRIPT 之后,芯片解除复位。

外部高速振荡器异常停振复位的设定,请参照【4.5.2 外部高速振荡器故障检测】。

图 3-8 外部高速振荡异常复位

### 3.3.9 复位方式的判断

根据 RMU\_RSTF0 的复位标志可以判断复位方式。当两个或者两个以上复位同时产生时,可能会产生多个复位标志。RMU\_RSTF0 中的 MULTIRF 位为 1 时表示发生多个复位。在读 RMU\_RSTF0 之后,通过置位 CLRF 位能够将所有的复位标志清 0。

# 3.4 寄存器说明

寄存器一览如表 3-3 所示。

BASE ADDR: 0x40014100

| 寄存器名    | 符号        | 偏移地址 | 位宽 | 复位值            |

|---------|-----------|------|----|----------------|

| 复位状态寄存器 | RMU_RSTF0 | 0x00 | 16 | 根据不同的复位方式复位值不同 |

表 3-3 RMU 寄存器一览

# 3.4.1 复位标志寄存器 0 (RMU\_RSTF0)

复位值: 0xXXXXh(根据复位方式不同,复位值不同)

| b15  | b14     | b13     | b12          | b11 | b10        | b9    | b8        | b7   | b6   | b5         | b4  | b3         | b2   | b1    | ь0   |

|------|---------|---------|--------------|-----|------------|-------|-----------|------|------|------------|-----|------------|------|-------|------|

| CLRF | MULTIRF | XTALERF | CPULKUPRF    | -   | RAMPERF    | -     | SWRF      | -    | -    | WDRF       | -   | -          | LVRF | PINRF | PORF |

|      |         |         |              |     |            |       |           |      |      |            |     |            |      |       |      |

| 位    | 左 标记    | ļ       | 位名           |     | 功能         |       |           |      |      |            |     |            |      |       | 读写   |

| b15  | CLRF    |         | 清除复位         |     | 软件置1,用于    | 清除    | 复位标志      | 位。   |      |            |     |            |      |       | R/W  |

|      |         |         | 标志           |     | 读出时为0。置    | 位动    | 作必须在      | 读取R  | RMU_ | RSTF0之     | 后进往 | <b></b> 元。 |      |       |      |

|      |         |         |              |     | 0: 无操作     |       |           |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 1: 清零复位标   | 志     |           |      |      |            |     |            |      |       |      |

| b14  | MULTIR  | F       | 2个以上复位       |     | 发生两个及两个    | 个以上   | 复位时,      | 由硬   | 件置   | <u>分</u> 。 |     |            |      |       | R/W  |

|      |         |         | 发生标志位        |     | 通过置位CLRF   | 清零    |           |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 0: 未发生两个   | 及两    | 个以上复      | 位    |      |            |     |            |      |       |      |

|      |         |         |              |     | 1: 发生两个及   | 两个    | 以上复位      | 时    |      |            |     |            |      |       |      |

| b13  | XTALER  | RF.     | 外部高速振荡器      | 异常  | 发生外部高速抗    | 辰荡器   | 异常停振      | 夏位   | 时,   | 由硬件置       | 位。  |            |      |       | R/W  |

|      |         |         | 停振复位标志       |     | 通过置位CLRF   | 清零    | >         |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 0: 未发生外部   | 高速:   | 振荡器异      | 常停捷  | 辰复位  | Ĺ          |     |            |      |       |      |

|      |         |         |              |     | 1: 发生外部高   | 速振    | 荡器异常      | 停振多  | 夏位   |            |     |            |      |       |      |

| b12  | CPULKU  | JPRF    | M0+ Lockup复位 | 复位标 | 发生M0+ Lock | up复信  | 过时,由码     | 更件置  | 位。   |            |     |            |      |       | R/W  |

|      |         |         | 志            |     | 通过置位CLRF   | 清零    | >         |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 0: 未发生M0+  | Lock  | up复位      |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 1:发生M0+L   | ockup | 复位        |      |      |            |     |            |      |       |      |

| b11  | -       |         | -            |     | -          |       |           |      |      |            |     |            |      |       | R/W  |

| b10  | RAMPE   | RF      | RAM奇偶校验错     | 误复位 | 发生RAM奇偶    | 校验铂   | 昔误复位田     | 付, 由 | 硬件   | 置位。        |     |            |      | R     | /W   |

|      |         |         | 标志           |     | 通过置位CLRF   | 清零    | •         |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 0:未发生RAM   | 1奇偶   | 校验错误      | 复位   |      |            |     |            |      |       |      |

|      |         |         |              |     | 1:发生RAM奇   | 予偶校   | 验错误复      | 位    |      |            |     |            |      |       |      |

| Ь9   | -       |         | -            |     | -          |       |           |      |      |            |     |            |      | R     | /W   |

| b8   | SWRF    |         | 软件复位标志       |     | 发生软件复位多    | 夏位时   | ,由硬件      | 丰置位  | . 0  |            |     |            |      | R     | /W   |

|      |         |         |              |     | 通过置位CLRF   | 清零    | >         |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 0: 未发生软件   | 复位    | 复位        |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 1: 发生软件复   | 位复    | <u>'À</u> |      |      |            |     |            |      |       |      |

| b7   |         |         |              |     |            |       |           |      |      |            |     |            |      | R     | /W   |

| b6   | -       |         | -            |     | -          |       |           |      |      |            |     |            |      | R     | /W   |

| b5   | WDRF    |         | 专用看门狗复位      |     | 发生专用看门犭    | 句复位   | 时,由硬      | 更件置  | 位。   |            |     |            |      |       | R/W  |

|      |         |         | 标志           |     | 通过置位CLRF   | 清零    | >         |      |      |            |     |            |      |       |      |

|      |         |         |              |     | 0: 未发生专用   | 看门    | 佝复位       |      |      |            |     |            |      |       |      |

|      |         |         |              |     |            |       |           |      |      |            |     |            |      |       |      |

|    |       |         | 1: 发生专用看门狗复位      |     |

|----|-------|---------|-------------------|-----|

| b4 |       |         |                   | R/W |

| b3 |       |         |                   | R/W |

| b2 | LVRF  | 低电压检测复位 | 发生低电压检测复位时,由硬件置位。 | R/W |

|    |       |         | 通过置位CLRF清零。       |     |

|    |       |         | 0: 未发生低电压检测复位     |     |

|    |       |         | 1: 发生低电压检测复位      |     |

| bl | PINRF | RESET引脚 | 发生引脚复位时,由硬件置位。    | R/W |

|    |       | 复位标志    | 通过置位CLRF清零。       |     |

|    |       |         | 0: 未发生RESET复位     |     |

|    |       |         | 1: 发生RESET复位      |     |

| b0 | PORF  | 上电复位    | 发生上电复位时,由硬件置位。    | R/W |

|    |       | 标志      | 通过置位CLRF清零。       |     |

|    |       |         | 0: 未发生上电复位        |     |

|    |       |         | 1: 发生上电复位         |     |

### 4 时钟控制器(CMU)

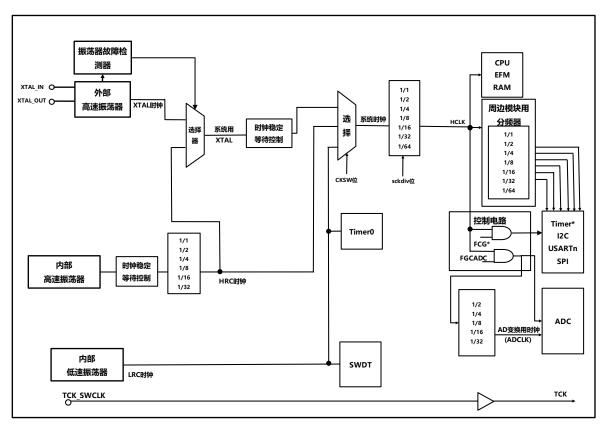

### 4.1 简介

时钟控制单元提供了一系列频率的时钟功能,包括:一个外部高速振荡器、一个内部高速振荡器、一个内部低速振荡器、时钟预分频器和时钟门控电路。

AHB、APB 和 Cortex-M0+时钟都源自系统时钟,系统时钟的源可选择 3 个时钟源:

- 1) 外部高速振荡器(XTAL)

- 2) 内部高速振荡器(HRC)

- 3) 内部低速振荡器(LRC)

系统时钟的最大运行时钟频率可以达到 48MHz。

对于每一个时钟源,在未使用时都可以单独打开和关闭,以降低功耗。

### 4.2 系统框图

### 4.2.1 系统框图

图 4-1 时钟系统框图

# 4.3 时钟源规格

各时钟源的主要特性如下表所示。

| 时钟源           | 规格                                      |  |  |  |

|---------------|-----------------------------------------|--|--|--|

| 外部高速振荡器(XTAL) | 晶振的频率范围: 4~20MHz                        |  |  |  |

|               | 外部时钟输入:最高 20MHz                         |  |  |  |

|               | 振荡器故障检测功能                               |  |  |  |

| 内部高速振荡器(HRC)  | 频率: 48MHz、32MHz、24MHz、16MHz、12MHz、8MHz、 |  |  |  |

|               | 6MHz、4MHz、3MHz、2MHz、1.5MHz、1MHz。通过      |  |  |  |

|               | ICG0.HRCFREQS 位配置。                      |  |  |  |

| 内部低速振荡器 (LRC) | 频率: 32.768kHz                           |  |  |  |

|               | 可用作 SWDT、Timer0 的计数时钟                   |  |  |  |

# 4.4 工作时钟规格

| 时钟      | 作用范围                        | 规格            |

|---------|-----------------------------|---------------|

| HCLK    | CPU、AOS、CRC、EFM(主闪存)、       | 最高频率 48MHz    |

|         | SRAM、GPIO、INTC、USARTn       |               |

|         | (n=1~4) 、SPI、Timer0、TimerBn |               |

|         | (n=1~8)、I2C、SWDT(控制逻辑)、     |               |

|         | ADC(控制逻辑)、CTC               |               |

| ADCLK   | AD 变换用时钟                    | 最高频率 32MHz    |

| STICCLK | CPU 的 SysTickTimer 计数器用时钟,时 | 频率 32.768kHz  |

|         | 钟源为 LRC                     |               |

| SWDTCLK | SWDT 计数器用时钟                 | 频率 32.768K Hz |

| TCK     | JTAG 用时钟                    | 最高频率 20MHz    |

表 4-1 各个内部时钟的规格

#### 4.5 晶振电路

#### 4.5.1 外部高速振荡器

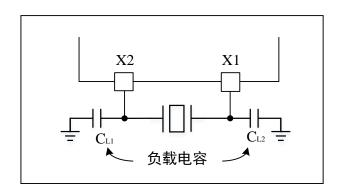

#### 4.5.1.1 振荡器模式

外部高速振荡器可为系统时钟提供更为精确时钟源。频率范围 4~20MHz。

XTAL 通过 CMU XTALCR 的 XTALSTP 位打开和关闭。

CMU\_OSCSTBSR 的 XTALSTBF 标志位指示外部高速振荡器是否稳定,稳定时间通过寄存器 CMU\_XTALSTBCR 配置。CMU\_XTALSTBCR 设定的稳定时间一定要大于等于晶振厂商要求的稳定时间。

晶振的电路常数因晶振和安装电路的寄生电容而不同,因此必须和晶振厂商仔细商谈后决定。振荡器的各种特性与用户的电路板设计密接相关,晶振和负载电容必须尽可能地靠近振荡器的引脚,以尽量减小输出失真和起振稳定时间。负载电容值必须根据所选振荡器的不同做适当调整。在振荡电路附近不能通过信号线,否则就可能因电感而不能正常振荡。

图 4-2 外部高速振荡器连接事例

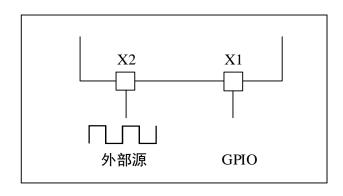

### 4.5.1.2 时钟输入模式

时钟输入模式下,必须提供外部时钟源。此模式通过 CMU\_XTALCFGR 的 XTALMS 位和 CMU\_XTALCR 的 XTALSTP 位置"1"进行选择。必须使用占空比约为 50%的外部时钟信号来驱动 X2 引脚。此时 X1 引脚可根据寄存器设定配置成 GPIO。外部时钟输入的连接例如下图所示。

图 4-3 外部时钟输入的连接事例图

#### 4.5.2 外部高速振荡器故障检测

振荡器故障检测是检测外部高速振荡器(XTAL)振荡是否正常。

通过寄存器 CMU XTALSTDCR 的 XTALSTDE 位打开或关闭。

复位解除后,外部高速振荡器停止振荡,外部高速振荡器故障检测功能无效。要将外部高速振荡器故障检测功能置为有效时,必须使外部高速振荡器振荡,并且在等到外部高速振荡器稳定即 CMU\_OSCSTBSR.XTALSTBF 为 1,通过寄存器 CMU\_XTALSTDCR 的 XTALSTDE 位打开。

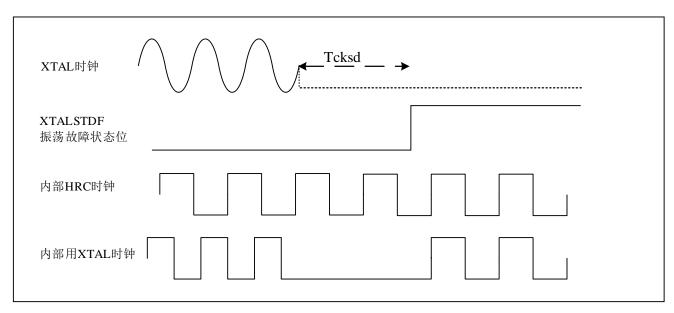

因为振荡器故障检测是检测外部因素导致的振荡器异常振荡,所以要通过软件使外部高速振荡器停止振荡或者转移到停止模式和掉电模式时,将振荡器振荡故障检测功能无效。如果外部高速振荡器发生故障,动作波形如下图所示。操作流程参照检测到 XTAL 故障检测动作。

图 4-4 外部高速振荡器故障检测例

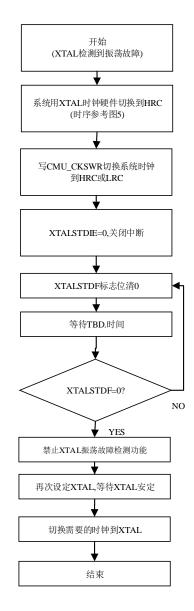

### 4.5.2.1 检测到 XTAL 故障检测动作

当检测到外部高速振荡器振荡故障时,如果系统时钟选择外部高速振荡器作为系统时钟,系统时钟会自动切换到 HRC。

系统时钟选择成 XTAL,检测到 XTAL 故障时,动作例如下图所示。

图 4-5 系统时钟选择 XTAL, 检测到 XTAL 振荡故障例

### 4.5.2.2 检测到 XTAL 振荡故障产生中断复位

XTAL振荡故障中断可配置成可屏蔽中断或非可屏蔽中断,参考【10中断控制器(INTC)】章。

XTAL 振荡故障配置成复位时,检测到 XTAL 振荡故障,芯片产生复位,复位动作参考【3 复位控制(RMU)】章。

### 4.6 内部 RC 时钟

#### 4.6.1 HRC 时钟

HRC 时钟信号由内部高速振荡器生成,可直接用作系统时钟。HRC 的频率可由 ICG0. HRCFREQS 配置成 48MHz、32MHz、24MHz、16MHz、12MHz、8MHz、6MHz、4MHz、3MHz、2MHz、1.5MHz、1MHz。也可通过 CMU\_HRCCFGR.HRCFREQS[2:0]寄存器软件设定频率。

在复位解除后, CPU 一定以此内部高速振荡时钟开始运行。

HRC 振荡器的优点是成本较低(无需使用外部组件)。此外,其启动速度也要比 XTAL 晶振块,但即使校准后,其精度也不及外部晶振。

#### 频率校准

因为生产工艺不同,不同芯片的 RC 振荡器频率也不同,因此会对每个器件进行出厂校准,保证精度参照**数据手册电气特性中内部高速(HRC)振荡器**章节。

如果应用受到温度变化影响,则这可能也会影响到 RC 振荡器的精度。

CMU\_OSCSTBSR 中的 HRCSTBF 标志指示 HRC 是否稳定。在启动时,硬件将此位置 1 后,HRC 才可以使用。

HRC 可通过 CMU HRCCR 控制寄存器中的 HRCSTP 位打开或关闭。

#### 4.6.2 LRC 时钟

LRC 时钟信号由内部 32.768kHz 低速振荡器生成,可直接用作系统时钟。LRC 可作为低功耗时钟源在停止模式下保持运行,供 Timer0/SWDT 使用。

LRC 振荡器的启动速度快,启动后不需要等稳定即可使用。

#### 频率校准

因为生产工艺不同,不同芯片的 RC 振荡器频率也不同,因此会对每个器件进行出厂校准,保证精度参照**数据手册电气特性中内部低速(LRC)振荡器**章节。

如果应用受到电压或温度变化影响,则这可能也会影响到 RC 振荡器的速度。

LRC 可通过 CMU LRCCR 控制寄存器中的 LRCSTP 位打开或关闭。

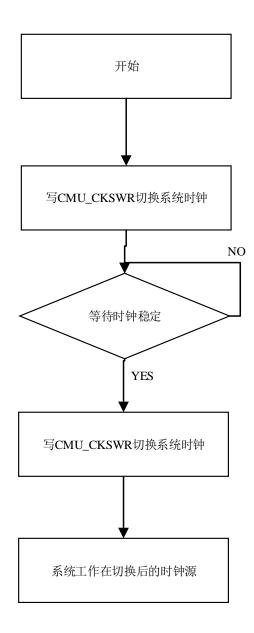

### 4.7 时钟切换步骤

在系统复位后,默认系统时钟为 HRC。通过设定寄存器 CMU\_CKSW 切换时钟源,切换步骤参照时钟源切换。只有在目标时钟源已稳定的状态下,才可以从一个时钟源切换到另一个时钟源。

时钟切换时需要正确配置 Flash/SRAM 的等待周期,防止系统时钟频率大于 Flash/SRAM 的最大动作频率。参照【7.4.1CPU 时钟和 FLASH 读取时间之间的关系】、【8 内置 SRAM (SRAM)】配置。

## 4.7.1 时钟源切换

## 4.8 时钟输出功能

### $MCO_1$ :

用户可通过可配置的预分配器(从 1 到 128)向 MCO\_1 引脚输出不同的时钟源:

- HRC 时钟

- LRC 时钟

- XTAL 时钟

- 系统时钟

所需的时钟源通过 CMU\_MCO1CFGR.MCO1SEL 位选择。

MCO\_1 输出时钟不得超过 TBD MHz(最大 I/O 速度)。

# 4.9 寄存器说明

基准地址 1:0x40014400

| 寄存器名              | 符号            | 偏移地址 | 位宽 | 复位值       |

|-------------------|---------------|------|----|-----------|

| CMU_AD时钟配置寄存器     | CMU_PERICKSEL | 0x00 | 8  | 0x00      |

| CMU_XTAL振荡故障状态寄存器 | CMU_XTALSTDSR | 0x04 | 8  | 0x00      |

| CMU_系统时钟分频配置寄存器   | CMU_SCKDIVR   | 0x08 | 8  | 0x00      |

| CMU_系统时钟源切换寄存器    | CMU_CKSWR     | 0x0C | 8  | 0x00      |

| CMU_XTAL控制寄存器     | CMU_XTALCR    | 0x10 | 8  | 0x01      |

| CMU_XTAL配置寄存器     | CMU_XTALCFGR  | 0x14 | 8  | 0x80      |

| CMU_XTAL安定配置寄存器   | CMU_XTALSTBCR | 0x15 | 8  | 0x00      |

| CMU_HRC控制寄存器      | CMU_HRCCR     | 0x18 | 8  | 0x00      |

| CMU_时钟源安定状态寄存器    | CMU_OSCSTBSR  | 0x20 | 8  | 0x00      |

| CMU_MCO1时钟输出配置寄存器 | CMU_MCO1CFGR  | 0x24 | 8  | 0x00      |

| CMU_XTAL振荡故障控制寄存器 | CMU_XTALSTDCR | 0x28 | 8  | 0x00      |

| CMU_功能时钟控制寄存器     | CMU_FCG       | 0x30 | 32 | 0xFFFFFFF |

| CMU_LRC控制寄存器      | CMU_LRCCR     | 0x3C | 8  | 0x00      |

基准地址 2: 0x40000800

| 寄存器名           | 符号          | 偏移地址   | 位宽 | 复位值       |

|----------------|-------------|--------|----|-----------|

| CMU_HRC频率配置寄存器 | CMU_HRCCFGR | 0x0282 | 8  | 由ICG0.    |

|                |             |        |    | HRCFREQS  |

|                |             |        |    | [3:0]的值决定 |

## 4.9.1 CMU XTAL 配置寄存器器(CMU\_XTALCFGR)

复位值: 0x80

| b7     | b6     | b5    | b4      | b3 | b2 | b1 | b0 |  |

|--------|--------|-------|---------|----|----|----|----|--|

| SUPDRV | XTALMS | XTALD | RV[1:0] | -  | -  | -  | -  |  |

| 位     | 标记           | 位名          | 功能                             | 读写  |

|-------|--------------|-------------|--------------------------------|-----|

| b7    | SUPDRV       | XTAL超高速驱动允许 | 0: 禁止超高速驱动                     | R/W |

|       |              |             | 1: 允许超高速驱动                     |     |

|       |              |             | 超高速驱动允许时,XTAL稳定后,无视此位设定,禁止超高速驱 |     |

|       |              |             | 动,降低功耗。                        |     |

| b6    | XTALMS       | XTAL模式选择位   | 0: 振荡器模式                       | R/W |

|       |              |             | 1: 外部时钟输入模式                    |     |

| b5~b4 | XTALDRV[1:0] | XTAL驱动能力选择  | 00: 高驱动能力(建议20MHz晶振)           | R/W |

|       |              |             | 01: 中驱动能力(建议10~20MHz晶振)        |     |

|       |              |             | 10: 小驱动能力(建议4~10MHz晶振)         |     |

|       |              |             | 11: 超小驱动能力(建议4MHz晶振)           |     |

| b3~b0 | Reserved     | -           | 读出时为 "0" ,写入时写 "0"             | R/W |

## 4.9.2 CMU XTAL 配置寄存器器(CMU\_XTALSTBCR)

| b7 | b6 | b5 | b4 | b3 | b2    | b1      | b0 |

|----|----|----|----|----|-------|---------|----|

| -  | -  | -  | -  |    | XTALS | TB[3:0] |    |

| 位     | 标记           | 位名         | 功能                                            | 读写  |

|-------|--------------|------------|-----------------------------------------------|-----|

| b7~b3 | Reserved     | -          | 读出时为"0",写入时写"0"                               |     |

| b2~b0 | XTALSTB[3:0] | XTAL稳定时间选择 | 000: 2 <sup>8</sup> *XTAL周期                   | R/W |

|       |              |            | 001: 29*XTAL周期                                |     |

|       |              |            | 010: 2 <sup>10</sup> *XTAL周期                  |     |

|       |              |            | 011: 2 <sup>11*</sup> XTAL周期                  |     |

|       |              |            | 100: 2 <sup>13</sup> *XTAL周期                  |     |

|       |              |            | 101: 2 <sup>15*</sup> XTAL周期                  |     |

|       |              |            | 110: 2 <sup>16</sup> *XTAL周期                  |     |

|       |              |            | 111: 2 <sup>17</sup> *XTAL周期                  |     |

|       |              |            | CMU_XTALCR.XTALSTP位1且CMU_OSCSTBSR.XTALSTBF位为0 |     |

|       |              |            | 的状态下配置此寄存器。                                   |     |

|       |              |            | CMU_XTALCFGR.XTALMS位选择为时钟输入模式时,无视此等待          |     |

|       |              |            | 时间。                                           |     |

## 4.9.3 CMU XTAL 控制寄存器(CMU\_XTALCR)

复位值: 0x01

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0      |

|----|----|----|----|----|----|----|---------|

| -  | -  | -  | -  | -  | -  | -  | XTALSTP |

| 位     | 标记       | 位名          | 功能              | 读写  |

|-------|----------|-------------|-----------------|-----|

| b7~b1 | Reserved | -           | 读出时为"0",写入时写"0" | R/W |

| b0    | XTALSTP  | XTAL振荡器开启停止 | 0: XTAL振荡器振荡    | R/W |

|       |          | 位           | 1: XTAL振荡器停止    |     |

#### 注意:

- XTAL 选作系统时钟源时,禁止 XTALSTP 写"1"停止 XTAL 振荡器。

## 4.9.4 CMU XTAL 振荡故障控制寄存器(CMU\_XTALSTDCR)

| b7       | b6 | b5 | b4 | b3 | b2         | b1        | b0        |

|----------|----|----|----|----|------------|-----------|-----------|

| XTALSTDE | -  | -  | -  | -  | XTALSTDRIS | XTALSTDRE | XTALSTDIE |

| 位     | 标记         | 位名          | 功能                           | 读写  |

|-------|------------|-------------|------------------------------|-----|

| b7    | XTALSTDE   | XTAL振荡故障检测功 | 0: 禁止XTAL振荡故障检测              | R/W |

|       |            | 能允许         | 1: 允许XTAL振荡故障检测              |     |

|       |            |             | 注:                           |     |

|       |            |             | 振荡器故障检测是检测外部因素导致的振荡器异常振荡,在进入 |     |

|       |            |             | 停止模式或者掉电模式前,请将振荡器振荡故障检测功能无效。 |     |

| b6~b3 | Reserved   | -           | 读出时为"0",写入时写"0"              | R/W |

| b2    | XTALSTDRIS | XTAL振荡故障复位中 | 0: XTAL振荡故障产生中断              | R/W |

|       |            | 断选择         | 1: XTAL振荡故障产生复位              |     |

| b1    | XTALSTDRE  | XTAL振荡故障复位允 | 0: 禁止XTAL振荡故障复位              | R/W |

|       |            | 许           | 1: 允许XTAL振荡故障复位              |     |

| b0    | XTALSTDIE  | XTAL振荡故障中断允 | 0: 禁止XTAL振荡故障中断              | R/W |

|       |            | 许           | 1: 允许XTAL振荡故障中断              |     |

# 4.9.5 CMU XTAL 振荡故障状态寄存器(CMU\_XTALSTDSR)

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0       |

|----|----|----|----|----|----|----|----------|

| -  | -  | -  | -  | -  | -  | -  | XTALSTDF |

| 位     | 标记                   | 位名 | 功能                         | 读写  |

|-------|----------------------|----|----------------------------|-----|

| b7~b3 | Reserved             | -  | 读出时为"0",写入时写"0"            | R/W |

| b0    | XTALSTDF XTAL振荡故障状态位 |    | 0:未检测到XTAL振荡故障             | R/W |

|       |                      |    | 1: 检测到XTAL振荡故障             |     |

|       |                      |    | 置位条件:                      |     |

|       |                      |    | XTALSTDE=1的条件下,XTAL振荡故障    |     |

|       |                      |    | 清零条件:系统时钟选择XTAL以外时钟时,读1写0。 |     |

## 4.9.6 CMU HRC 控制寄存器(CMU\_HRCCR)

复位值: 0x00

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0     |  |

|----|----|----|----|----|----|----|--------|--|

| -  | -  | -  | -  | -  | -  | -  | HRCSTP |  |

| 位     | 标记                | 位名 | 功能              | 读写  |

|-------|-------------------|----|-----------------|-----|

| b7~b1 | 7~b1 Reserved -   |    | 读出时为"0",写入时写"0" | R/W |

| b0    | HRCSTP HRC振荡器开启停止 |    | 0: HRC振荡器振荡     | R/W |

|       |                   | 位  | 1: HRC振荡器停止     |     |

#### 注意:

- HRC 选作系统时钟源时,禁止 CMU\_HRCCR.HRCSTP 写"1"停止 HRC 时钟。

## 4.9.7 CMU HRC 频率配置寄存器(CMU\_HRCCFGR)

复位值:由ICG0.HRCFREQS[3:0]的值决定

| b7 | b6 | b5 | b4 | b3 | b2     | b1       | b0 |

|----|----|----|----|----|--------|----------|----|

| -  | -  | -  | -  |    | HRCFRE | EQS[3:0] |    |

| 位     | 标记       | 位名       | 功能                                           |                                  |                   | 读写 |  |  |

|-------|----------|----------|----------------------------------------------|----------------------------------|-------------------|----|--|--|

| b7~b4 | Reserved | -        | 读出时为"0",写入时                                  | 读出时为"0",写入时写"0"                  |                   |    |  |  |

| b3~0  | HRCFREQS | HRC频率选择位 | 内部高速振荡器频率选                                   | 内部高速振荡器频率选择,复位值由ICG0.HRCFREQS决定。 |                   |    |  |  |

|       |          |          | HRCFREQS[3]只能通过ICG0.HRCFREQS[3]设定,不可以软件改写。   |                                  |                   |    |  |  |

|       |          |          | HRCFREQS[2:0]可通过ICG0.HRCFREQS[2:0]设定。亦可软件改写。 |                                  |                   |    |  |  |

|       |          |          | 该寄存器通过设定EFM                                  | _FAPRT寄存器解除写值                    | 呆护。               |    |  |  |

|       |          |          | HD CEDE OCIA AL                              | HRO                              | <b>C</b> 频率       |    |  |  |

|       |          |          | HRCFREQS[2:0]                                | IID CEDE OCIAL A                 | IID GED EG GIAL 1 |    |  |  |

| HDCEDEOS(3.0) | HRC           | 频率            |

|---------------|---------------|---------------|

| HRCFREQS[2:0] | HRCFREQS[3]=0 | HRCFREQS[3]=1 |

| 000           | 32MHz         | 48MHz         |

| 001           | 16MHz         | 24MHz         |

| 010           | 8MHz          | 12MHz         |

| 011           | 4MHz          | 6MHz          |

| 100           | 2MHz          | 3MHz          |

| 101~111       | 1MHz          | 1.5MHz        |

## 4.9.8 CMU LRC 控制寄存器(CMU\_LRCCR)

复位值: 0x00

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0     |

|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | LRCSTP |

| 位     | 标记       | 位名         | 功能              | 读写  |

|-------|----------|------------|-----------------|-----|

| b7~b1 | Reserved | -          | 读出时为"0",写入时写"0" | R/W |

| b0    | LRCSTP   | LRC振荡器开启停止 | 0: LRC振荡器振荡     | R/W |

|       |          | 位          | 1: LRC振荡器停止     |     |

#### 注意:

- LRC 选作系统时钟源时,禁止 LRCSTP 写"1"停止 LRC 时钟。

## 4.9.9 CMU 时钟源稳定状态器(CMU\_OSCSTBSR)

| b7 | b6 | b5 | b4 | b3       | b2 | b1 | b0      |

|----|----|----|----|----------|----|----|---------|

| -  | -  | -  | -  | XTALSTBF | -  | -  | HRCSTBF |

| 位     | 标记       | 位名        | 功能              | 读写 |

|-------|----------|-----------|-----------------|----|

| b7~5  | Reserved | -         | 读出时为"0",写入时写"0" | R  |

| b4    | Reserved | -         | 读出时为"0",写入时写"0" | R  |

| b3    | XTALSTBF | XTAL稳定标志位 | 0: XTAL停止或者未稳定  | R  |

|       |          |           | 1: XTAL稳定       |    |

| b2~b1 | Reserved | -         | 读出时为"0",写入时写"0" | R  |

| b0    | HRCSTBF  | HRC稳定标志位  | 0: HRC停止或者未稳定   | R  |

|       |          |           | 1: HRC稳定        |    |

## 4.9.10 CMU 系统时钟源切换寄存器(CMU\_CKSWR)

复位值: 0x00

| b7 | b6 | b5 | b4 | b3 | b2 | b1   | b0     |

|----|----|----|----|----|----|------|--------|

| -  | -  | -  | -  | -  | -  | CKSW | V[1:0] |

| 位     | 标记        | 位名      | 功能                                   | 读写  |

|-------|-----------|---------|--------------------------------------|-----|

| b7~b2 | Reserved  | -       | 读出时为"0",写入时写"0"                      | R/W |

| b1-b0 | CKSW[1:0] | 系统时钟源切换 | 00: 选择HRC时钟作为系统时钟                    | R/W |

|       |           |         | 01: 选择XTAL时钟作为系统时钟                   |     |

|       |           |         | 10: 选择LRC时钟作为系统时钟                    |     |

|       |           |         | 11: 禁止设定                             |     |

|       |           |         | 注:                                   |     |

|       |           |         | 1, 切换的目标时钟源, 需保证在时钟稳定状态。             |     |

|       |           |         | 2, 流程参照【时钟源切换】章节                     |     |

|       |           |         | 3,PWR_STPMCR.CKSMRC位为1时,停止模式唤醒后,此寄存器 |     |

|       |           |         | 初始化,系统时钟源选择HRC时钟。                    |     |

## 4.9.11 CMU 时钟分频配置存器(CMU\_SCKDIVR)

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0      |

|----|----|----|----|----|----|----|---------|

| -  | -  | -  | -  | -  | -  |    | IV[2:0] |

| 位     | 标记          | 位名          | 功能                                 | 读写  |

|-------|-------------|-------------|------------------------------------|-----|

| b7~b3 | Reserved    | -           | 读出时为"0",写入时写"0"                    | R/W |

| b2~b0 | SCKDIV[2:0] | CPU及周边时钟    | 000: 系统时钟                          | R/W |

|       |             | (HCLK) 分频选择 | 001: 系统时钟的2分频                      |     |

|       |             |             | 010: 系统时钟的4分频                      |     |