# HK32F0301M 用户手册

版本: 2.2

发布日期: 2023-10-13

# 前言

### 编写目的

本文档介绍了 HK32F0301M 系列芯片的功能框图、存储器映射、Flash、中断和事件等功能以及各功能模块的寄存器描述,旨在帮助用户快速开发 HK32F0301M 的应用及产品。

### 读者对象

本文适用于以下读者:

- 开发工程师

- 芯片测试工程师

### 版本说明

本文档对应的产品系列为 HK32F0301M 系列芯片。

### 修订记录

| 版本  | 日期         | 修订内容                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 | 2020/02/21 | 首次发布。                                                                                                                                                                          |

| 1.1 | 2020/03/04 | 增加了选项字节的章节。                                                                                                                                                                    |

| 1.2 | 2021/04/16 | 更新了寄存器的章节内容。                                                                                                                                                                   |

| 1.3 | 2021/12/17 | 添加了各章节的功能描述内容。                                                                                                                                                                 |

| 1.4 | 2022/02/24 | 更新了"8.2 GPIO 功能描述"、"11.7 内部参考电压"等。                                                                                                                                             |

| 1.5 | 2022/03/30 | 更正了全文中的一些小错误。                                                                                                                                                                  |

| 1.6 | 2022/09/16 | 1. 在"1简介"中添加了新型号: HK32F0301MF4N6。 2. 删除了"11.3.2 可编程分辨率(RES)快速转换模式"、"11 ADC 寄存器模数转换器"中有关可配置分辨率和 RES 位的描述。 3. 修改了 USART 的框图。 4. 更正了 TIM2 的计数器位数,TIM6 添加了向下计数功能。 5. 更正了全文中的一些小错误。 |

| 1.7 | 2022/10/09 | <ol> <li>更新了"2.1 系统架构"中的图 2-1、"2.2 存储器映射及寄存器编址"中的图 2-2;</li> <li>更正了"3.1 Flash 特性"中的 Flash 访问位宽、"13.3.10 TIM2 计数器(TIM2_CNT)"的位数,以及 GPIO 外部输入时钟的最高频率。</li> </ol>                |

| 1.8 | 2022/10/18 | <ol> <li>更新了"8.3 GPIO 寄存器"中 GPIOx_MODER、GPIOx_PUPDR 和 GPIOx_IOSR 寄存器的复位值,以及 GPIOx_IOSR 的寄存器位等。</li> <li>添加了"ADC 寄存器"中位域的说明。</li> </ol>                                         |

| 1.9 | 2023/05/17 | 1. 修改了 "6.2 时钟"中时钟树的 FLITFCLK 为 2MHz;<br>2. 增加了 "11.7 内部参考电压"中 VREFINT_CAL 在系统中的存储地址。<br>3. 删除了 "19 通用同步异步收发器(USART)"中数据字长编程为 7 位的相关描述。<br>4. 更正了全文中的一些小错误。                    |

| 版本  | 日期         | 修订内容                                                                                                                                                                   |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 | 2023/05/31 | 1. 更新了章节 "3 Flash"中擦除后的"随机值"的描述,改为:"趋近于 0 的随机值"。<br>2. 更正了章节"19 通用同步异步收发器(USART)"的框图"图 19 1 USART 框图"。                                                                 |

| 2.1 | 2023/07/13 | 在"3.2.4写保护"一节中添加了写保护生效条件的说明。                                                                                                                                           |

| 2.2 | 2023/10/13 | 1. 更新了章节"11 模拟数字转换器(ADC)"中仅支持 12 位分辨率。 2. 更新了章节"19.4.4 USART 波特率生成"中的波特率公式。 3. 更新了章节"16.2 IWDG 功能描述"中的 IWDG 框图,预分频器为 3 位,而不是之前的 8 位。 4. 更新了章节"20.7.1 I2S 概述"中的 I2S 框图。 |

# 目录

| 1 简介                                | 1  |

|-------------------------------------|----|

| 2 系统及存储器概述                          | 2  |

| 2.1 系统架构                            | 2  |

| 2.1.1 总线架构                          | 2  |

| 2.2 存储器映射及寄存器编址                     | 3  |

| 2.3 SRAM                            | 3  |

| 2.4 启动配置                            | 4  |

| 3 Flash                             | 5  |

| 3.1 Flash 特性                        | 5  |

| 3.2 Flash 功能                        | 5  |

| 3.2.1 Flash 结构                      | 5  |

| 3.2.2 读操作                           | 6  |

| 3.2.3 读保护                           | 6  |

| 3.2.3.1 改变读保护级别                     | 7  |

| 3.2.4 写保护                           | 7  |

| 3.2.5 主 Flash 写和擦除操作                | 8  |

| 3.2.5.1 主 Flash 空间的解锁               | 8  |

| 3.2.5.2 主 Flash 擦除                  | 8  |

| 3.2.5.3 主 Flash 编程                  | 10 |

| 3.2.6 Flash 中断                      | 11 |

| 3.3 Flash 选项字节                      | 11 |

| 3.3.1 选项字节擦除                        | 13 |

| 3.3.2 选项字节编程                        | 14 |

| 3.4 EEPROM                          | 14 |

| 3.4.1 EEPROM 的擦除                    | 15 |

| 3.4.2 EEPROM 的编程                    | 15 |

| 3.5 Flash 寄存器                       | 15 |

| 3.5.1 Flash 访问控制寄存器(FLASH_ACR)      | 15 |

| 3.5.2 Flash 关键字寄存器(FLASH_KEYR)      | 16 |

| 3.5.3 Flash 选项关键字寄存器(FLASH_OPTKEYR) | 17 |

|      | 3.5.4 Flash 状态寄存器(FLASH_SR)       | 17 |

|------|-----------------------------------|----|

|      | 3.5.5 Flash 控制寄存器(FLASH_CR)       | 18 |

|      | 3.5.6 Flash 地址寄存器(FLASH_AR)       | 19 |

|      | 3.5.7 Flash 选项字节寄存器(FLASH_OBR)    | 19 |

|      | 3.5.8 Flash 写保护寄存器(FLASH_WRPR)    | 20 |

|      | 3.5.9 Flash 控制寄存器 2(FLASH_ECR)    | 21 |

|      | 3.5.10 中断向量表偏移寄存器(INT_VEC_OFFSET) | 21 |

| 4 CI | RC 计算单元(CRC)                      | 23 |

|      | 4.1 CRC 主要功能                      | 23 |

|      | 4.2 CRC 功能描述                      | 23 |

|      | 4.3 CRC 寄存器                       | 24 |

|      | 4.3.1 数据寄存器(CRC_DR)               | 24 |

|      | 4.3.2 独立数据寄存器(CRC_IDR)            | 24 |

|      | 4.3.3 控制寄存器(CRC_CR)               | 25 |

|      | 4.3.4 CRC 初值寄存器(CRC_INIT)         | 25 |

| 5 电  | <b>担源控制(PWR)</b>                  | 27 |

|      | 5.1 电源                            | 27 |

|      | 5.1.1 独立的 A/D 转换器供电和参考电压          | 27 |

|      | 5.1.2 电压调节器                       | 27 |

|      | 5.2 上电/掉电复位(POR/PDR)              | 28 |

|      | 5.3 低功耗模式                         | 28 |

|      | 5.3.1 降低系统时钟                      | 29 |

|      | 5.3.2 外部时钟的控制                     | 29 |

|      | 5.3.3 睡眠(Sleep)模式                 | 30 |

|      | 5.3.3.1 进入睡眠模式                    | 30 |

|      | 5.3.3.2 退出睡眠模式                    | 30 |

|      | 5.3.4 深度睡眠(DeepSleep)模式           | 31 |

|      | 5.3.5 停机(Stop)模式                  | 31 |

|      | 5.3.5.1 进入停机模式                    | 31 |

|      | 5.3.5.2 退出停机模式                    | 31 |

|      | 5.3.6 待机(Standby)模式               | 31 |

| 5.3.6.1 进入待机模式                       | 31 |

|--------------------------------------|----|

| 5.3.6.2 退出待机模式                       | 32 |

| 5.3.6.3 待机模式下的输入/输出端口状态              | 32 |

| 5.3.6.4 待机模式下的自动唤醒(STBAWU)           | 32 |

| 5.3.6.5 待机模式下的 IO 保持                 | 32 |

| 5.3.6.6 待机模式下的备份                     | 32 |

| 5.3.7 调试模式                           | 32 |

| 5.4 PWR 寄存器                          | 32 |

| 5.4.1 电源控制寄存器(PWR_CR)                | 32 |

| 5.4.2 电源控制/状态寄存器(PWR_CSR)            | 33 |

| 5.4.3 WKUP 引脚极性控制寄存器(PWR_WUP_POL)    | 34 |

| 5.4.4 待机模式下掉电检测控制寄存器(PWR_PORPDR_CFG) | 35 |

| 5.4.5 内部参考电压输出选择寄存器(PWR_VREF_SEL)    | 36 |

| 5.4.6 待机模式下自动唤醒定时器(PWR_SAWUT)        | 36 |

| 5.4.7 待机模式下备份(PWR_SBKPO)             | 36 |

| 5.4.8 待机模式下备份(PWR_SBKP1)             | 37 |

| 6 复位和时钟控制(RCC)                       | 38 |

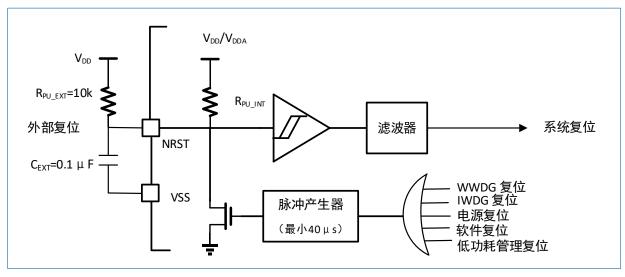

| 6.1 复位                               | 38 |

| 6.1.1 系统复位                           | 38 |

| 6.1.2 电源复位                           | 39 |

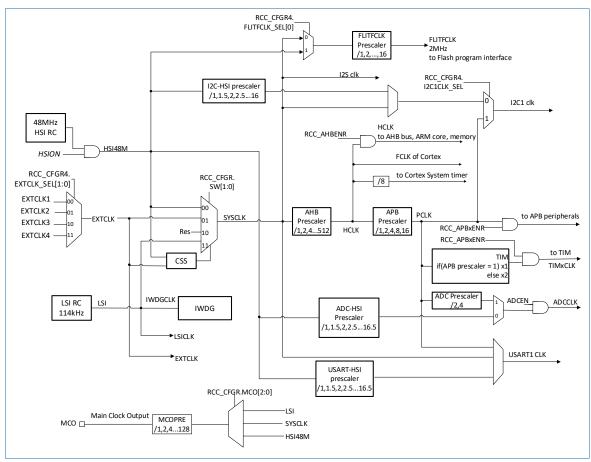

| 6.2 时钟                               | 39 |

| 6.2.1 HSI 时钟                         | 40 |

| 6.2.2 GPIO 外部时钟输入                    | 40 |

| 6.2.3 LSI 时钟                         | 40 |

| 6.2.4 系统时钟(SYSCLK)选择                 | 41 |

| 6.2.5 看门狗时钟                          | 41 |

| 6.2.6 时钟输出功能(MCO)                    | 41 |

| 6.3 RCC 寄存器                          | 41 |

| 6.3.1 时钟控制寄存器(RCC_CR)                | 41 |

| 6.3.2 时钟配置寄存器(RCC_CFGR)              | 43 |

| 6.3.3 时钟中断寄存器(RCC_CIR)               | 44 |

| 6.3.4 APB2 外设复位寄存器(RCC_APB2RSTR)         | 46 |

|------------------------------------------|----|

| 6.3.5 APB1 外设复位寄存器(RCC_APB1RSTR)         | 47 |

| 6.3.6 AHB 外部时钟使能寄存器(RCC_AHBENR)          | 49 |

| 6.3.7 APB 外设时钟使能寄存器 2(RCC_APB2ENR)       | 50 |

| 6.3.8 APB1 外设时钟使能寄存器(RCC_APB1ENR)        | 52 |

| 6.3.9 控制/状态寄存器(RCC_CSR)                  | 53 |

| 6.3.10 AHB 外设复位寄存器(RCC_AHBRSTR)          | 55 |

| 6.3.11 时钟配置寄存器 3(RCC_CFGR3)              | 56 |

| 6.3.12 控制寄存器(RCC_CSS)                    | 57 |

| 6.3.13 时钟配置寄存器 4(RCC_CFGR4)              | 57 |

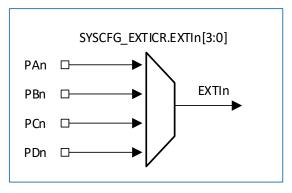

| 7 系统配置控制器(SYSCFG)                        | 59 |

| 7.1 SYSCFG 寄存器                           | 59 |

| 7.1.1 SYSCFG 配置寄存器 1(SYSCFG_CFGR1)       | 59 |

| 7.1.2 SYSCFG 外部中断配置寄存器 1(SYSCFG_EXTICR1) | 59 |

| 7.1.3 SYSCFG 外部中断配置寄存器 2(SYSCFG_EXTICR2) | 60 |

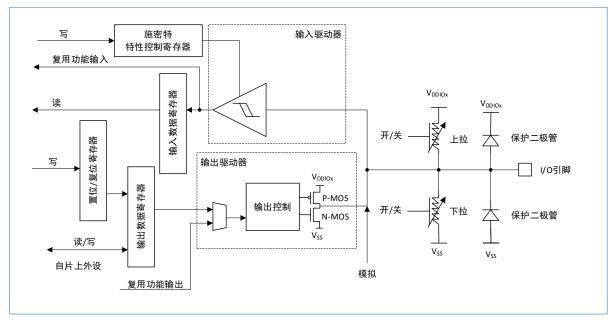

| 8 通用 I/O(GPIO)                           | 61 |

| 8.1 GPIO 的主要特性                           | 61 |

| 8.2 GPIO 功能描述                            | 61 |

| 8.2.1 通用 I/O(GPIO)                       | 63 |

| 8.2.2 I/O 引脚复用功能复用器和映射                   | 63 |

| 8.2.3 I/O 端口控制寄存器                        | 64 |

| 8.2.4 I/O 端口数据寄存器                        | 64 |

| 8.2.5 I/O 数据位操作                          | 64 |

| 8.2.6 GPIO 锁定机制                          | 64 |

| 8.2.7 I/O 复用功能输入输出                       | 65 |

| 8.2.8 外部中断线/唤醒线                          | 65 |

| 8.2.9 输出配置                               | 65 |

| 8.2.10 复用功能配置                            | 65 |

| 8.2.11 模拟配置                              | 65 |

| 8.2.12 施密特功能配置                           | 66 |

| 8.3 GPIO 寄存器                             | 66 |

| 8.3.1 GPIO 端口模式寄存器(GPIOx_MODER)(x = AD)    | 66 |

|--------------------------------------------|----|

| 8.3.2 GPIO 端口输出类型寄存器(GPIOx_OTYPER)(x = AD) | 66 |

| 8.3.3 GPIO 口输出速度寄存器(GPIOx_OSPEEDR)(x = AD) | 67 |

| 8.3.4 GPIO 口上拉/下拉寄存器(GPIOx_PUPDR)(x = AD)  | 67 |

| 8.3.5 GPIO 端口输入数据寄存器(GPIOx_IDR)(x = AD)    | 67 |

| 8.3.6 GPIO 端口输出数据寄存器(GPIOx_ODR)(x = AD)    | 68 |

| 8.3.7 GPIO 端口置位/复位寄存器(GPIOx_BSRR)(x = AD)  | 68 |

| 8.3.8 GPIO 端口配置锁定寄存器(GPIOx_LCKR)(x = AB)   | 69 |

| 8.3.9 GPIO 复用功能低位寄存器(GPIOx_AFRL)(x = AD)   | 70 |

| 8.3.10 GPIO 端口位复位寄存器(GPIOx_BRR)(x=AD)      | 70 |

| 8.3.11 GPIO 端口输入输出施密特寄存器(GPIOx_IOSR)(x=AD) | 71 |

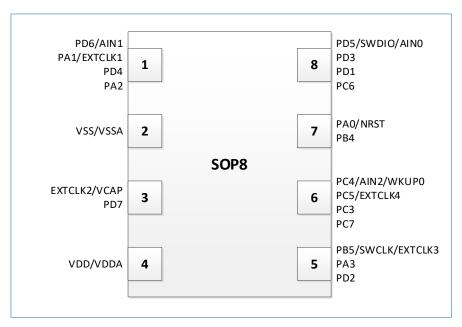

| 9 引脚选择功能(IOMUX)                            | 72 |

| 9.1 功能介绍                                   | 72 |

| 9.2 IOMUX 寄存器                              | 72 |

| 9.2.1 IOMUX 引脚功能选择寄存器(PIN_FUNC_SEL)        | 72 |

| 9.2.2 IOMUX 引脚选择寄存器(PKG_PIN_SEL)           | 73 |

| 9.2.3 IOMUX 功能控制寄存器(NRST_PIN_KEY)          | 74 |

| 9.2.4 IOMUX 引脚功能控制寄存器(NRST_PAO_SEL)        | 74 |

| 9.2.5 IOMUX 引脚功能控制寄存器(TIM2_CH0_IN_SEL)     | 75 |

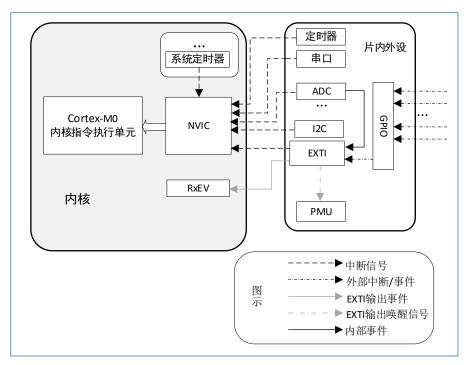

| 10 中断和事件(NVIC 和 EXTI)                      | 76 |

| 10.1 嵌套向量中断控制器(NVIC)                       | 76 |

| 10.1.1 NVIC 主要特性                           | 76 |

| 10.1.2 系统嘀嗒校准值寄存器                          | 76 |

| 10.1.3 中断和异常向量                             | 76 |

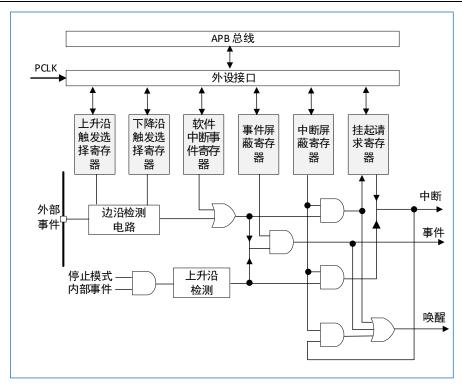

| 10.2 扩展中断和事件控制器(EXTI)                      | 78 |

| 10.2.1 主要特性                                | 78 |

| 10.2.2 框图                                  | 78 |

| 10.2.3 EXTI 与周边模块关系                        | 79 |

| 10.2.4 唤醒事件管理                              | 79 |

| 10.2.5 功能说明                                | 80 |

| 10.2.5.1 硬件中断选择                            | 80 |

| 10.2.5.2 硬件事件选择                     | 80 |

|-------------------------------------|----|

| 10.2.5.3 软件中断/事件的选择                 | 80 |

| 10.2.6 外部中断/事件线映射                   | 80 |

| 10.3 EXTI 寄存器                       | 81 |

| 10.3.1 中断屏蔽寄存器(EXTI_IMR)            | 81 |

| 10.3.2 事件屏蔽寄存器(EXTI_EMR)            | 82 |

| 10.3.3 上升沿触发选择寄存器(EXTI_RTSR)        | 82 |

| 10.3.4 下降沿触发选择寄存器(EXTI_FTSR)        | 83 |

| 10.3.5 软件中断事件寄存器(EXTI_SWIER)        | 83 |

| 10.3.6 请求挂起寄存器(EXTI_PR)             | 84 |

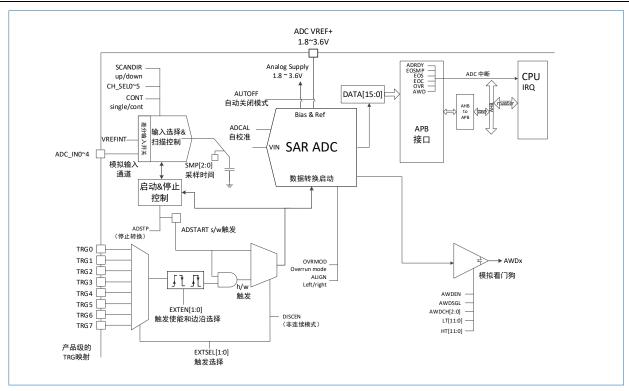

| 11 模拟数字转换器(ADC)                     | 85 |

| 11.1 ADC 主要特性                       | 85 |

| 11.2 ADC 功能描述                       | 85 |

| 11.2.1 ADC 引脚和内部信号                  | 86 |

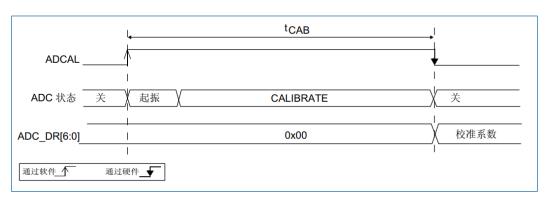

| 11.2.2 校准(ADCAL)                    | 86 |

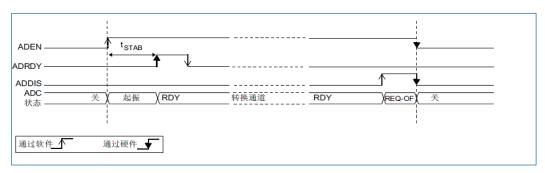

| 11.2.3 ADC 开关控制(ADEN, ADDIS, ADRDY) | 87 |

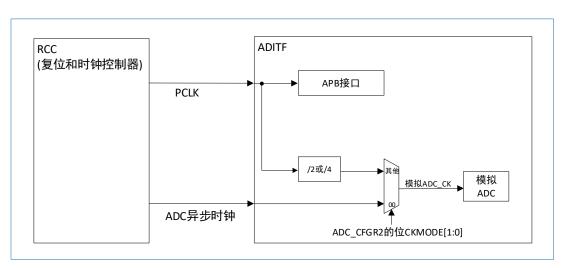

| 11.2.4 ADC 时钟(CKMODE)               | 88 |

| 11.2.5 配置 ADC                       | 89 |

| 11.2.6 通道选择                         | 89 |

| 11.2.7 可编程采样时间(SMP)                 | 89 |

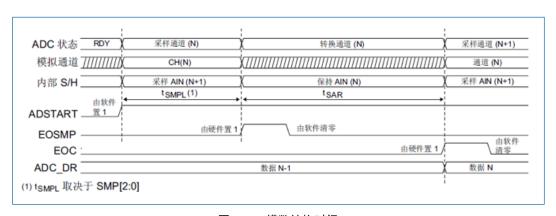

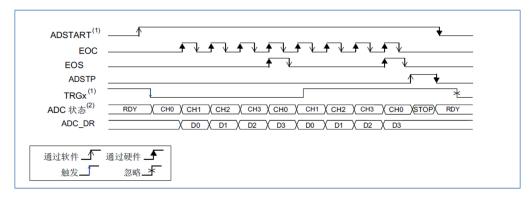

| 11.2.8 单次转换模式(CONT=0)               | 90 |

| 11.2.9 连续转换模式(CONT=1)               | 90 |

| 11.2.10 开始转换(ADSTART)               | 91 |

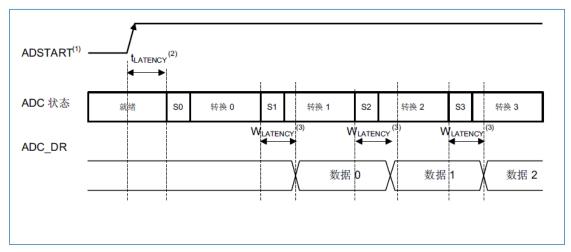

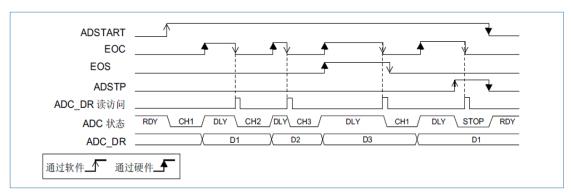

| 11.2.11 时序                          | 91 |

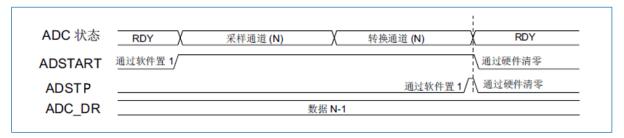

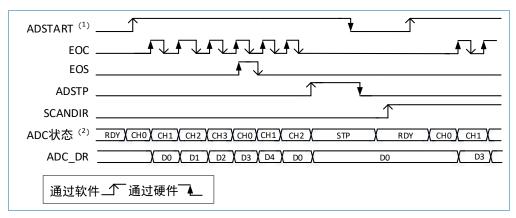

| 11.2.12 停止正在进行的转换(ADSTP)            | 92 |

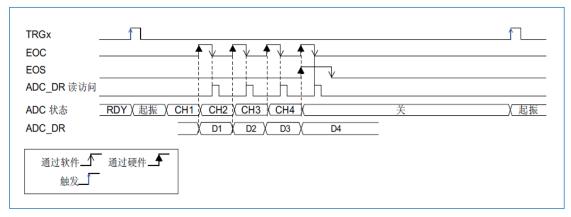

| 11.3 外部触发转换和触发极性(EXTSEL, EXTEN)     | 92 |

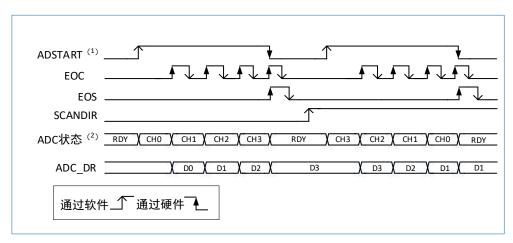

| 11.3.1 不连续模式(DISCEN)                | 93 |

| 11.3.2 转换结束、采样阶段结束(EOC, EOSMP 标志)   | 94 |

| 11.3.3 转换序列结束(EOS 标志)               | 94 |

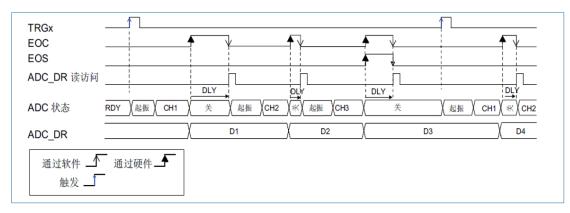

| 11.3.4 时序图示例(单次/连续模式硬件/软件触发)        | 94 |

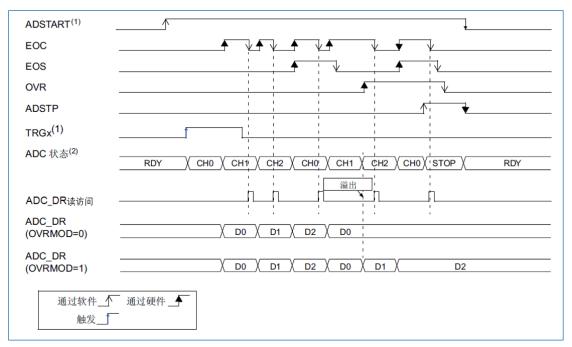

| 11.4 数据管理                           | 95 |

| 11.4.1 数据管理和数据对齐(ADC_DR, ALIGN)                | 95  |

|------------------------------------------------|-----|

| 11.4.2 ADC 溢出(OVR, OVRMOD)                     | 96  |

| 11.5 功耗特性                                      | 97  |

| 11.5.1 等待模式转换                                  | 97  |

| <b>11.5.2</b> 自动关闭模式(AUTOFF)                   | 97  |

| 11.6 模拟窗口看门狗(AWDEN, AWDSGL, AWDCH, HT/LT, AWD) | 98  |

| 11.7 内部参考电压                                    | 99  |

| 11.8 ADC 中断                                    | 100 |

| 11.9 ADC 寄存器                                   | 101 |

| 11.9.1 ADC 中断和状态寄存器(ADC_ISR)                   | 101 |

| 11.9.2 ADC 中断使能寄存器(ADC_IER)                    | 102 |

| 11.9.3 ADC 控制寄存器(ADC_CR)                       | 103 |

| 11.9.4 ADC 配置寄存器 1(ADC_CFGR1)                  | 105 |

| 11.9.5 ADC 配置寄存器 2(ADC_CFGR2)                  | 108 |

| 11.9.6 ADC 采样时间寄存器(ADC_SMPR)                   | 108 |

| 11.9.7 ADC 看门狗阈值寄存器(ADC_TR)                    | 109 |

| 11.9.8 ADC 通道选择寄存器(ADC_CHSELR)                 | 109 |

| 11.9.9 ADC 数据寄存器(ADC_DR)                       | 110 |

| 11.9.10 ADC 通用配置寄存器(ADC_CCR)                   | 110 |

| 11.9.11 ADC 控制寄存器 2(ADC_CR2)                   | 111 |

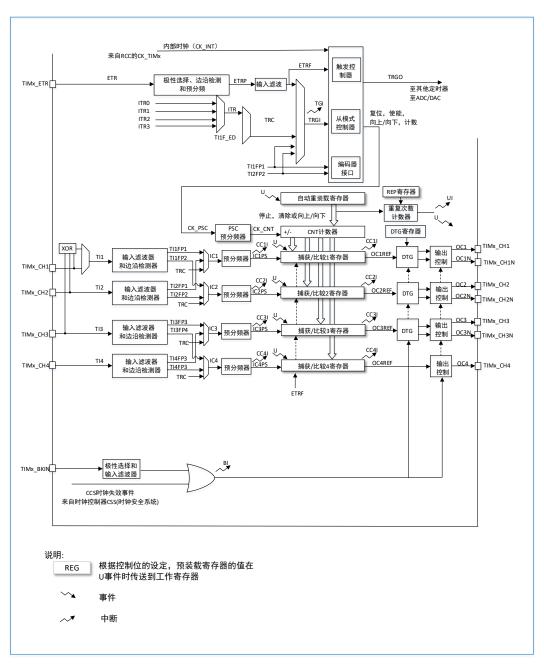

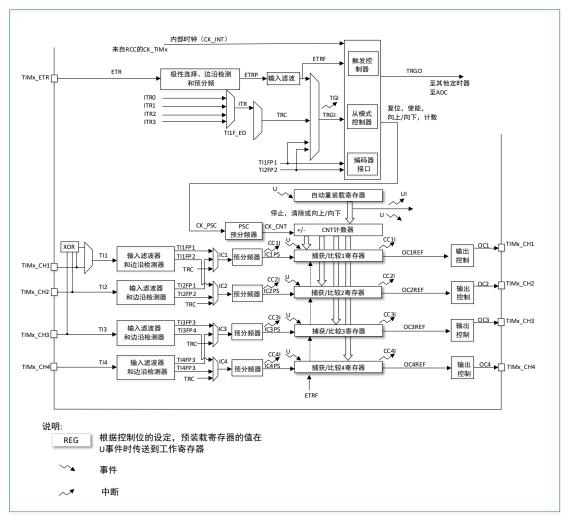

| 12 高级控制定时器(TIM1)                               | 112 |

| 12.1 TIM1 主要功能                                 | 112 |

| 12.2 TIM1 功能描述                                 | 113 |

| 12.2.1 时基单元                                    | 113 |

| 12.2.2 计数器模式                                   | 115 |

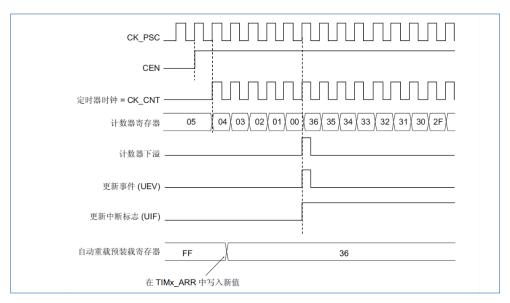

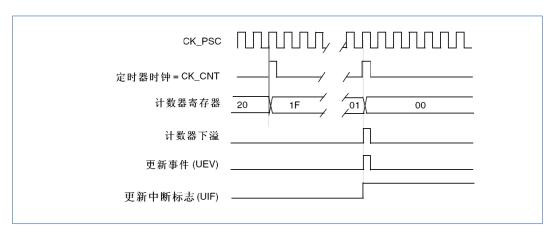

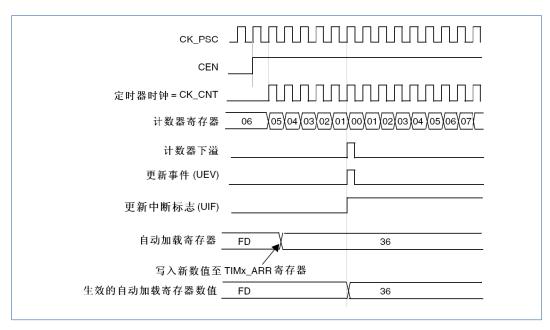

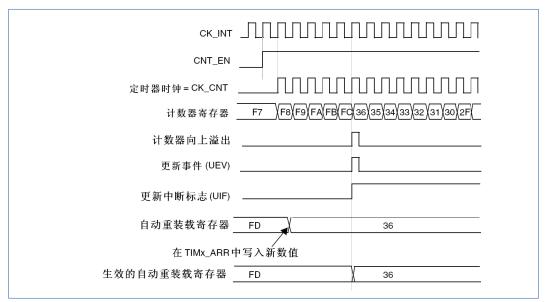

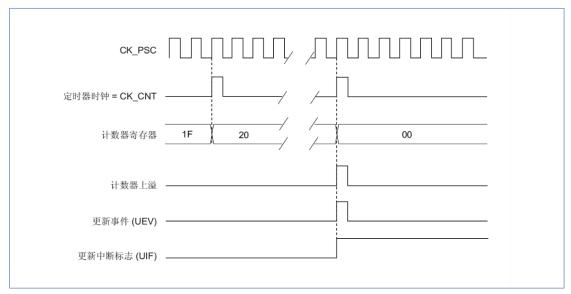

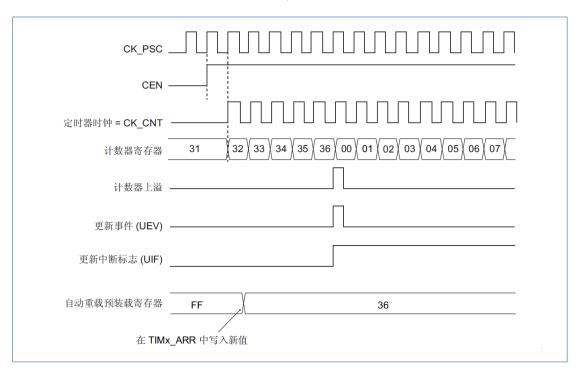

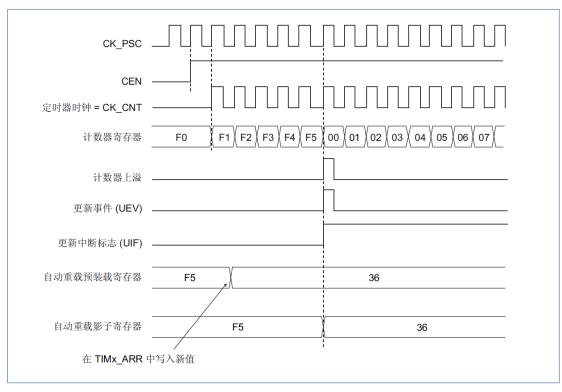

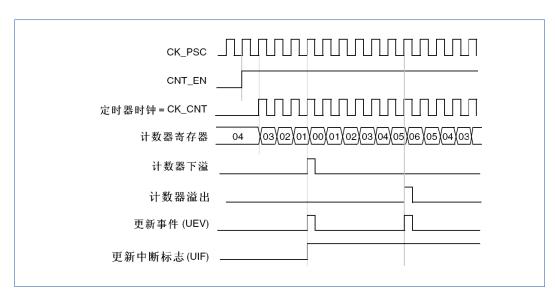

| 12.2.2.1 向上计数模式                                | 115 |

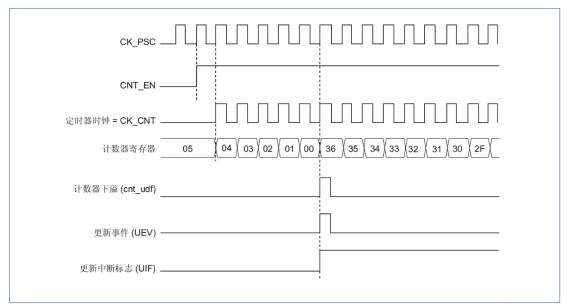

| 12.2.2.2 向下计数模式                                | 118 |

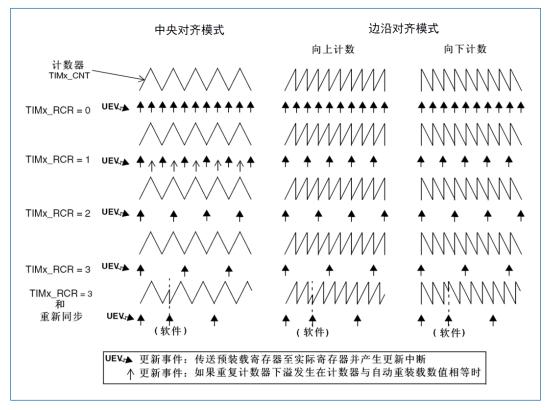

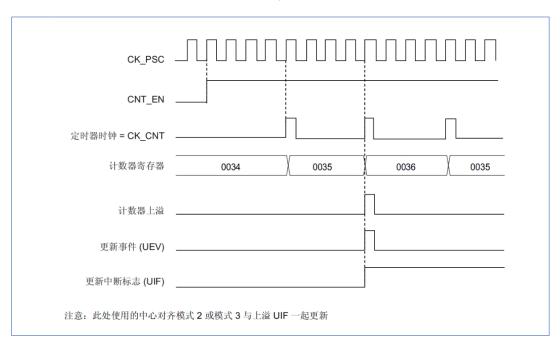

| 12.2.2.3 中央对齐模式(向上/向下计数)                       | 119 |

| 12.2.3 重复计数器                                   | 122 |

| 12.2.4 时钟选择                                    | 123 |

| 12.2.5 捕获/比较通道                                 | 125 |

|      | 12.2.6 输入捕获模式                        | 127 |

|------|--------------------------------------|-----|

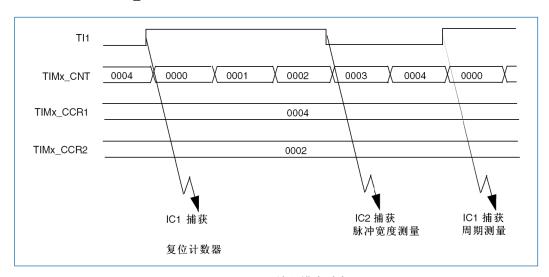

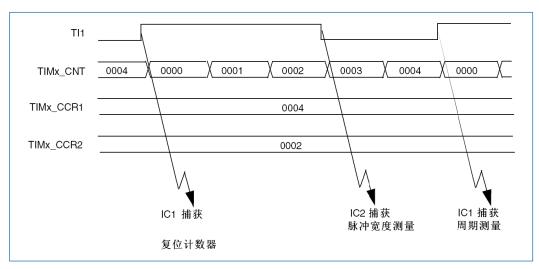

|      | 12.2.7 PWM 输入模式                      | 128 |

|      | 12.2.8 强制输出模式                        | 128 |

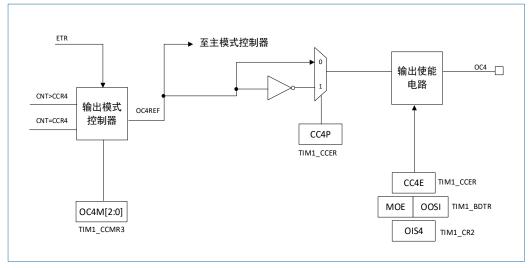

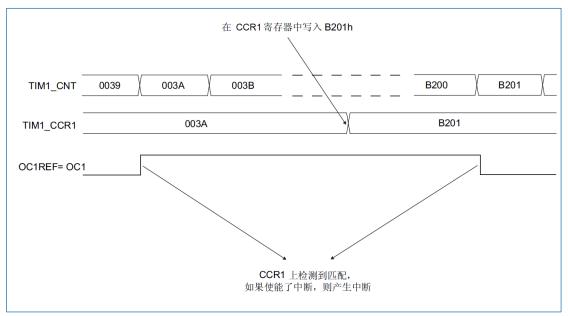

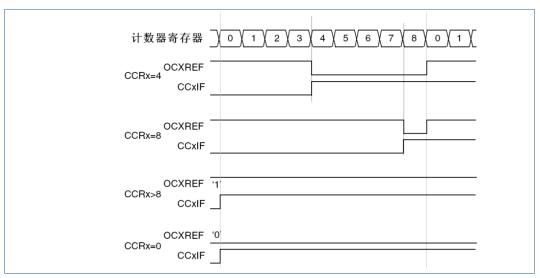

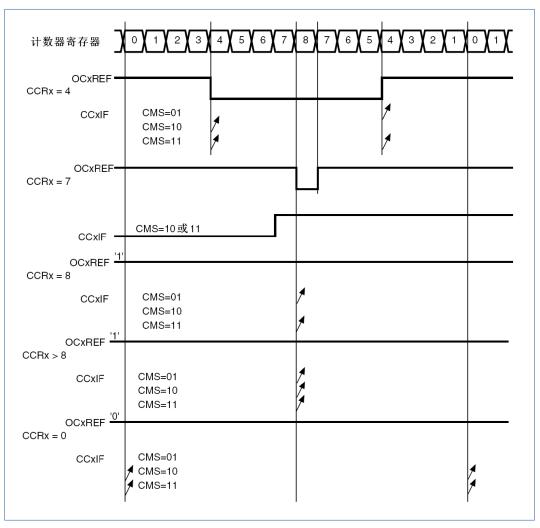

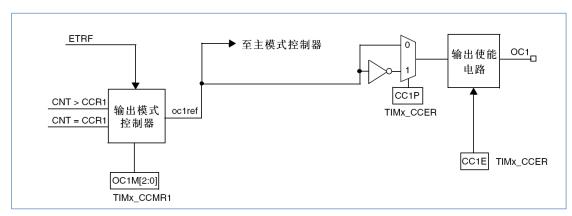

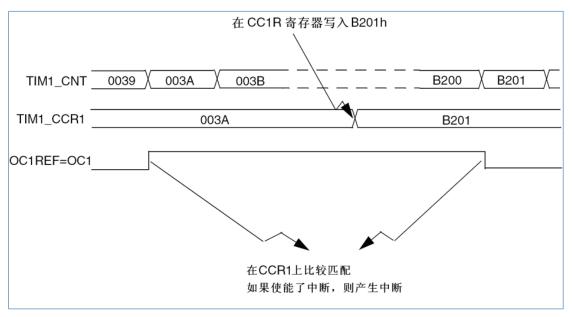

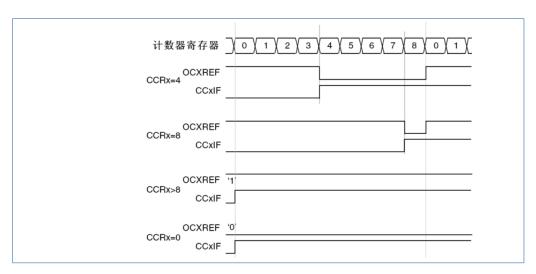

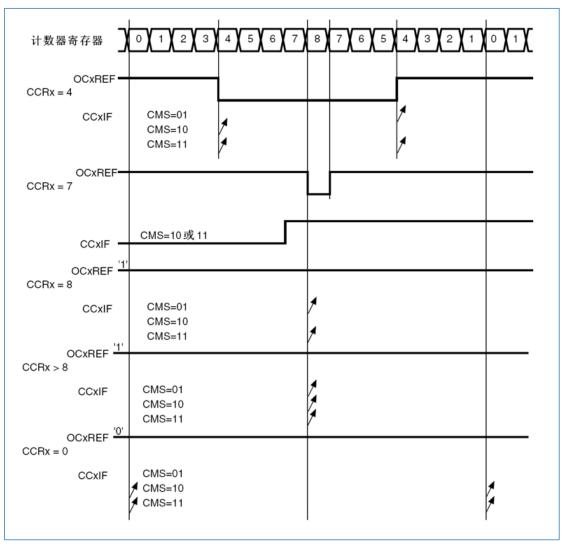

|      | 12.2.9 输出比较模式                        | 129 |

|      | 12.2.10 PWM 模式                       | 130 |

|      | 12.2.10.1 PWM 边沿对齐模式                 | 130 |

|      | 12.2.10.2 PWM 中央对齐模式                 | 131 |

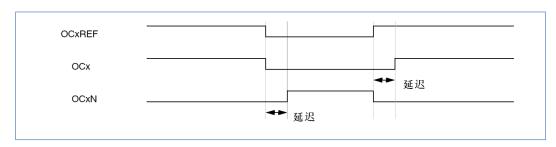

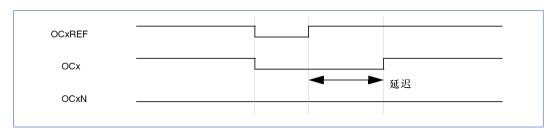

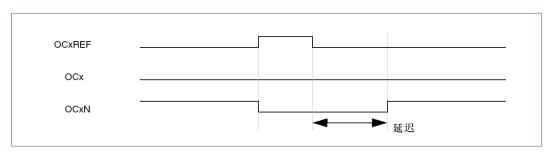

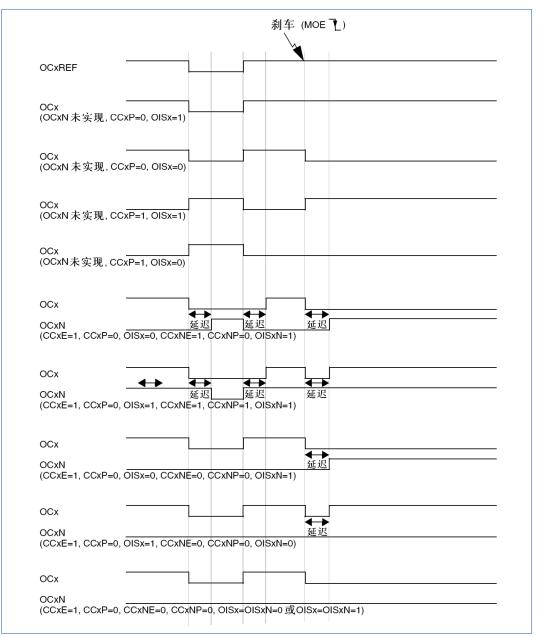

|      | 12.2.11 互补输出和死区插入                    | 132 |

|      | 12.2.12 使用刹车功能                       | 134 |

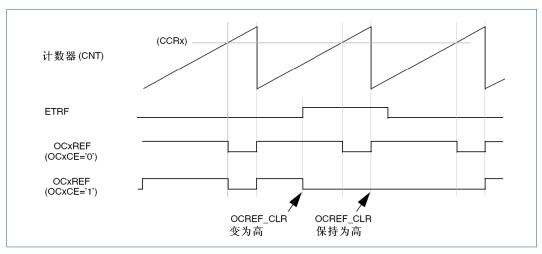

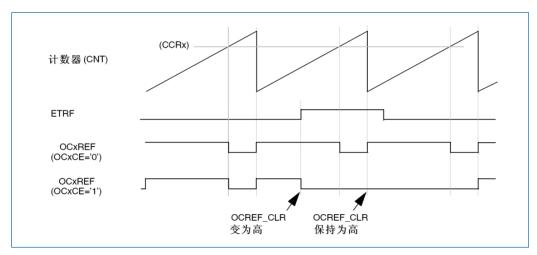

|      | 12.2.13 在外部事件时清除 OCxREF 信号           | 135 |

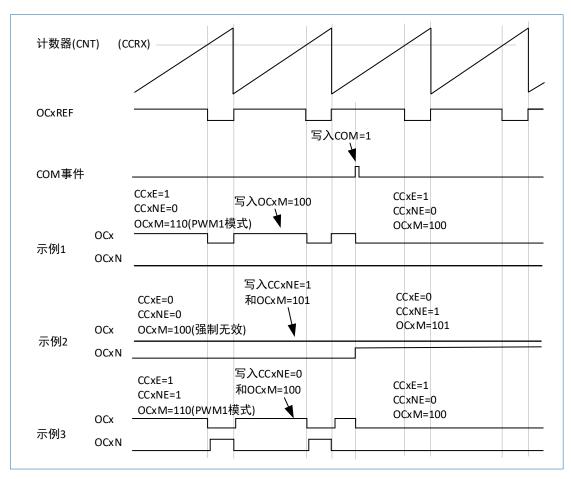

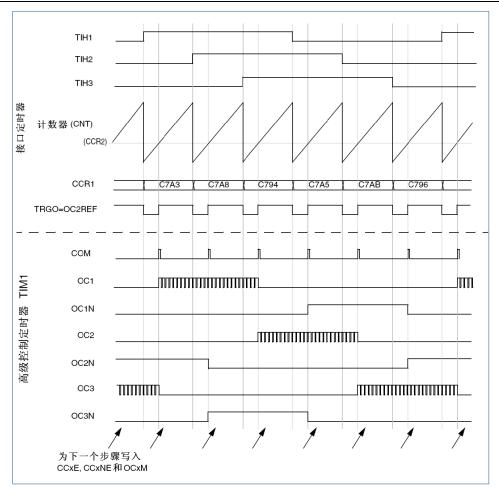

|      | 12.2.14 产生六步 PWM 输出                  | 136 |

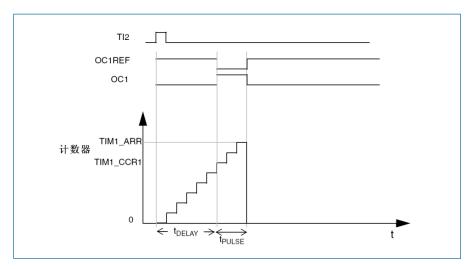

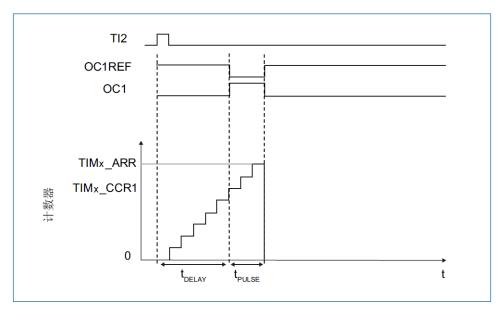

|      | 12.2.15 单脉冲模式                        | 137 |

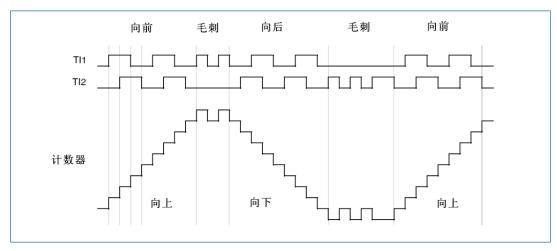

|      | 12.2.16 编码器接口模式                      | 138 |

|      | 12.2.17 定时器输入异或功能                    | 139 |

|      | 12.2.18 与霍尔传感器的接口                    | 140 |

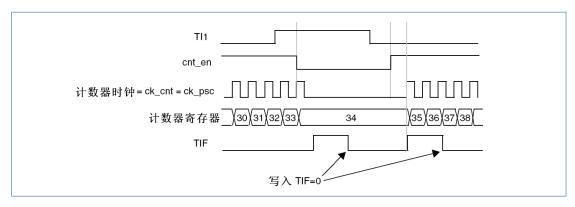

|      | 12.2.19 TIM1 定时器和外部触发的同步             | 141 |

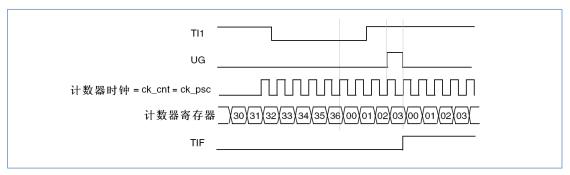

|      | 12.2.19.1 从模式: 复位模式                  | 141 |

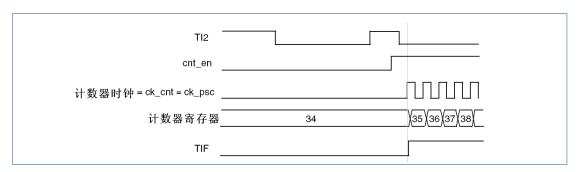

|      | 12.2.19.2 从模式: 门控模式                  | 142 |

|      | 12.2.19.3 从模式: 触发模式                  | 142 |

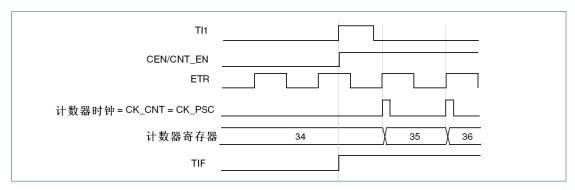

|      | 12.2.19.4 从模式:外部时钟模式 2+触发模式          | 143 |

|      | 12.2.20 定时器同步                        | 143 |

|      | 12.2.21 调试模式                         | 144 |

| 12.3 | 3 TIM1 寄存器                           | 144 |

|      | 12.3.1 TIM1 控制存器 1(TIM1_CR1)         | 144 |

|      | 12.3.2 TIM1 控制寄存器 2(TIM1_CR2)        | 145 |

|      | 12.3.3 TIM1 从模式控制寄存器(TIM1_SMCR)      | 147 |

|      | 12.3.4 TIM1 中断使能寄存器(TIM1_DIER)       | 149 |

|      | 12.3.5 TIM1 状态寄存器(TIM1_SR)           | 150 |

|      | 12.3.6 TIM1 事件产生寄存器(TIM1_EGR)        | 152 |

|      | 12.3.7 TIM1 捕捉/比较模式寄存器 1(TIM1_CCMR1) | 153 |

|      | 12.3.8 TIM1 捕捉/比较模式寄存器 2(TIM1_CCMR2) | 156 |

| 12.3.9 TIM1 捕捉/比较使能寄存器(TIM1_CCER)  | 158 |

|------------------------------------|-----|

| 12.3.10 TIM1 计数器(TIM1_CNT)         | 160 |

| 12.3.11 TIM1 预分频器(TIM1_PSC)        | 161 |

| 12.3.12 TIM1 自动重装载寄存器(TIM1_ARR)    | 161 |

| 12.3.13 TIM1 重复计数寄存器(TIM1_RCR)     | 161 |

| 12.3.14 TIM1 捕捉/比较寄存器 1(TIM1_CCR1) | 162 |

| 12.3.15 TIM1 捕捉/比较寄存器 2(TIM1_CCR2) | 162 |

| 12.3.16 TIM1 捕捉/比较寄存器 3(TIM1_CCR3) | 162 |

| 12.3.17 TIM1 捕捉/比较寄存器 4(TIM1_CCR4) | 163 |

| 12.3.18 TIM1 刹车和死区寄存器(TIM1_BDTR)   | 163 |

| 13 通用定时器(TIM2)                     | 165 |

| 13.1 TIM2 主要功能                     | 165 |

| 13.2 TIM2 功能描述                     | 166 |

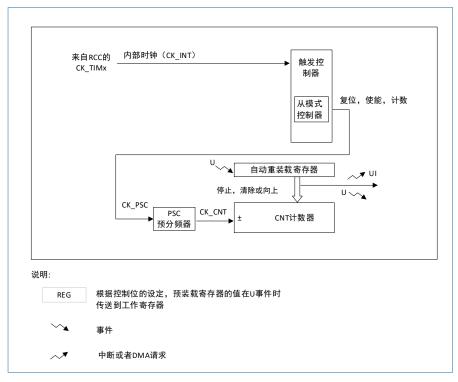

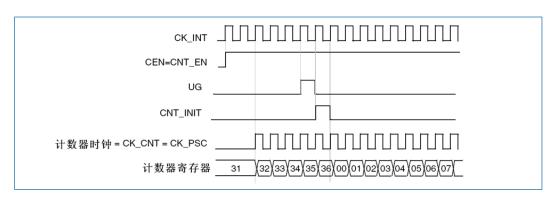

| 13.2.1 时基单元                        | 166 |

| 13.2.2 计数器模式                       | 168 |

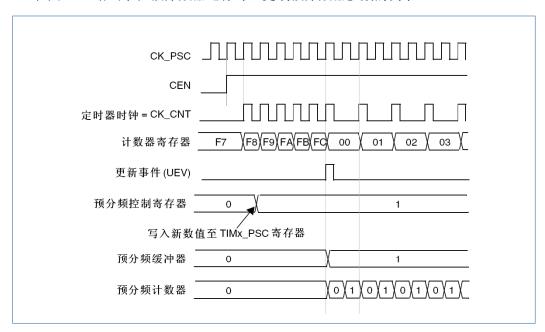

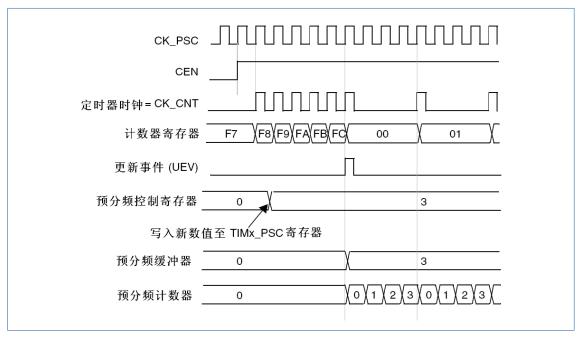

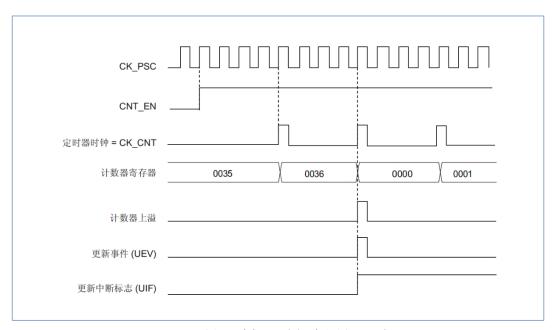

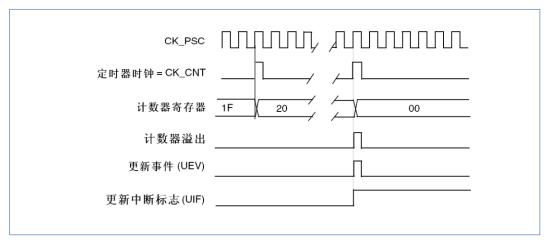

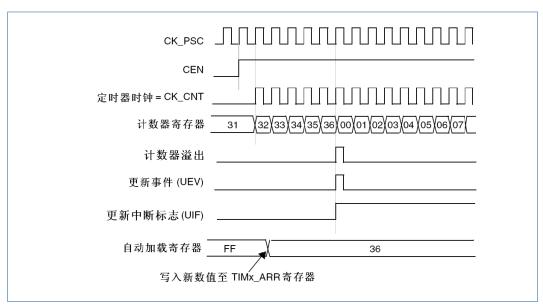

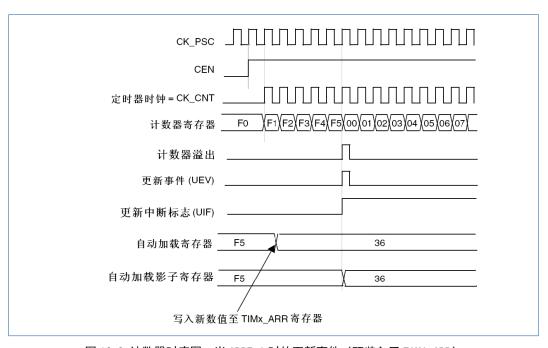

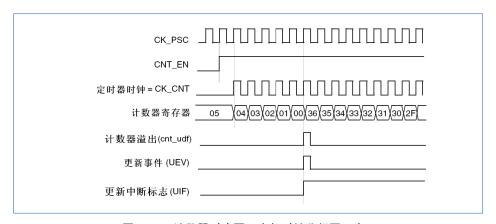

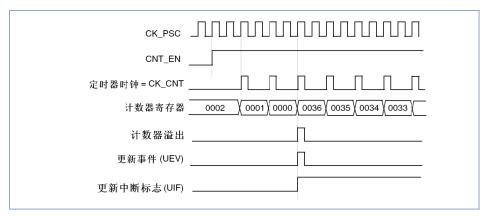

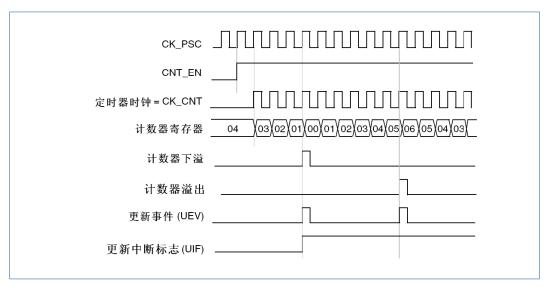

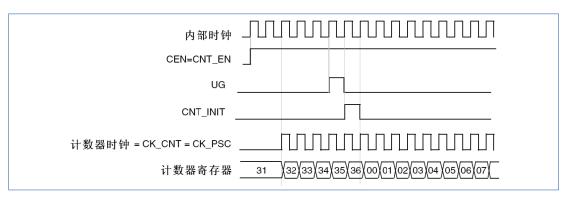

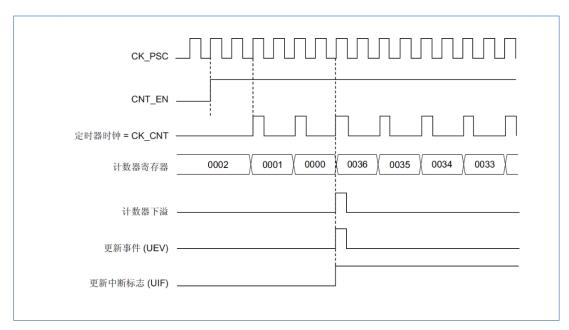

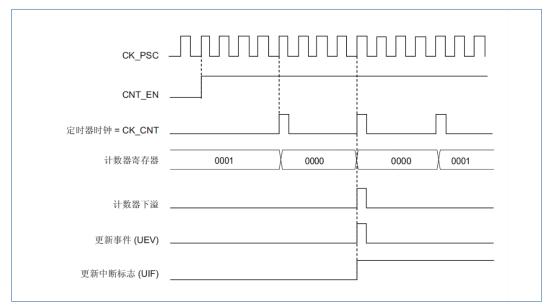

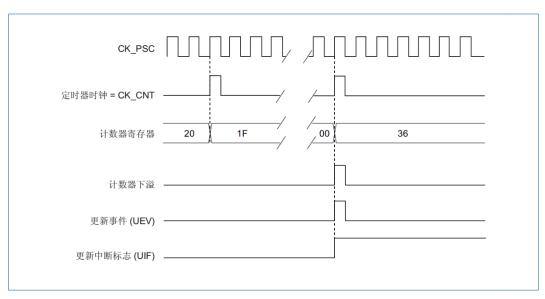

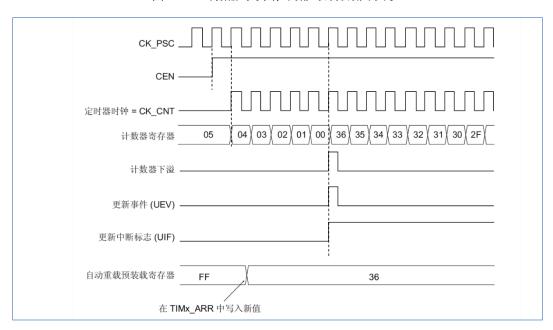

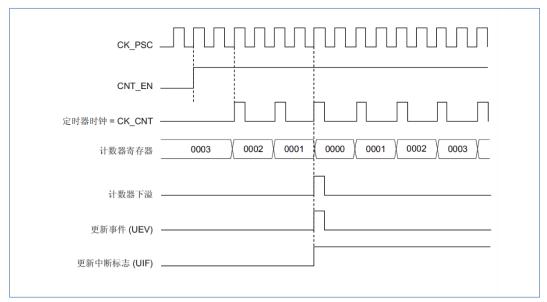

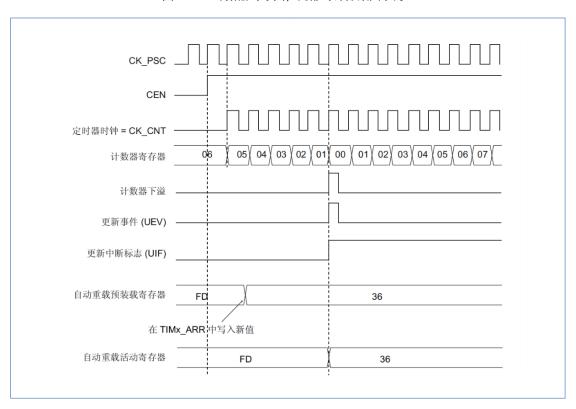

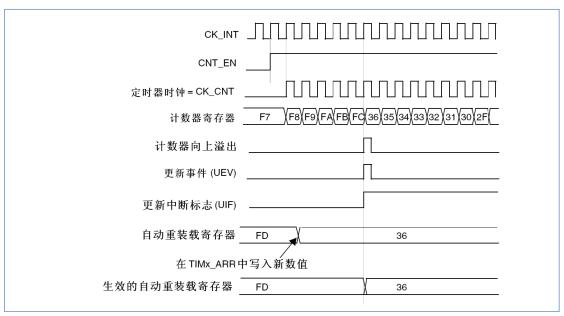

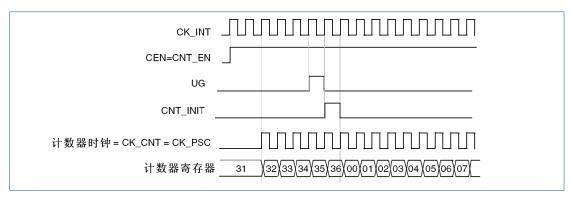

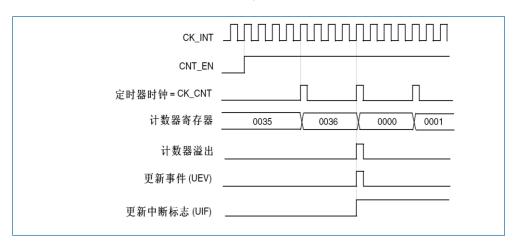

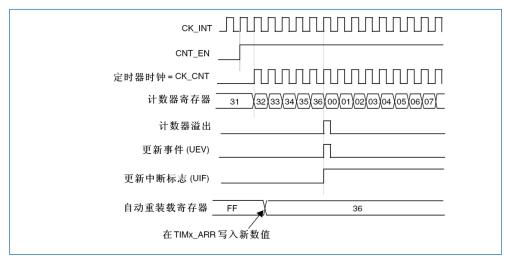

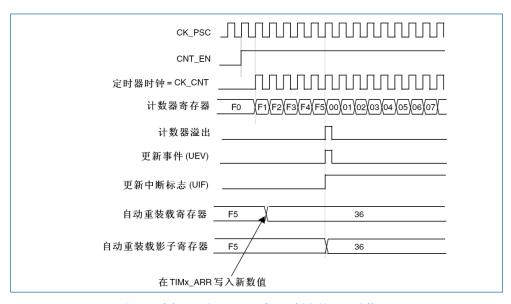

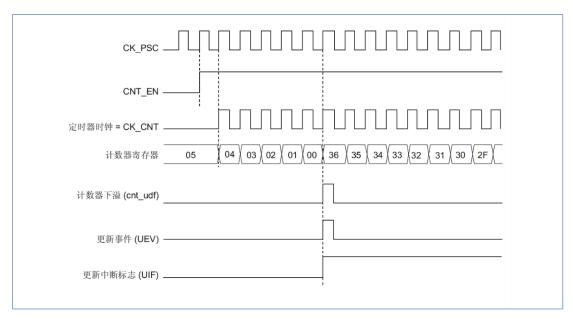

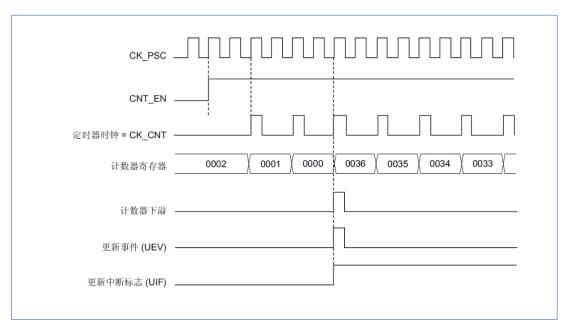

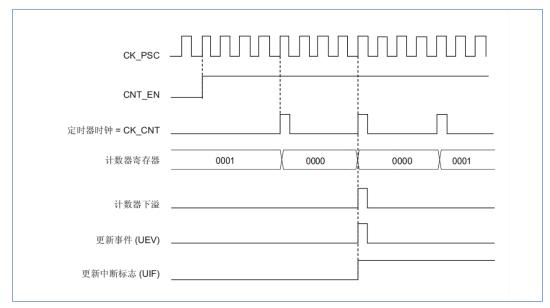

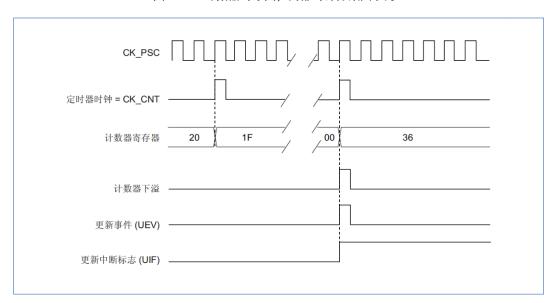

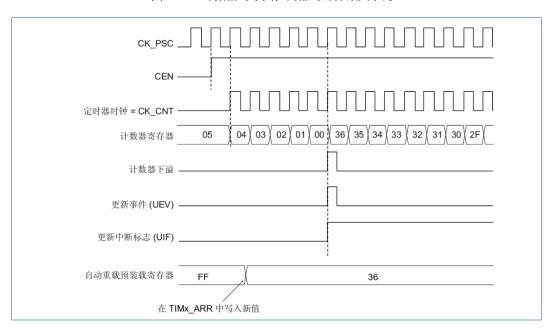

| 13.2.2.1 向上计数模式                    | 168 |

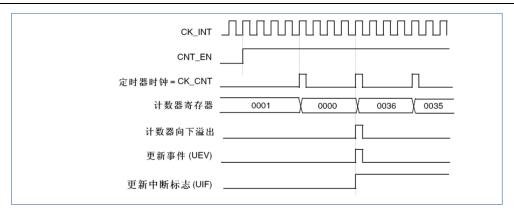

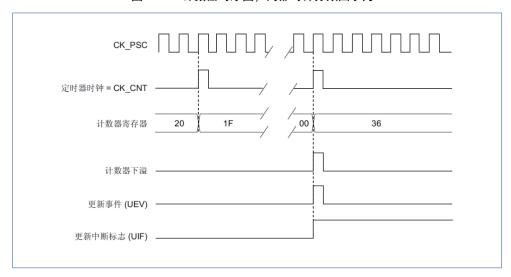

| 13.2.2.2 向下计数模式                    | 171 |

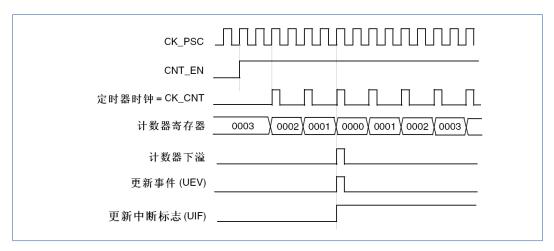

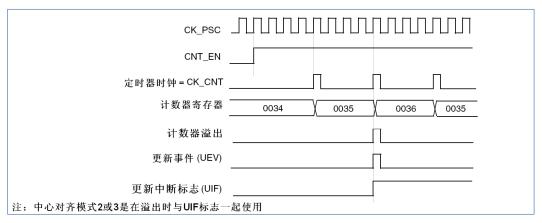

| 13.2.2.3 中央对齐模式(向上/向下计数)           | 174 |

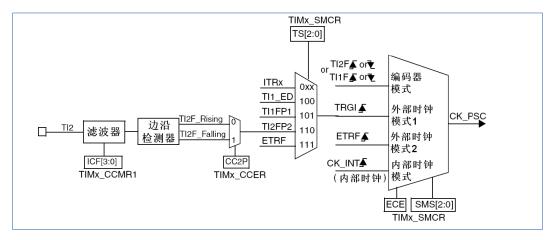

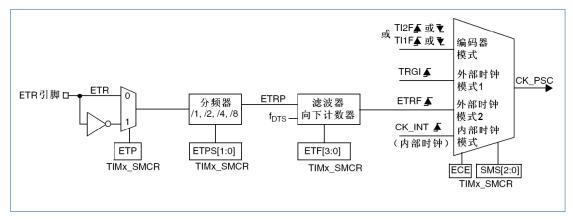

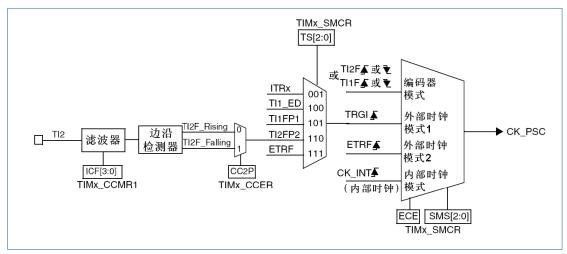

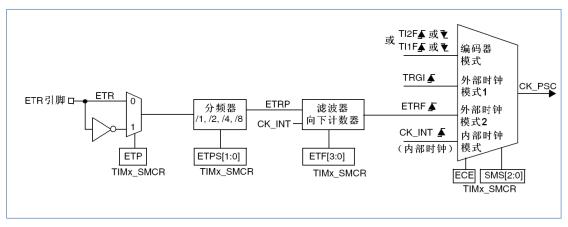

| 13.2.3 时钟选择                        | 177 |

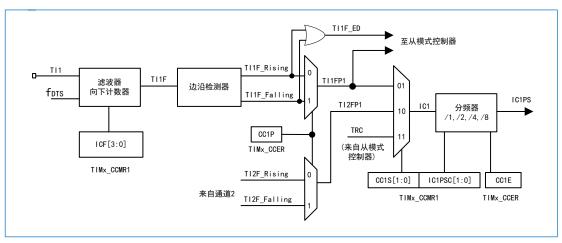

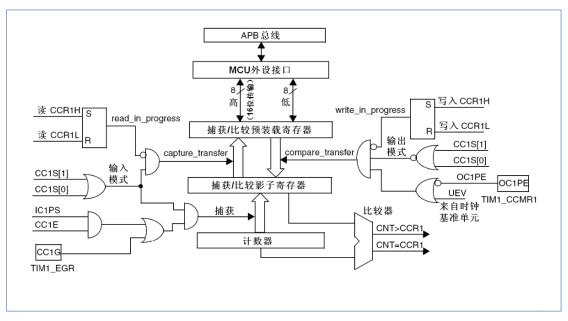

| 13.2.4 捕获/比较通道                     | 179 |

| 13.2.5 输入捕获模式                      | 181 |

| 13.2.6 PWM 输入模式                    | 181 |

| 13.2.7 强置输出模式                      | 182 |

| 13.2.8 输出比较模式                      | 182 |

| 13.2.9 PWM 模式                      | 183 |

| 13.2.9.1 PWM 边沿对齐模式                | 184 |

| 13.2.9.2 PWM 中央对齐模式                | 184 |

| 13.2.10 单脉冲模式                      | 185 |

| 13.2.11 在外部事件时清除 OCxREF 信号         | 187 |

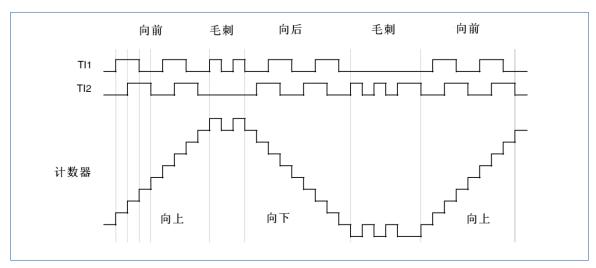

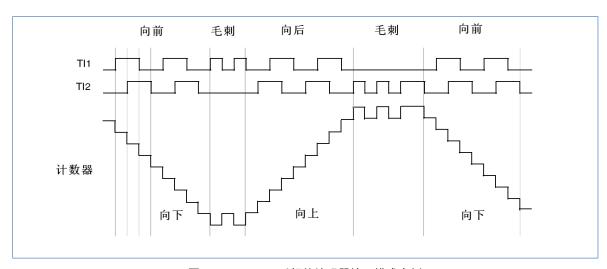

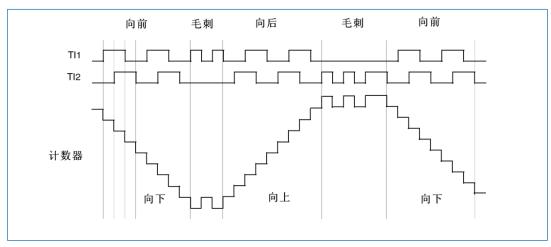

| 13.2.12 编码器接口模式                    | 187 |

| 13.2.13 定时器输入异或功能                  | 189 |

| 13.2.14 定时器和外部触发的同步                  | 189 |

|--------------------------------------|-----|

| 13.2.14.1 从模式: 复位模式                  | 189 |

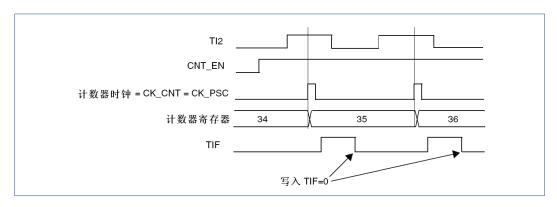

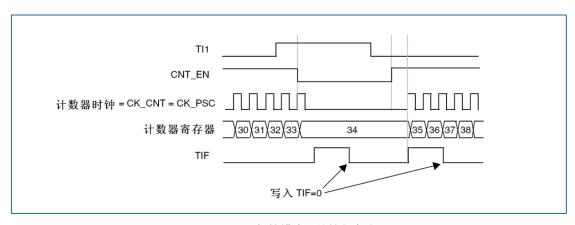

| 13.2.14.2 从模式: 门控模式                  | 190 |

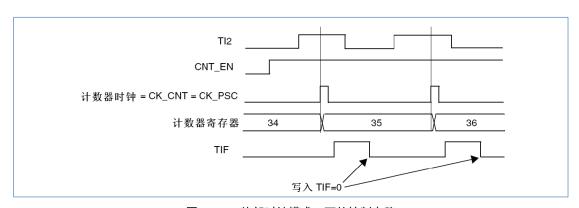

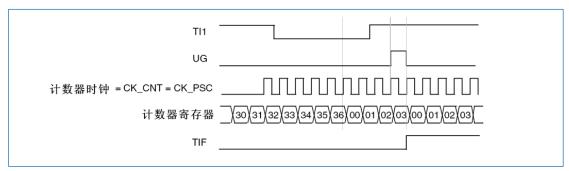

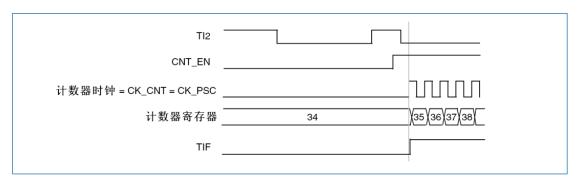

| 13.2.14.3 从模式: 触发模式                  | 190 |

| 13.2.14.4 从模式: 外部时钟模式 2+触发模式         | 191 |

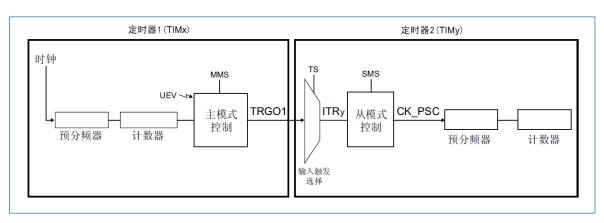

| 13.2.15 定时器同步                        | 191 |

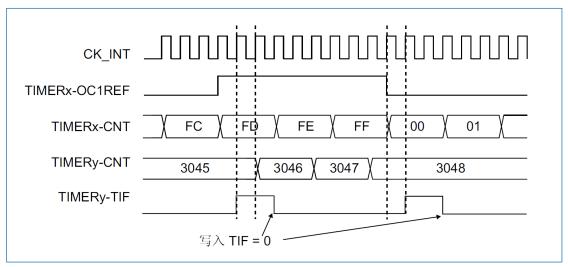

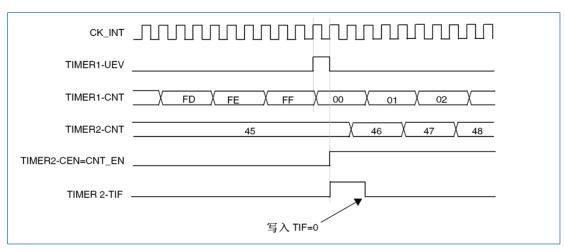

| 13.2.15.1 使用一个定时器作为另一个定时器的预分频器       | 192 |

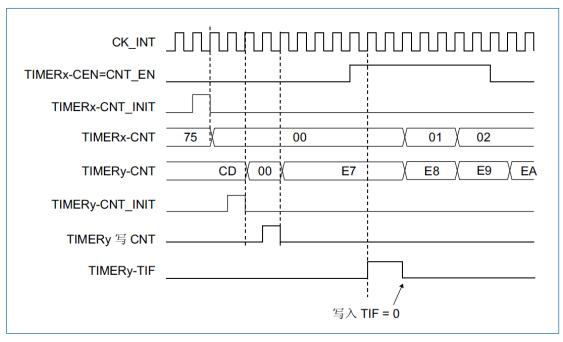

| 13.2.15.2 使用一个定时器使能另一个定时器            | 192 |

| 13.2.15.3 使用一个定时器去启动另一个定时器           | 194 |

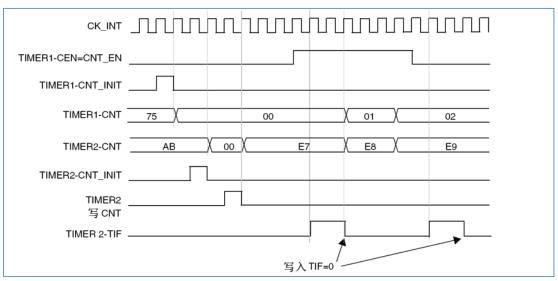

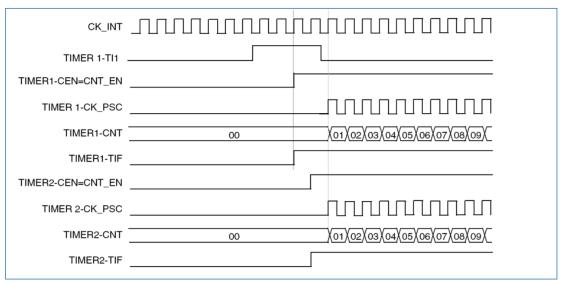

| 13.2.15.4 使用一个外部触发同步地启动 2 个定时器       | 195 |

| 13.2.16 调试模式                         | 196 |

| 13.3 TIM2 寄存器                        | 196 |

| 13.3.1 TIM2 控制寄存器 1(TIM2_CR1)        | 196 |

| 13.3.2 TIM2 控制寄存器 2(TIM2_CR2)        | 198 |

| 13.3.3 TIM2 从模式控制寄存器(TIM2_SMCR)      | 199 |

| 13.3.4 TIM2 中断允许寄存器(TIM2_DIER)       | 201 |

| 13.3.5 TIM2 状态寄存器(TIM2_SR)           | 202 |

| 13.3.6 TIM2 事件产生寄存器(TIM2_EGR)        | 203 |

| 13.3.7 TIM2 捕捉/比较模式寄存器 1(TIM2_CCMR1) | 204 |

| 13.3.8 TIM2 捕捉/比较模式寄存器 2(TIM2_CCMR2) | 207 |

| 13.3.9 TIM2 捕捉/比较使能寄存器(TIM2_CCER)    | 209 |

| 13.3.10 TIM2 计数器(TIM2_CNT)           | 210 |

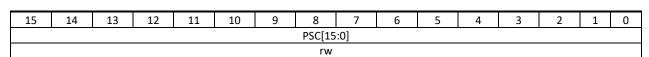

| 13.3.11 TIM2 预分频(TIM2_PSC)           | 210 |

| 13.3.12 TIM2 自动重装寄存器(TIM2_ARR)       | 211 |

| 13.3.13 TIM2 捕捉/比较寄存器 1(TIM2_CCR1)   | 211 |

| 13.3.14 TIM2 捕捉/比较寄存器 2(TIM2_CCR2)   | 212 |

| 13.3.15 TIM2 捕捉/比较寄存器 3(TIM2_CCR3)   | 212 |

| 13.3.16 TIM2 捕捉/比较寄存器 4(TIM2_CCR4)   | 213 |

| 14 基本定时器(TIM6)                       | 214 |

| 14.1 TIM6 主要功能                       | 214 |

| 14.2 TIM6 功能描述                       | 214 |

| 14.2.1 时基单元                    | 214 |

|--------------------------------|-----|

| 14.2.2 计数模式                    | 216 |

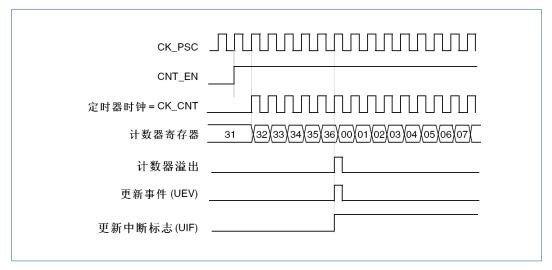

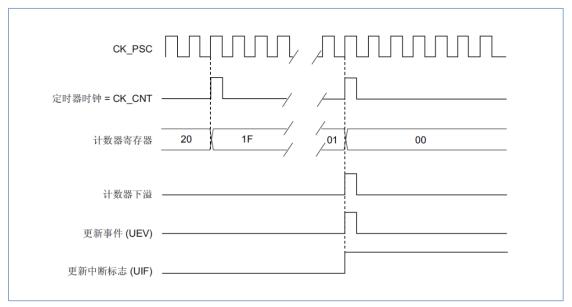

| 14.2.2.1 向上计数模式                | 216 |

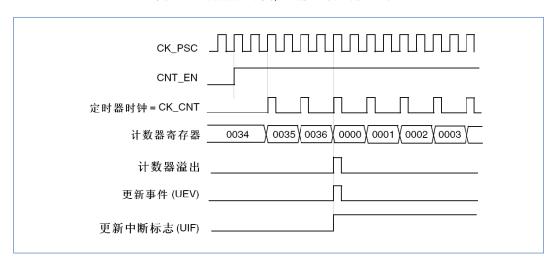

| 14.2.2.2 向下计数模式                | 218 |

| 14.2.3 时钟源                     | 221 |

| 14.2.4 调试模式                    | 221 |

| 14.3 TIM6 寄存器                  | 221 |

| 14.3.1 TIM6 控制寄存器 1(TIM6_CR1)  | 221 |

| 14.3.2 TIM6 控制寄存器 2(TIM6_CR2)  | 222 |

| 14.3.3 TIM6 中断使能寄存器(TIM6_DIER) | 223 |

| 14.3.4 TIM6 状态寄存器(TIM6_SR)     | 223 |

| 14.3.5 TIM6 事件产生寄存器(TIM6_EGR)  | 224 |

| 14.3.6 TIM6 定时器(TIM6_CNT)      | 224 |

| 14.3.7 TIM6 预分频器(TIM6_PSC)     | 224 |

| 14.3.8 TIM6 自动重装寄存器(TIM6_ARR)  | 225 |

| 15 自动唤醒定时器(AWU)                | 226 |

| 15.1 AWU 寄存器                   | 226 |

| 15.1.1 控制寄存器(AWU_CR)           | 226 |

| 15.1.2 控制寄存器(AWU_SR)           | 226 |

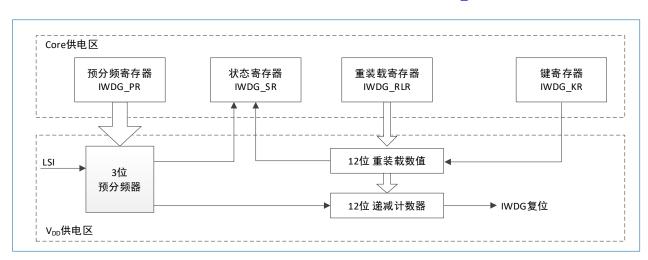

| 16 独立看门狗(IWDG)                 | 228 |

| 16.1 IWDG 主要功能                 | 228 |

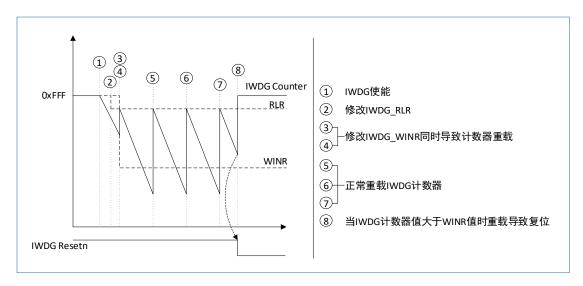

| 16.2 IWDG 功能描述                 | 228 |

| 16.2.1 窗口选项                    | 229 |

| 16.2.2 硬件看门狗                   | 230 |

| 16.2.3 寄存器访问保护                 | 230 |

| 16.2.4 调试模式                    | 230 |

| 16.3 IWDG 寄存器                  | 230 |

| 16.3.1 关键字寄存器(IWDG_KR)         | 230 |

| 16.3.2 预分频寄存器(IWDG_PR)         | 231 |

| 16.3.3 重加载寄存器(IWDG_RLR)        | 231 |

| 16.3.4 状态寄存器(IWDG_SR)          | 232 |

| 16.3.5 窗口寄存器(IWDG_WINR)            | 232 |

|------------------------------------|-----|

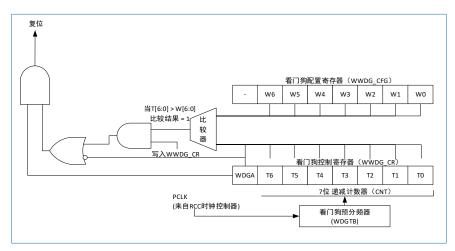

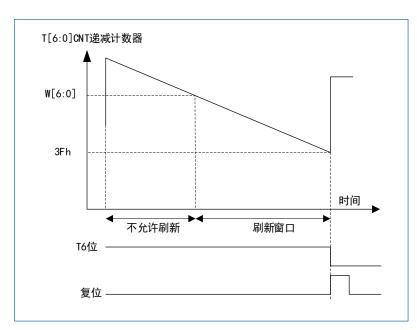

| 17 系统窗口看门狗(WWDG)                   | 234 |

| 17.1 WWDG 主要特性                     | 234 |

| 17.2 WWDG 功能描述                     | 234 |

| 17.2.1 启动看门狗                       | 234 |

| 17.2.2 控制递减计数器                     | 235 |

| 17.2.3 看门狗中断高级特性                   | 235 |

| 17.2.4 如何编写看门狗超时程序                 | 235 |

| 17.2.5 调试模式                        | 236 |

| 17.3 WWDG 寄存器                      | 236 |

| 17.3.1 控制寄存器(WWDG_CR)              | 236 |

| 17.3.2 配置寄存器(WWDG_CFR)             | 237 |

| 17.3.3 状态寄存器(WWDG_SR)              | 237 |

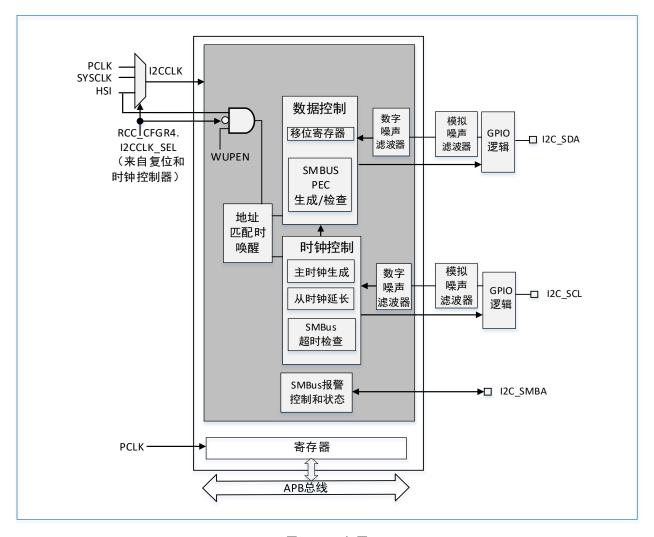

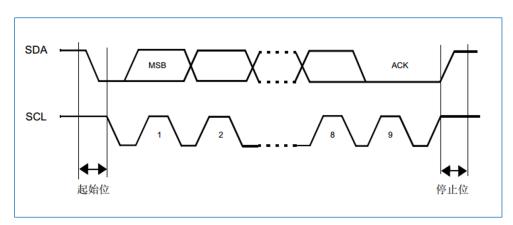

| 18 内部集成电路接口(I2C)                   | 238 |

| 18.1 I2C 主要特性                      | 238 |

| 18.2 I2C 功能说明                      | 238 |

| 18.2.1 I2C 框图                      | 239 |

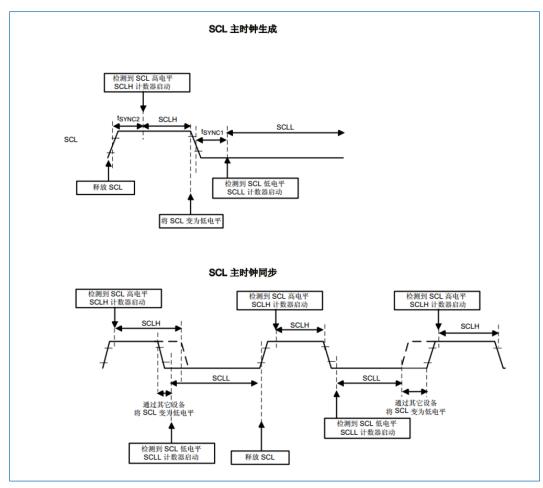

| 18.2.2 I2C 时钟要求                    | 239 |

| 18.2.3 模式选择                        | 240 |

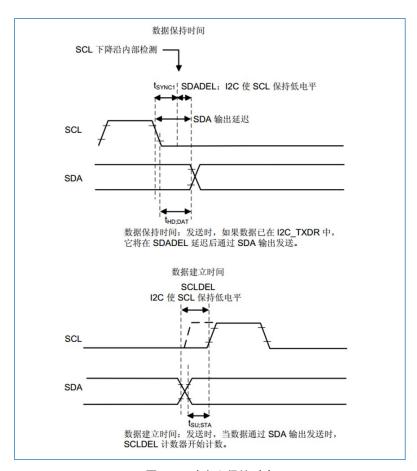

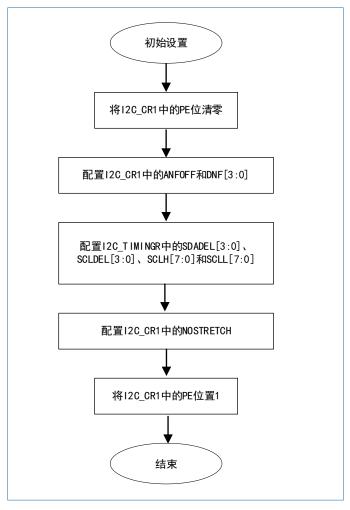

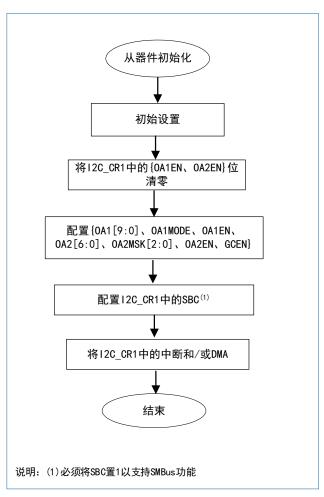

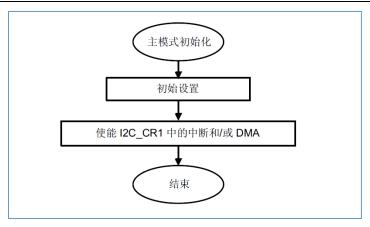

| 18.2.4 I2C 初始化                     | 240 |

| 18.2.5 软件复位                        | 244 |

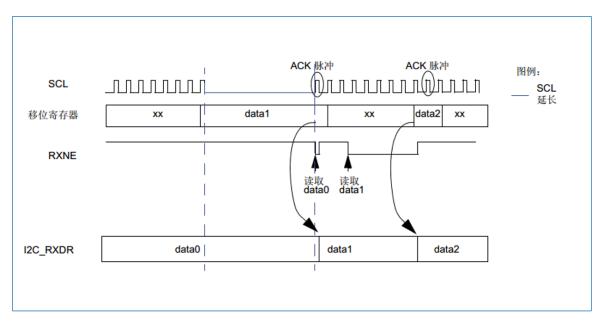

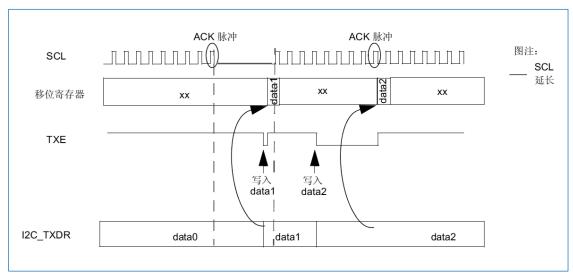

| 18.2.6 数据传输                        | 244 |

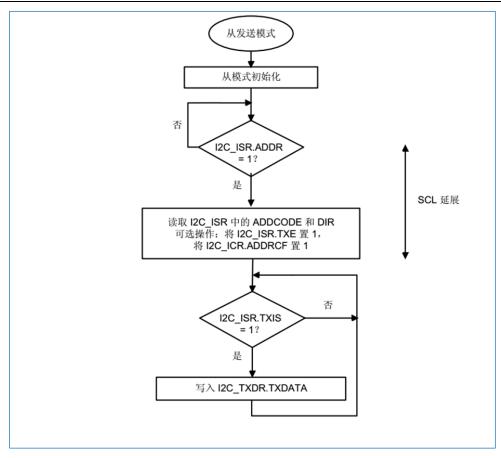

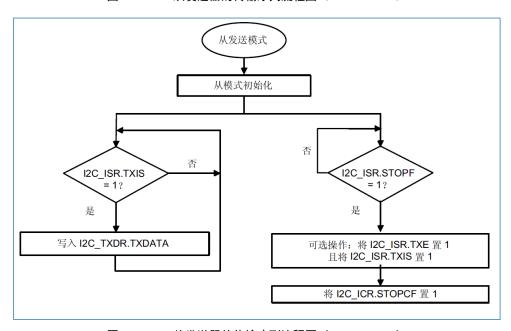

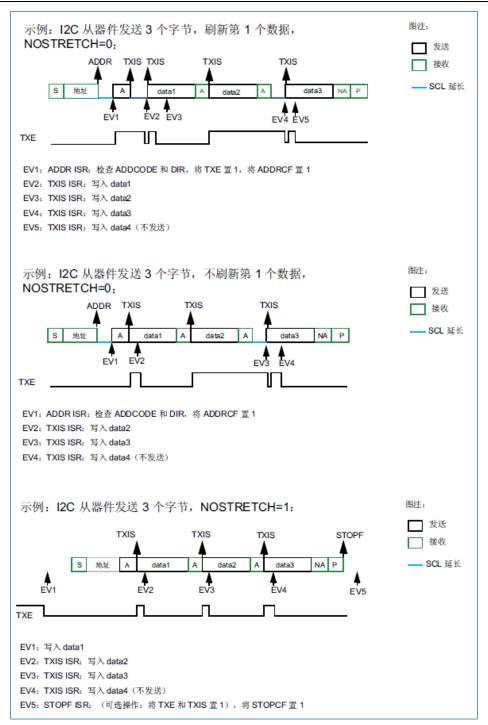

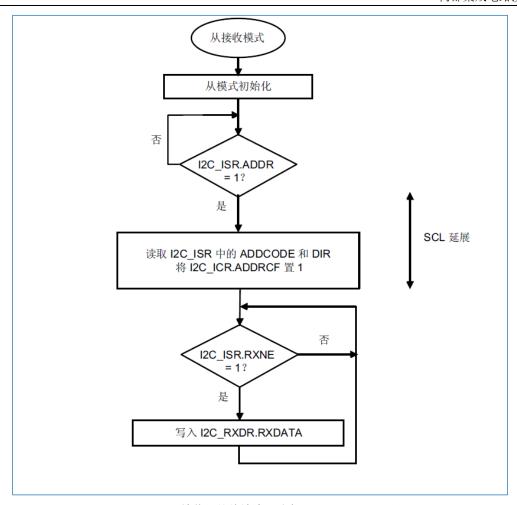

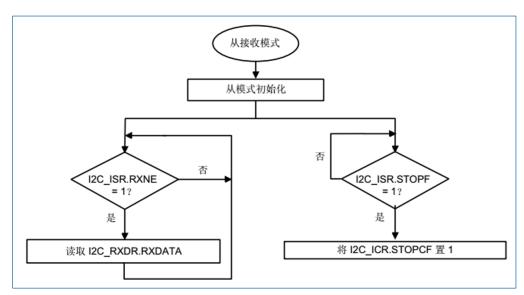

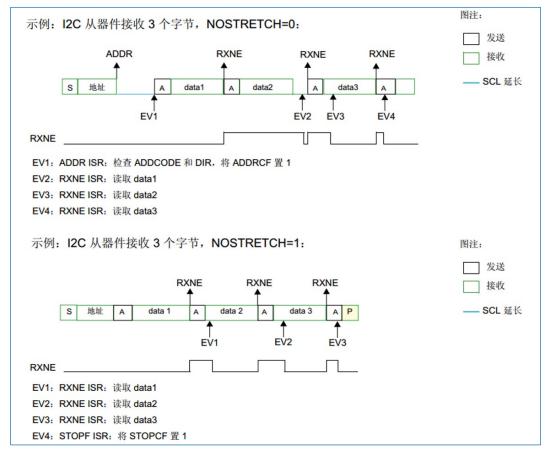

| 18.2.7 从模式                         | 247 |

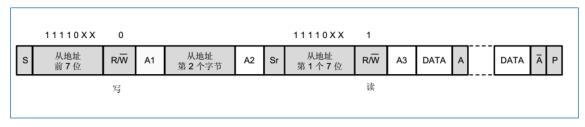

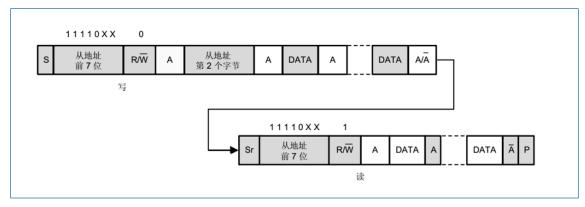

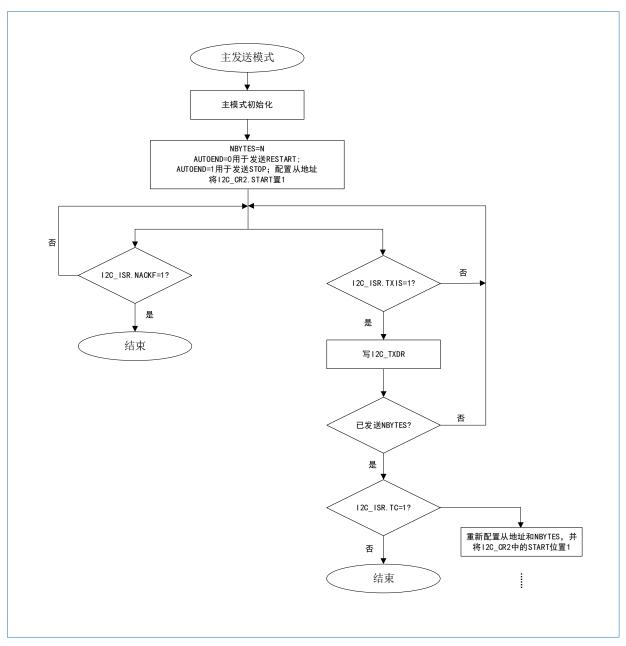

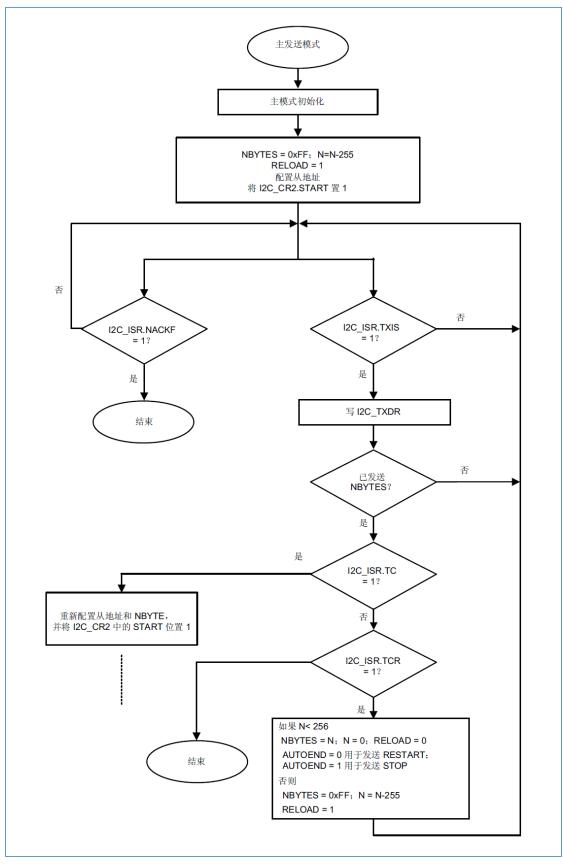

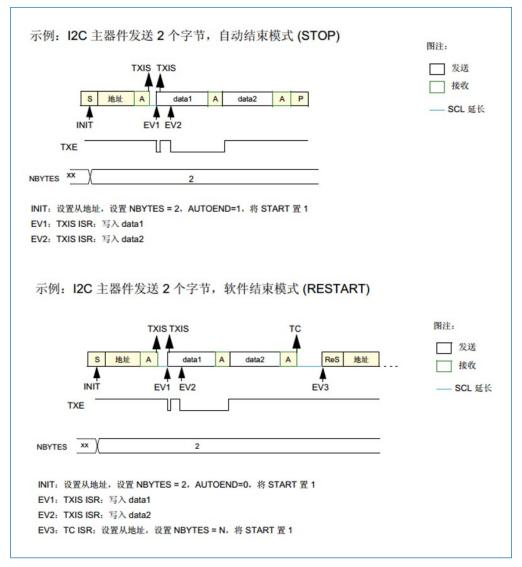

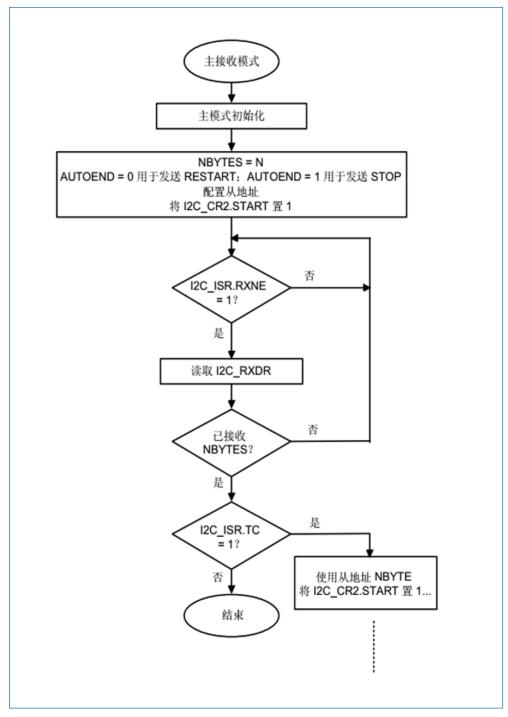

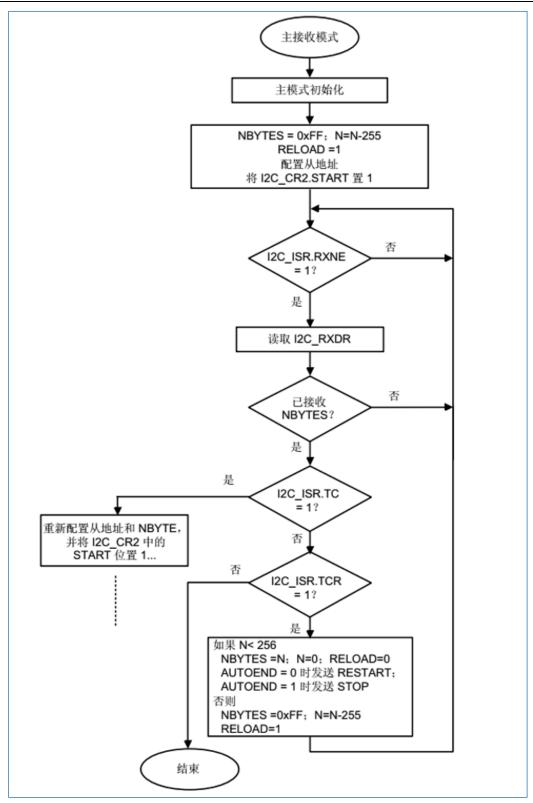

| 18.2.8 主模式                         | 253 |

| 18.2.9 I2C_TIMINGR 寄存器配置示例         | 262 |

| 18.2.10 SMBus I2C 特性               | 263 |

| 18.2.11 SMBus 初始化                  | 265 |

| 18.2.12 SMBus:I2C_TIMEOUTR 寄存器配置示例 | 267 |

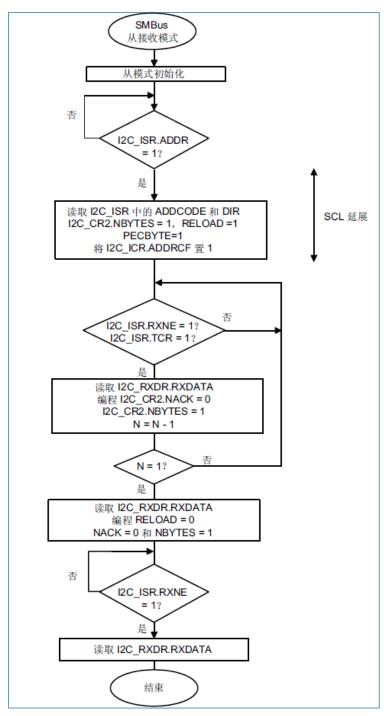

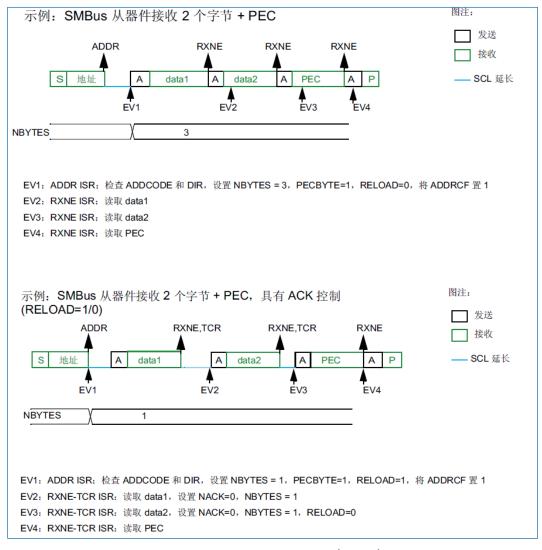

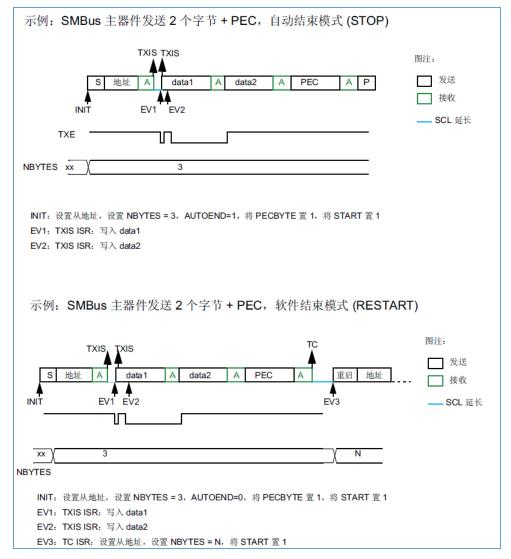

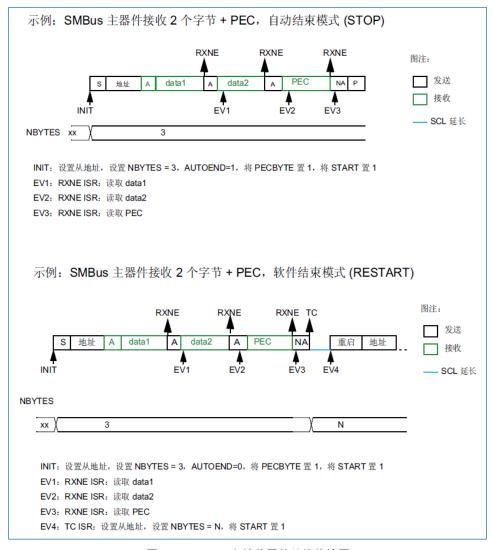

| 18.2.13 SMBus 模式                   | 267 |

| 18.2.14 地址匹配时从停机模式唤醒               | 272 |

| 18.2.15 错误条件                       | 273 |

|                                    |     |

| 18.2.16 调试模    | 三式                | 274 |

|----------------|-------------------|-----|

| 18.3 I2C 低功耗模式 | t                 | 274 |

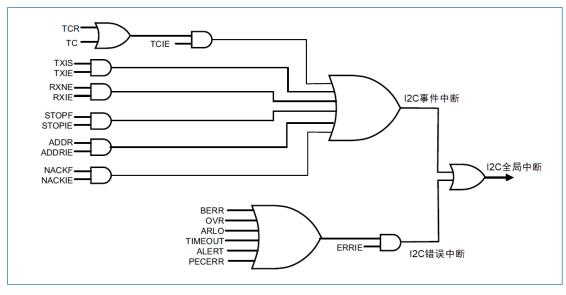

| 18.4 I2C 中断    |                   | 274 |

| 18.5 I2C 寄存器   |                   | 275 |

| 18.5.1 控制寄石    | 存器 1(I2C_CR1)     | 275 |

| 18.5.2 控制寄石    | 存器 2(I2C_CR2)     | 278 |

| 18.5.3 本机地均    | 业 1 寄存器(I2C_OAR1) | 280 |

| 18.5.4 本机地均    | 业 2 寄存器(I2C_OAR2) | 281 |

| 18.5.5 时序寄石    | 存器(I2C_TIMINGR)   | 282 |

| 18.5.6 超时寄石    | 存器(I2C_TIMEOUTR)  | 282 |

| 18.5.7 中断和4    | 状态寄存器(I2C_ISR)    | 283 |

| 18.5.8 中断清隆    | 徐寄存器(I2C_ICR)     | 285 |

| 18.5.9 PEC 寄存  | 字器(I2C_PECR)      | 286 |

| 18.5.10 接收数    | r据寄存器(I2C_RXDR)   | 287 |

| 18.5.11 发送数    | r据寄存器(I2C_TXDR)   | 287 |

| 19 通用同步异步收发器   | (USART)           | 288 |

| 19.1 USART 主要特 | 性                 | 288 |

| 19.2 USART 扩展特 | 性                 | 288 |

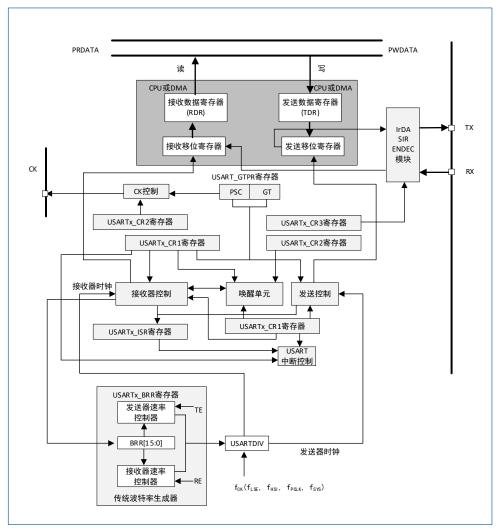

| 19.3 USART 实现  |                   | 289 |

| 19.4 USART 功能说 | 明                 | 289 |

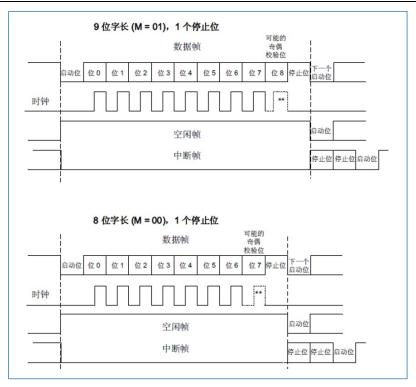

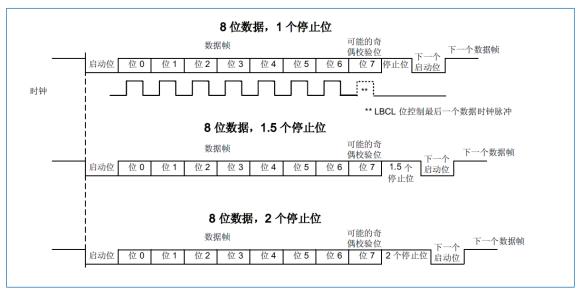

| 19.4.1 USART = | 字符说明              | 290 |

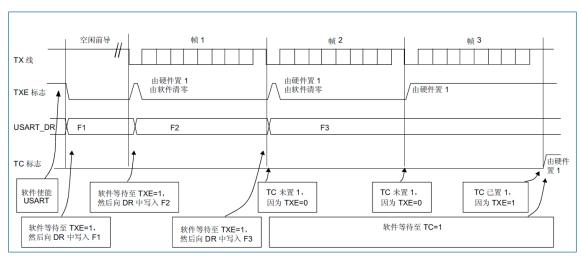

| 19.4.2 USART ½ | 发送器               | 291 |

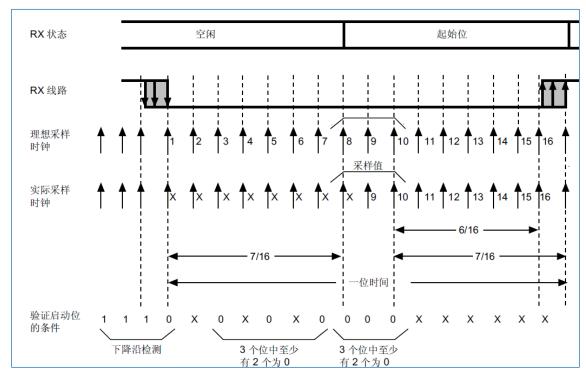

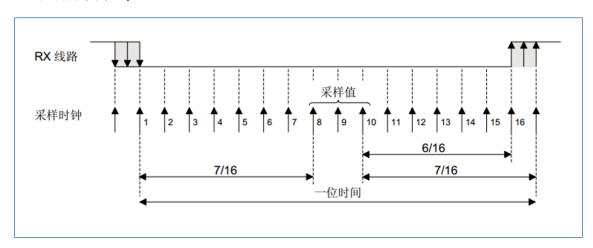

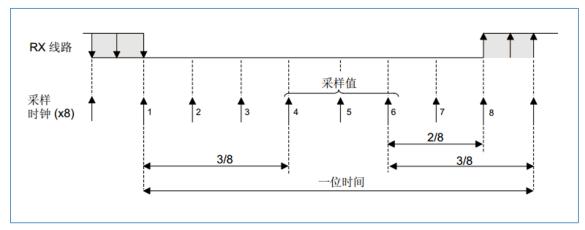

| 19.4.3 USART 挂 | 妾收器               | 293 |

| 19.4.4 USART 🖠 | 皮特率生成             | 296 |

| 19.4.5 USART   | 妾收器对时钟偏差的容差       | 298 |

| 19.4.6 USART 自 | 自动波特率检测           | 299 |

| 19.4.7 使用 US   | ART 进行多处理器通信      | 300 |

| 19.4.8 使用 US   | ART 进行 Modbus 通信  | 301 |

| 19.4.9 USART ₹ | 奇偶校验              | 301 |

| 19.4.10 USART  | LIN(局域互连网络)模式     | 302 |

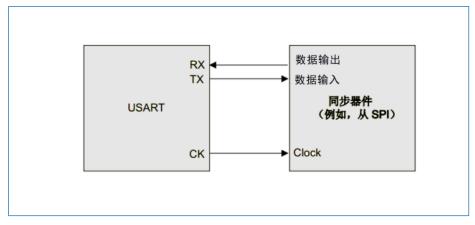

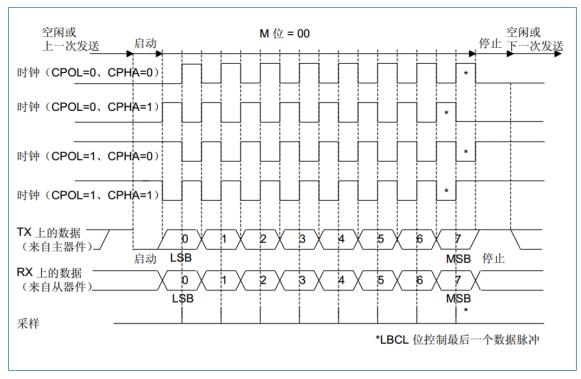

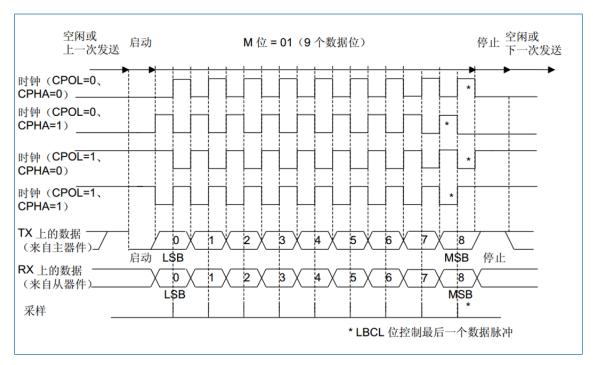

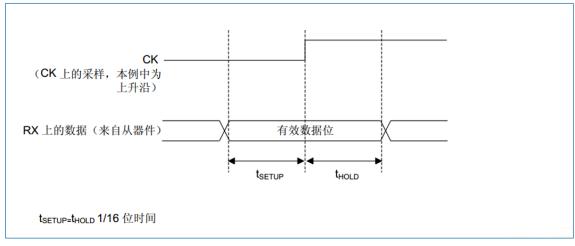

| 19.4.11 USART  | 同步模式              | 304 |

| 19.4.12 USART 单线半双工通信           | 306 |

|---------------------------------|-----|

| 19.4.13 USART 智能卡模式             | 306 |

| 19.4.14 USART IrDA SIR ENDEC 模块 | 309 |

| 19.4.15 RS485 驱动器使能             | 310 |

| 19.4.16 从停机模式唤醒                 | 310 |

| 19.5 USART 低功耗模式                | 311 |

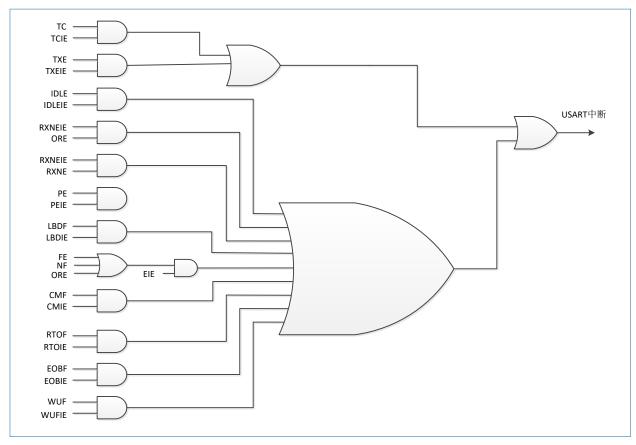

| 19.6 USART 中断                   | 311 |

| 19.7 USART 寄存器                  | 312 |

| 19.7.1 控制寄存器 1(USART_CR1)       | 312 |

| 19.7.2 控制寄存器 2(USART_CR2)       | 315 |

| 19.7.3 控制寄存器 3(USART_CR3)       | 319 |

| 19.7.4 波特率寄存器(USART_BRR)        | 322 |

| 19.7.5 保护时间和预分频器寄存器(USART_GTPR) | 322 |

| 19.7.6 接收超时寄存器(USART_RTOR)      | 323 |

| 19.7.7 请求寄存器(USART_RQR)         | 324 |

| 19.7.8 中断和状态寄存器(USART_ISR)      | 324 |

| 19.7.9 中断标志清除寄存器(USART_ICR)     | 328 |

| 19.7.10 数据接收寄存器(USART_RDR)      | 330 |

| 19.7.11 数据发送寄存器(USART_TDR)      | 330 |

| 20 串行外设接口(SPI/I2S)              | 331 |

| 20.1 SPI 和 I2S 主要特征             | 331 |

| 20.2 SPI 主要特征                   | 331 |

| 20.2.1   28 主要特征                | 331 |

| 20.3 SPI/I2S 实现                 | 332 |

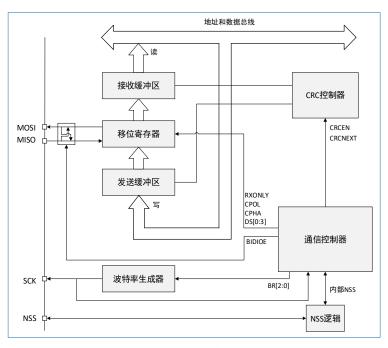

| 20.4 SPI 功能说明                   | 332 |

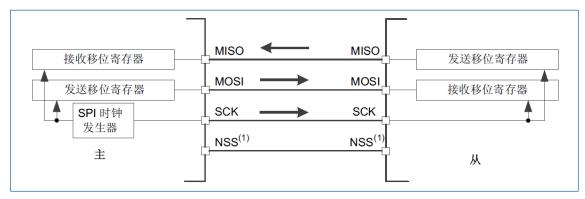

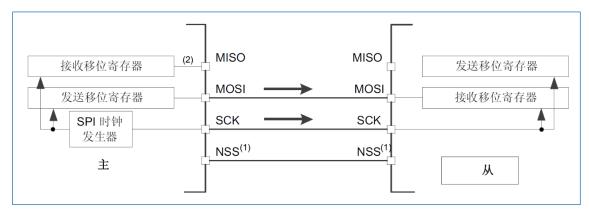

| 20.4.1 一个主器件和一个从器件之间的通信         | 333 |

| 20.4.1.1 全双工通信                  | 333 |

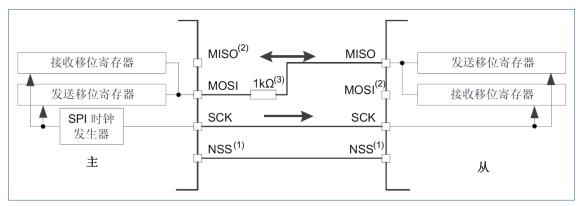

| 20.4.1.2 半双工通信                  | 333 |

| 20.4.1.3 单工通信                   | 334 |

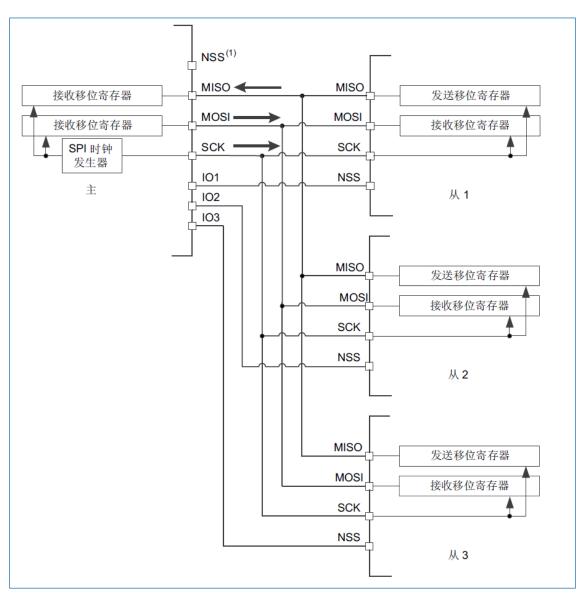

| 20.4.2 标准多从器件通信                 | 335 |

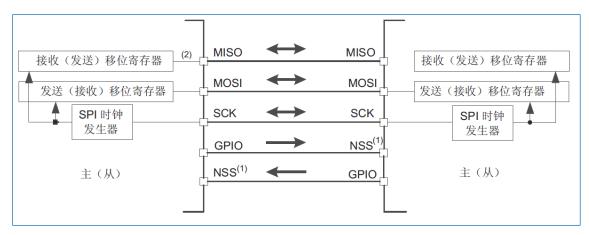

| 20.4.3 多主器件通信                   | 335 |

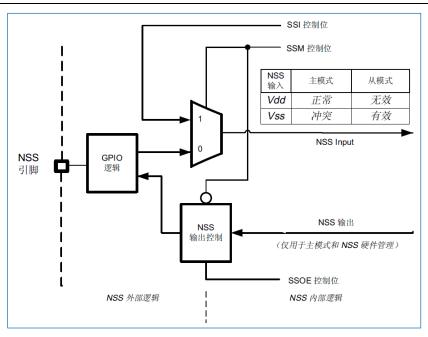

|     | 20.4.4 从器件选择(NSS)引脚管理        | 336 |

|-----|------------------------------|-----|

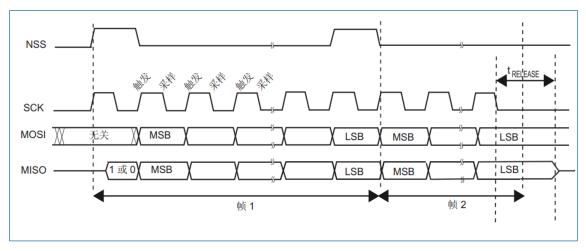

|     | 20.4.5 通信格式                  | 337 |

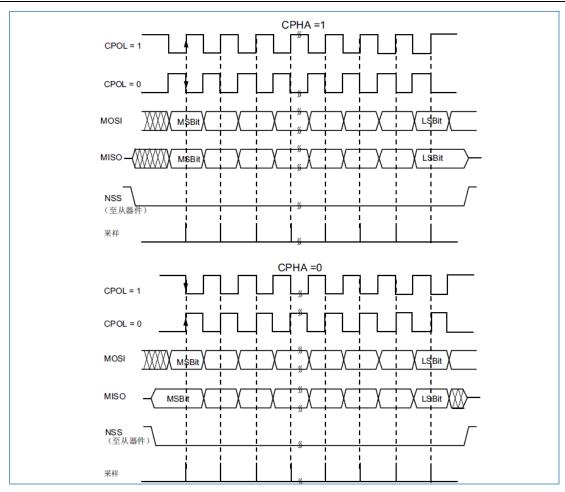

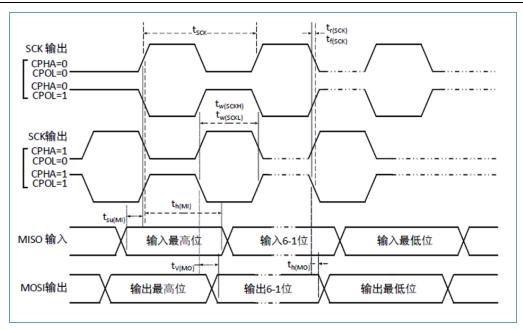

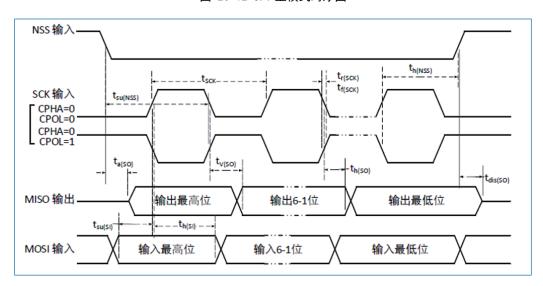

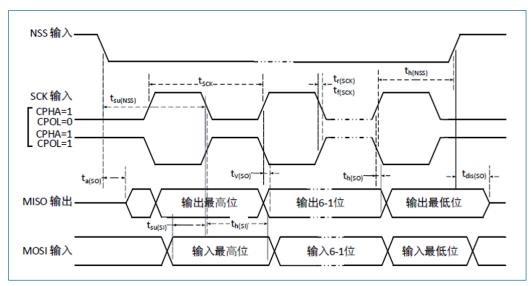

|     | 20.4.5.1 时钟相位和极性控制           | 337 |

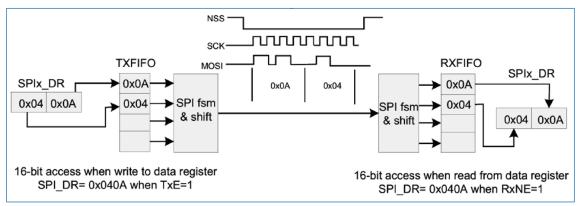

|     | 20.4.5.2 数据帧格式               | 338 |

|     | 20.4.6 SPI 配置                | 338 |

|     | 20.4.7 使能 SPI 步骤             | 339 |

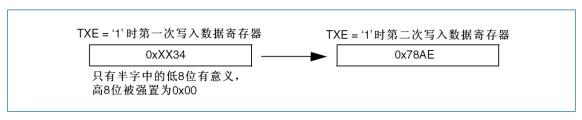

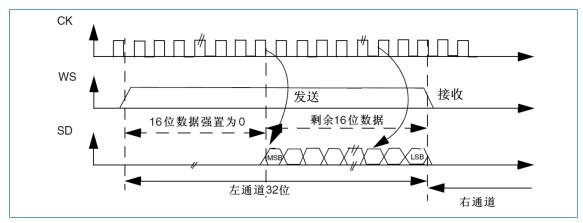

|     | 20.4.8 数据发送和接收过程             | 339 |

|     | 20.4.9 禁用 SPI 步骤             | 341 |

|     | 20.4.10 SPI 状态标志             | 342 |

|     | 20.4.11 SPI 错误标志             | 342 |

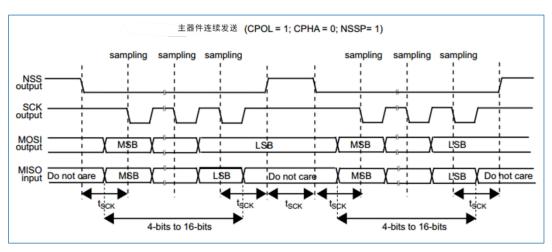

|     | 20.4.12 NSS 脉冲模式             | 343 |

|     | 20.4.13 TI 模式                | 344 |

|     | 20.4.14 CRC 计算               | 344 |

| 20. | 5 SPI 中断                     | 345 |

| 20. | 6 SPI 接口特性                   | 345 |

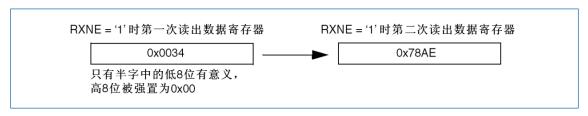

| 20. | 7 I2S 功能说明                   | 347 |

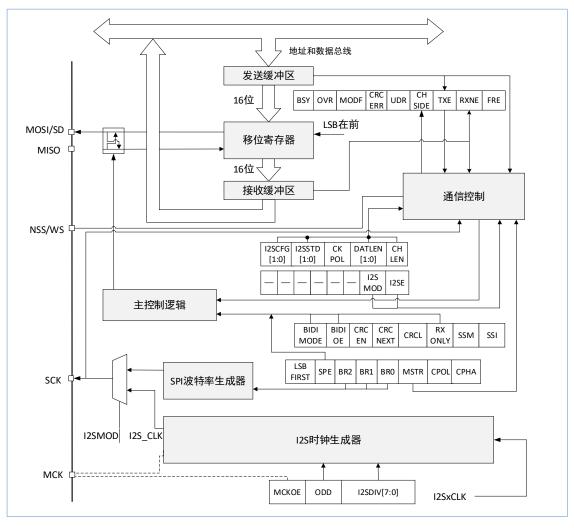

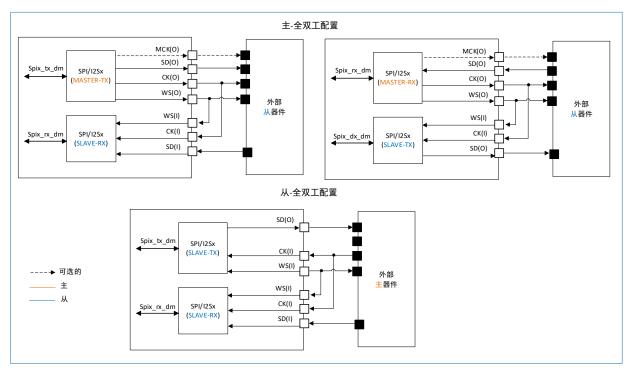

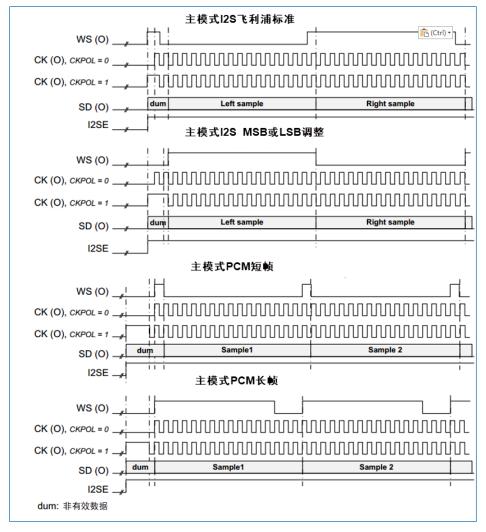

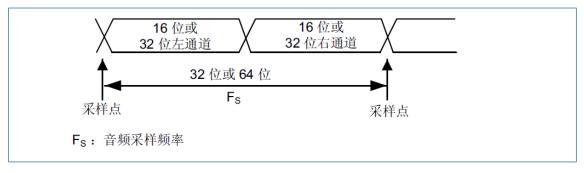

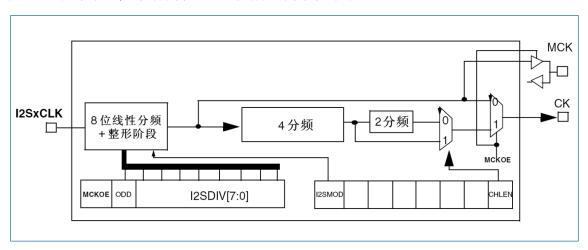

|     | 20.7.1   125 概述              | 347 |

|     | 20.7.2   25 全双工              | 349 |

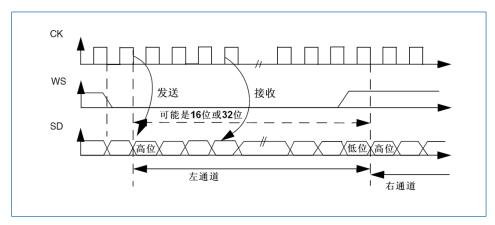

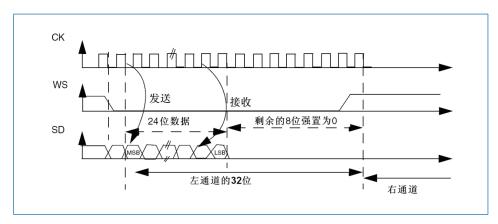

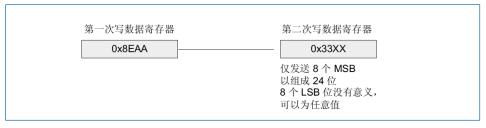

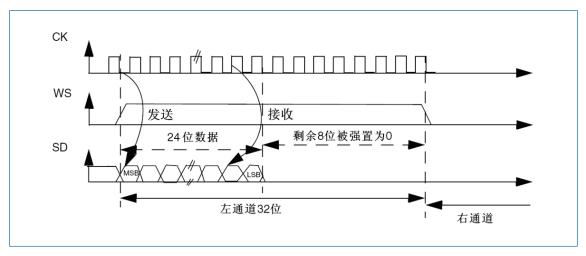

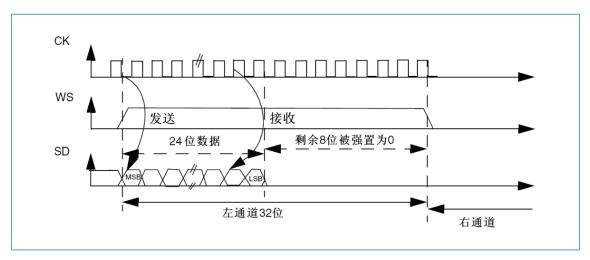

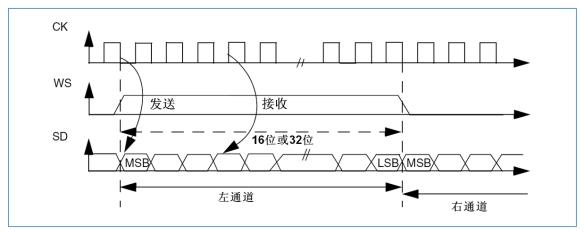

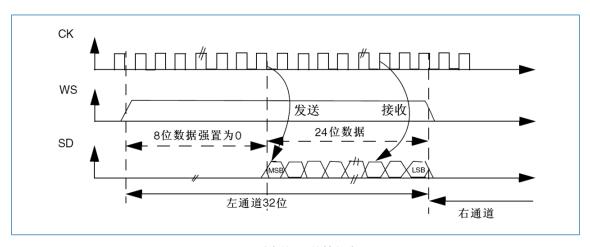

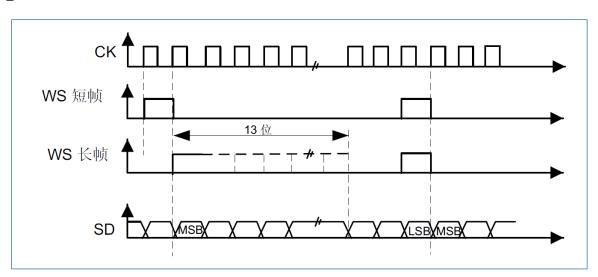

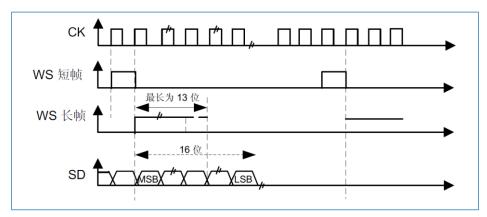

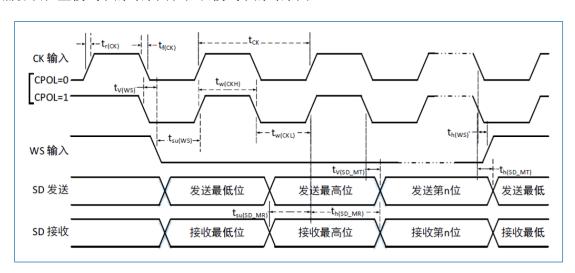

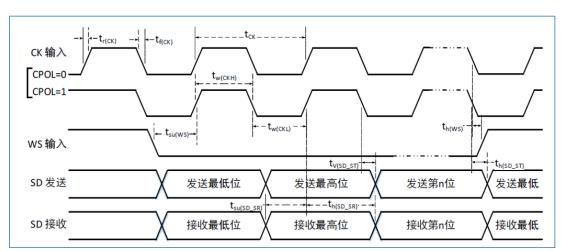

|     | 20.7.3 支持的音频协议               | 349 |

|     | 20.7.4 启动描述                  | 355 |

|     | 20.7.5 时钟发生器                 | 356 |

|     | 20.7.6   28 主模式              | 357 |

|     | 20.7.7 I2S 从模式               | 359 |

|     | 20.7.8   25 状态标志             | 360 |

|     | 20.7.9   12S 错误标志            | 361 |

| 20. | 8 I2S 中断                     | 361 |

| 20. | 9 I2S 接口特性                   | 362 |

| 20. | 10 SPI 寄存器                   | 363 |

|     | 20.10.1 SPI 控制寄存器 1(SPI_CR1) | 363 |

|     | 20.10.2 SPI 控制寄存器 2(SPI_CR2) | 365 |

|     | 20.10.3 SPI 状态寄存器(SPI_SR)    | 367 |

|      | 20.10.4 SPI 数据寄存器(SPI_DR)           | 368 |

|------|-------------------------------------|-----|

|      | 20.10.5 SPI 的 CRC 多项式寄存器(SPI_CRCPR) | 368 |

|      | 20.10.6 SPI 接收 CRC 寄存器(SPI_RXCRCR)  | 369 |

|      | 20.10.7 SPI 发送 CRC 寄存器(SPI_TXCRCR)  | 369 |

|      | 20.10.8 SPI_I2S 配置寄存器(SPI_I2SCFGR)  | 369 |

|      | 20.10.9 SPI_I2S 预分频寄存器(SPI_I2SPR)   | 371 |

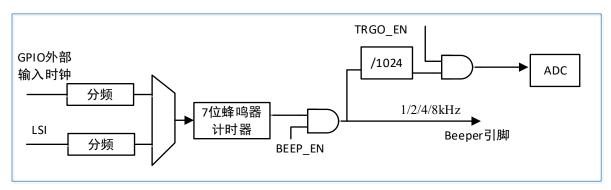

| 21 🖠 | 蜂鸣器(Beeper)                         | 372 |

|      | 21.1 蜂鸣器主要特性                        | 372 |

|      | 21.2 蜂鸣器功能说明                        | 372 |

|      | 21.2.1 蜂鸣器框图                        | 372 |

|      | 21.2.2 定时触发                         | 372 |

|      | 21.3 Beeper 寄存器                     | 372 |

|      | 21.3.1 配置寄存器(BEEP_CFGR)             | 372 |

|      | 21.3.2 控制寄存器(BEEP_CR)               | 373 |

| 22 j | 设备电子签名(UID)                         | 375 |

|      | 22.1 唯一设备 ID 寄存器(64 位)              | 375 |

|      | 22.1.1 UID 寄存器 0(U_ID0)             | 375 |

|      | 22.1.2 UID 寄存器 1(U_ID1)             | 375 |

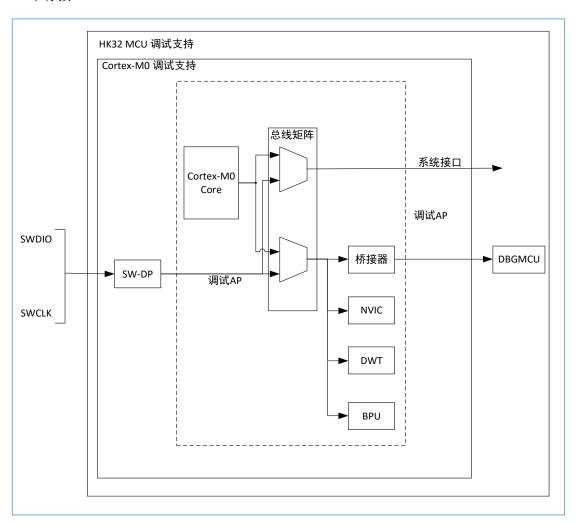

| 23 i | 调试支持(DBG)                           | 377 |

|      | 23.1 概述                             | 377 |

|      | 23.2 ARM®参考文档                       | 378 |

|      | 23.3 引脚排列和调试端口引脚                    | 378 |

|      | 23.3.1 SWD 端口引脚                     | 378 |

|      | 23.3.2 SW-DP 引脚分配                   | 378 |

|      | 23.3.3 SWD 引脚上的内部上拉和下拉              | 378 |

|      | 23.4 SWD 端口                         | 378 |

|      | 23.4.1 SWD 协议简介                     | 378 |

|      | 23.4.2 SWD 协议序列                     | 379 |

|      | 23.4.3 SW-DP 状态机(复位、空闲状态、ID 代码)     | 380 |

|      | 23.4.4 DP 和 AP 读/写访问                | 380 |

|      | 23.4.5 SW-DP 寄存器描述                  | 380 |

|      | 23.4.6 SW-AP 寄存器描述                       | 381 |

|------|------------------------------------------|-----|

|      | 23.5 内核调试                                | 381 |

|      | 23.6 BPU(断点单元)                           | 382 |

|      | 23.6.1 BPU 功能                            | 382 |

|      | 23.7 DWT(数据观察点)                          | 382 |

|      | 23.7.1 DWT 功能                            | 382 |

|      | 23.7.2 DWT 程序计数器采样寄存器                    | 382 |

|      | 23.8 MCU 调试组件(DBG)                       | 382 |

|      | 23.8.1 对低功耗模式的调试支持                       | 382 |

|      | 23.8.2 对定时器、看门狗和 I2C 的调试支持               | 383 |

|      | 23.9 DBGMCU 寄存器                          | 383 |

|      | 23.9.1 MCU 器件 ID 代码寄存器(DBGMCU_IDCODE)    | 383 |

|      | 23.9.2 调试 MCU 配置寄存器(DBGMCU_CR)           | 383 |

|      | 23.9.3 调试 MCU APB1 冻结寄存器(DBGMCU_APB1_FZ) | 384 |

| 24 绡 | <b>诸略语与术语</b>                            | 386 |

|      | 24.1 寄存器描述中的缩略语                          | 386 |

|      | 24.2 缩略语                                 | 386 |

|      | 24.3 术语                                  | 387 |

| 25   | 重要提示                                     | 388 |

# 1 简介

本文档为 HK32F0301M 系列芯片的用户手册。HK32F0301M 系列芯片是由深圳市航顺芯片技术研发有限公司研发的经济型 MCU 芯片,包括以下型号:

- HK32F0301MF4U6

- HK32F0301MF4N6

- HK32F0301MF4P6

- HK32F0301MD4P6

- HK32F0301MJ4M6

用户可以查看《HK32F0301M数据手册》,进一步了解HK32F0301M MCU 的功能特性,如外设接口、电气特性、管脚封装等。

# 2 系统及存储器概述

本章介绍了 HK32F0301M MCU 的系统架构和内部存储器。

# 2.1 系统架构

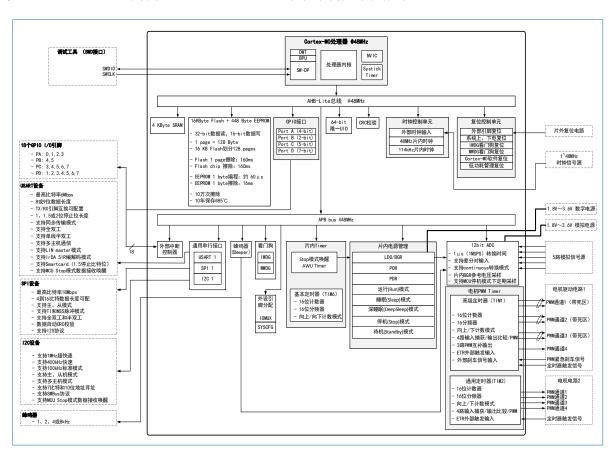

HK32F0301M MCU 主要包括以下几个模块:

- 主模块:

- 。 Cortex®-MO 内核和 AHB-Lite 总线

- 从模块:

- 。 内部 SRAM

- 。 内部 Flash 存储器

- 。 AHB-Lite 到 APB 的桥,所有的外设都挂在 APB 总线上

- 。 连接于 AHB-Lite 总线的 GPIO 口

以 HK32F0301MF4P6 为例,HK32F0301M MCU 系统架构如下图所示:

图 2-1 HK32F0301MF4P6 系统架构图

# 2.1.1 总线架构

• AHB-lite 到 APB 桥

AHB-lite 到 APB 桥在 AHB-lite 与 APB 总线间提供同步连接。

有关连接到桥的不同外设的地址映射,请参见图 2-2。

在每次复位之后,所有的外设时钟都关闭(除了 SRAM 及 FLIFT 外)。在用一个外设前,你必须打开

相应的 RCC AHBENR、RCC APBXENR 寄存器中时钟使能位。

说明: 当对 APB 寄存器进行 8 位或者 16 位访问时,该访问会被自动转换成 32 位的访问: 桥会自动 将 16 位或者 8 位的数据扩展以配合 32 位的宽度。

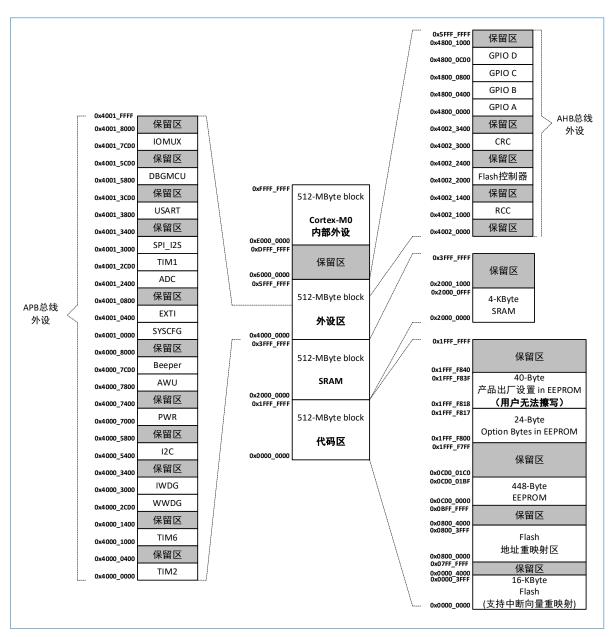

### 2.2 存储器映射及寄存器编址

程序存储器、数据存储器、寄存器及 I/O 口统一编址,其线性地址空间达到 4G Byte。HK32F0301M MCU 支持小端模式的数据存储,即数据的低字节存放于低地址,数据的高字节存放于高地址。

存储器的寻址空间可分成8块,每块512M Byte。存储器内的保留区是指暂时未分配给片上存储器和外设的地址空间。

以 HK32F0301MF4P6 为例,HK32F0301M MCU 存储器映射如下图所示:

图 2-2 HK32F0301MF4P6 存储器映射

#### **2.3 SRAM**

HK32F0301M MCU 内置 4 Kbyte 的 SRAM, 起始地址是 0x2000 0000。SRAM 可以字节(8位)、半字(16位)或字(32位)方式进行访问。CPU 可使用最快的系统时钟且不插入等待周期访问 SRAM。

SRAM 不支持硬件奇偶校验。

### 2.4 启动配置

系统复位等待至启动延迟时间结束之后,CPU 获取 Flash 地址 0x0000 0000 中存储的堆栈顶地址,然 后从 Flash 地址 0x0000 0004 处开始执行代码。

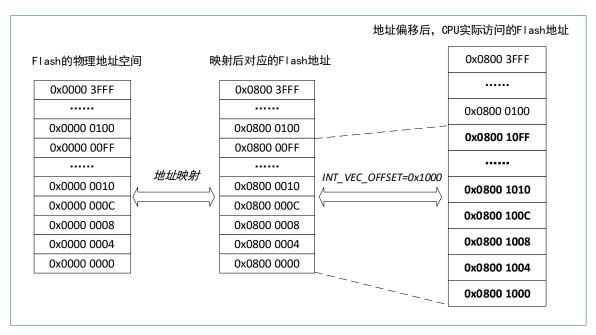

系统启动后,应用程序可通过修改 SYSCFG\_CFGR1 寄存器中的 MEM\_MODE 位来重新映射存储器地址。与 Cortex-M3®和 Cortex®-M4 内核不同,Cortex®-M0 内核不支持中断向量表(Interrupt Vector Table,IVT)重映射,但 HK32F0301M MCU 支持通过配置 INT\_VEC\_OFFSET 寄存器实现 IVT 重映射功能。

例如,实现在线升级(In Application Programming,IAP)功能,一种方法是用户将中断向量表重映射到 SRAM:

- 1. 将中断向量表从 Flash 拷贝到 SRAM 的起始地址 0x2000 0000。

- 2. 配置 SYSCFG\_CFGR1 寄存器的 MEM\_MODE[1:0],以实现 SRAM 映射到 Flash 的地址 0x0000 0000。

- 3. 当有中断发生时,CPU 从重映射到 SRAM 中的 IVT 取中断服务程序地址,然后跳转到 Flash 中执行中断服务程序。

另外一种方法是通过配置 INT\_VEC\_OFFSET 寄存器将 IVT 重映射到 Flash 地址。配置完成之后,若有中断发生,CPU 从重映射到 Flash 中的 IVT 取中断服务程序地址,然后跳到 Flash 中执行中断服务程序。

### 3 Flash

Flash 接口遵循 AHB 协议执行指令和数据存取。

# 3.1 Flash 特性

- Flash 结构

- 最高 16K 字节主 Flash 块

- 应用程序区

- 用户数据区

- 。 信息块,其包括:

- 选项字节(Option byte):内含硬件及存储保护用户配置选项。

- 448 字节 EEPROM

- Flash 编程/擦除操作

- 访问/写保护

- Flash 访问位宽: 支持半字(16位)写; 32位读

- 低功耗模式

### 3.2 Flash 功能

### 3.2.1 Flash 结构

Flash 空间由 32 位宽的存储单元组成,可存储代码和数据。

主 Flash 块可分为 128 页,每页 128 字节。

Flash 选项字节域共有 24 个字节。

表 3-1 Flash 结构

| 地址                      | 大小(字节)   | 页号      | 描述        |

|-------------------------|----------|---------|-----------|

| 0x0800 0000-0x0800 007F | 128 Byte | Page0   | 主 Flash 块 |

| 0x0800 0080-0x0800 00FF | 128 Byte | Page1   |           |

| 0x0800 0100-0x0800 017F | 128 Byte | Page2   |           |

| 0x0800 0180-0x0800 01FF | 128 Byte | Page3   |           |

|                         |          |         |           |

| 0x0800 1E00-0x0800 1E7F | 128 Byte | Page60  |           |

| 0x0800 1E80-0x0800 1EFF | 128 Byte | Page61  |           |

| 0x0800 1F00-0x0800 1F7F | 128 Byte | Page62  |           |

| 0x0800 1F80-0x0800 1FFF | 128 Byte | Page63  |           |

|                         |          |         |           |

| 0x0800 3E00-0x0800 3E7F | 128 Byte | Page124 |           |

| 地址                      | 大小(字节)   | 页号      | 描述   |

|-------------------------|----------|---------|------|

| 0x0800 3E80-0x0800 3EFF | 128 Byte | Page125 |      |

| 0x0800 3F00-0x0800 3F7F | 128 Byte | Page126 |      |

| 0x0800 3F80-0x0800 3FFF | 128 Byte | Page127 |      |

| 0x1FFF F800-0x1FFF F817 | 24 Byte  | -       | 选项字  |

| 0x1FFF F818-0x1FFF F83F | 40 Byte  | -       | 系统配置 |

### 3.2.2 读操作

嵌入式 Flash 模块可以直接寻址访问。任何对该 Flash 内容的读操作都须经过专门的判断过程。

指令和数据的访问都是通过 AHB 总线完成,并按照 Flash 访问控制寄存器(Flash\_ACR)所指定的等待周期进行访问。

### 3.2.3 读保护

将选项字节中的RDP 字节置位,然后重新复位,读保护功能则被激活。系统存储区不受读保护字节的影响,但该区域不允许编程和擦除操作。Flash 存储器的读保护级别和 RDP 选项字节及其按位取反之后的内容的对应关系,如下表:

| RDP 字节值             | RDP 按位取反之后的值                 | 读保护级别       |

|---------------------|------------------------------|-------------|

| ОхАА                | 0x55                         | Level 0     |

| 任意值,除 0xAA 和 0xCC 外 | 任意值(不要求按位取反),除 0x55 和 0x33 外 | Level 1(默认) |

| 0xCC                | 0x33                         | Level 2     |

表 3-2 读保护级别/RDP 字节及其按位取反值的对应关系

读保护状态包括三个级别:

• Level 0: 无保护

允许对主 Flash 区域和选项字节进行读写和擦除操作。

• Level 1: 读保护

这是 RDP 选项字节被擦除之后的默认保护级别。对应的 RDP 值为除 0xAA 和 0xCC 以外的任意值或者其按位取反之后的值。

- 。 用户模式:在用户模式下执行的代码允许对主 Flash 和选项字节做全部操作。

- 。 调试模式:包括 boot RAM。在调试模式下或运行在 boot RAM 状态下,不允许访问主 Flash 区和备份寄存器。在调试模式下,任何简单的读访问都会引起总线错误并引发硬件错误中断。主 Flash 区也禁止写和擦除操作,以防范恶意程序修改代码。当 RDP 字节的内容被重新改为 Level 0(0xAA)的级别时,CPU 硬件先执行整片擦除操作,并且备份寄存器也会被复位。

- Level 2: 不支持调试

Level 2 包含了 Level 1 的保护功能,且 Cortex M0 的调试接口被禁止了,也不支持从 RAM 启动、系统区启动等功能。

在用户模式下,允许对主 Flash 区进行读写和擦除操作;但选项字节区仅支持读取和写入操作,不支持擦除操作。

在 Level 2 级别时,不能改写 RDP 字节,因此 Level 2 保护级别不能被清除。设置为 Level 2 是不可恢复的操作。当试图改写 RDP 字节时,FLASH\_SR 寄存器中的保护错误标志 WRPRTERR 会被置位并引发一个中断。

| 区域         | 保护 |    |                   | 调试/从 RAM 或从系统区域启动 |                   |                   |                   |

|------------|----|----|-------------------|-------------------|-------------------|-------------------|-------------------|

|            | 级别 | 读  | 写                 | 擦除                | 读                 | 写                 | 擦除                |

| 主 Flash 区域 | 1  | 允许 | 允许                | 允许                | 禁止                | 禁止                | 禁止 <sup>(3)</sup> |

|            | 2  | 允许 | 允许                | 允许                | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> |

| 系统区域       | 1  | 允许 | 禁止                | 禁止                | 允许                | 禁止                | 禁止                |

|            | 2  | 允许 | 禁止                | 禁止                | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> |

| 选项字节       | 1  | 允许 | 允许 <sup>(2)</sup> | 允许                | 允许                | 允许 <sup>(3)</sup> | 允许                |

|            | 2  | 允许 | 允许 <sup>(3)</sup> | 禁止                | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> |

| 备份寄存器      | 1  | 允许 | 允许                | 允许                | 禁止                | 禁止                | 允许                |

|            | 2  | 允许 | 允许                | 允许                | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> | 禁止 <sup>(1)</sup> |

表 3-3 不同工作模式下保护级别和保护状态的对应关系

- (1). 当使能 Level2 保护级别,调试口被禁止从 RAM/系统启动。

- (2). 当 RDP 被改成不保护时, 主 Flash 会被擦除。

- (3). 除 RDP 以外的其他选项字节均能被再次编程。

### 3.2.3.1 改变读保护级别

修改 RDP 的值(除 0xCC 以外的值)就能将读保护级别从 Level 0 级迁移到 Level 1 级别。将 RDP 写入 0xCC,就可以直接进入 Level 2 级别。从 level 1 进入到 Level 0,一定会经过整片擦除阶段。因为在修改 RDP 成功进入到 Level 0 之前,MCU 已经启动了整片擦除。

## 3.2.4 写保护

写保护是通过配置选项字节中的 WRP 位,然后重新复位系统以使能写保护功能。一共 32 位写保护控制位,每个 WRP 比特置位对应保护 512 byte 主 Flash。

说明: 仅当 WRP 和 nWRP 具有按位互反关系时,写保护才能生效。

如果写入或擦除一个受写保护的扇区,会引起 FLASH SR 中的 WRPRTERR 标志位被置位。

#### 写保护的解除

以下是解除写保护操作的实例:

- 1. 置位 FLASH CR 中的 OPTER 位擦除整个选项字节区域。

- 2. 向 RDP 写入 0xAA 从而解除所有保护,这会引起整片擦除。

#### 选项字节的写保护

选项字节默认被写保护且随时可读。必须先向 FLASH\_OPTKEYR 寄存器顺序写入关键字,才能对选项字节进行写/擦除操作。填入正确的关键字会引起 FLASH\_CR 中的 OPTWRE 置位,表明解锁成功;通过对 OPTWRE 位清零,能够禁止对选项字节的写操作。

### 3.2.5 主 Flash 写和擦除操作

电路编程(In Circuit Programing,ICP)使用 SWD 或 Bootloader 的方法在线改变 Flash 的内容,将用户代码烧录到 MCU 中。ICP 提供了一种简单高效的方法,免除了烧写芯片时的芯片装夹等问题。

与 ICP 方法不同的是,IAP 能够使用 MCU 支持的任何通信接口下载程序或者数据。IAP 允许用户在运行程序的过程中重写应用程序,前提是 IAP 的烧录引导程序已经写入 MCU。

写和擦除操作在整个产品工作电压范围内都可以完成。该操作涉及以下寄存器的配置:

- Flash 关键字寄存器(FLASH KEYR)

- Flash 状态寄存器(FLASH\_SR)

- Flash 控制寄存器(FLASH\_CR)

- Flash 地址寄存器(FLASH AR)

- 写保护寄存器(FLASH WRPR)

在写/擦除 Flash 时,不能对 Flash 进行取指或数据访问,并且任何中断请求亦不会被响应。此时,中断会被 CPU 内核挂起,直到写/擦除完成之后才会响应中断。只要 CPU 不访问 Flash 空间,进行中的 Flash 写操作不会影响 CPU 的运行。即在对 Flash 进行写/擦除操作时,任何对 Flash 的访问都会令总线停顿,直到写/擦操作完成后才会继续执行 Flash 的访问。

在对 Flash 进行写/擦除操作时,内部 RC 振荡器(HSI)必须处于开启状态。

#### 3.2.5.1 主 Flash 空间的解锁

复位后,Flash 存储器默认处于受保护状态,以避免意外擦除。FLASH\_CR 寄存器的值通常不允许改写。只有对 FLASH\_KEYR 寄存器进行解锁操作后,才具有对 FLASH\_CR 寄存器的访问权限。FLASH\_KEYR 寄存器的解锁操作包括以下步骤:

- 1. 向 FLASH KEYR 寄存器写入关键字 KEY1=0x45670123;

- 2. 向 FLASH KEYR 寄存器写入关键字 KEY2=0xCDEF89AB。

错误的操作顺序将会锁死 FLASH\_CR 直至下次复位。当写入关键字错误时,会由总线错误触发一次硬件错误中断。

- 如果 KEY1 出错,就会立即触发中断。

- 如果 KEY1 正确且 KEY2 错误时,就会在 KEY2 错的时刻触发中断。

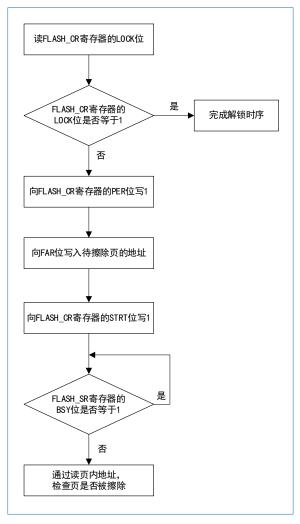

#### 3.2.5.2 主 Flash 擦除

主 Flash 存储器可以按页为单位擦除,也可以整片擦除。

注意:

HK32F0301M 系列芯片擦除后为趋近于 0 的随机值。

擦除页

图 3-1 Flash 擦除页的流程

#### 擦除页的操作步骤:

- 1. 检查 FLASH SR 寄存器中的 BSY 位,以确认上次操作已经结束。

- 2. 将 FLASH\_CR 寄存器中的 PER 位置为 1,以选择按页擦除。

- 3. 写 FLASH AR 寄存器的 FAR 位,写入待擦除页的地址。

- 4. 将 FLASH\_CR 寄存器中的 STRT 位置为 1,以启动擦除操作。

- 5. 将 FLASH CR 寄存器中的 PER 位置 0,以恢复默认值。

- 6. 等待 FLASH SR 中的 BSY 变为 0,表明擦除操作完成。

- 7. 检查 FLASH SR 寄存器的 EOP 标志(若 Flash 擦除成功会置位 EOP),然后软件清除该标志位。

#### • 整片擦除

整片擦除命令可以一次擦除整个 Flash 扇区。整片擦除的具体步骤如下:

- 1. 检查 FLASH\_SR 寄存器的 BSY 位,以确认上次操作已经结束。

- 2. 将 FLASH\_CR 寄存器中的 MER 位置 1,以启动整片擦除。

- 3. 将 FLASH\_CR 寄存器中的 STRT 位置为 1,以启动擦除操作。

- 4. 将 FLASH\_CR 寄存器中的 MER 位置 0,以禁止整片擦除。

- 5. 等待 FLASH SR 中的 BSY 位置 0,整片擦除操作结束。

- 6. 检查 FLASH\_SR 寄存器的 EOP 标志位(如果 Flash 擦除成功会置位 EOP),然后软件清除该标志位。

说明:整片擦除命令对信息块不起作用。

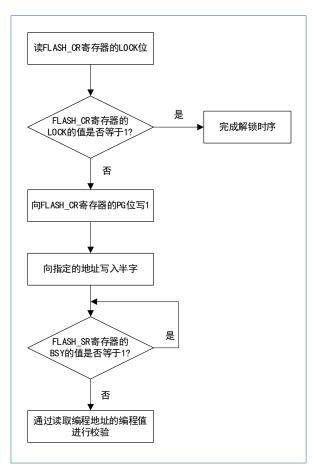

#### 3.2.5.3 主 Flash 编程

主 Flash 一次可以编程 16 位(半字)和 8 位(字节)。解锁 Flash 后,当 FLASH\_CR 寄存器中的 PG 位为 1 时,则向指定的地址写入半字的数据,即完成一次 Flash 编程操作。

#### 注意:

若 Flash 处于解锁状态,FLASH\_CR 寄存器中的 PG 位为 1 时,写入的数据长度不是半字,会引起硬件错误中断。

主 Flash 编程的流程如下图所示:

图 3-2 对 Flash 的编程

当待编程地址所对应的 FLASH\_WRPR 寄存器的写保护位生效时,不允许编程操作,否则会产生编程错误告警。编程操作结束后,FLASH SR 寄存器的 EOP 位会提示该操作是否成功。

主 Flash 存储器的标准编程流程如下:

- 1. 检查 FLASH\_SR 中的 BSY 位,以确认上次操作已经结束。

- 2. 将 FLASH\_CR 寄存器中的 PG 位置为 1,以写入 Flash。

- 3. 根据配置,以半字为单位向目标地址写入数据。

- 4. 在完成 Flash 的数据写入后,将 FLASH\_CR 寄存器中的 PG 位置为 0。

- 5. 等待 FLASH\_SR 寄存器中的 BSY 变为 0。

- 6. 检查 FLASH\_SR 寄存器的 EOP 标志位(如果 Flash 编程成功会置位 EOP),然后软件清除该标志位。

## 3.2.6 Flash 中断

表 3-4 Flash 中断事件和事件标志

| 中断事件  | 事件标志     | 使能控制位 |

|-------|----------|-------|

| 操作结束  | EOP      | EOPIE |

| 写保护错误 | WRPRTERR | ERRIE |

# 3.3 Flash 选项字节

Flash 选项字节域共有 24 个字节,根据用户的应用需求进行配置。

一个 32 位选项字可划分成如下表所示的选项字节:

表 3-5 选项字划分成选项字节

| [31:24]   | [23:16] | [15:8]    | [7:0]  |

|-----------|---------|-----------|--------|

| 选项字节1按位取反 | 选项字节1   | 选项字节0按位取反 | 选项字节 0 |

选项字若有内容更新,需复位系统才能生效。前面 4 个选项字是以按位取反之后和选项字节组合的 形式存储,如下表所示。

表 3-6 选项字节结构

| 地址          | [31:24]            | [23:16] | [15:8]           |           | [7:0]  |  |       |

|-------------|--------------------|---------|------------------|-----------|--------|--|-------|

| 0X1FFF F800 | nUSER              | USER    | nRDP             |           | RDP    |  |       |

| 0X1FFF F804 | nDATA1             | DATA1   | nDATA0           |           | nDATA0 |  | DATA0 |

| 0X1FFF F808 | nWRP1              | WRP1    | nWRP0            |           | WRP0   |  |       |

| 0X1FFF F80C | nWRP3              | WRP3    | nWRP2            |           | WRP2   |  |       |

| 0X1FFF F810 | IWDG_INI_KEY[15:0] | 保留      | IWDG_RL_         | _IV[11:0] |        |  |       |

| OX1FFF F814 | DBG_CLK_CTL[15:0]  |         | LSI_LP_CTL[15:0] |           |        |  |       |

表 3-7 选项字节描述

| 0x1FFF F800 31:24 nUSER: USER 按位取反 |  |

|------------------------------------|--|

| MOSER, OSER JA E-KA                |  |

| USER: 用户选项字节                       |  |

| 地址          | 位域    | 选项字节描述                                                                                                                                                                                                                                                                                            |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |       | <ul> <li>○ 0: 当进入待机模式产生复位</li> <li>○ 1: 不产生复位</li> <li>● 位 17: nRST_STOP</li> <li>○ 0: 当进入停机模式产生复位</li> <li>○ 1: 不产生复位</li> <li>● 位 16: WDG_SW</li> <li>○ 0: 硬件看门狗</li> <li>○ 1: 软件看门狗</li> <li>○ 1: 软件看门狗</li> <li>○ 1: 软件看门狗</li> <li>● 当进入停机模式时,产生复位事件。</li> <li>● 当进入停机模式时,产生复位事件。</li> </ul> |

|             | 15:8  | nRDP: RDP 按位取反                                                                                                                                                                                                                                                                                    |

|             | 7:0   | RDP: Flash 读保护选项字节<br>该字节的值定义了 Flash 读保护级别。<br>● 0xAA: 级别 0<br>● 0xXX(除 0xAA 和 0xCC 取值外): 级别 1<br>● 0xCC: 级别 2                                                                                                                                                                                    |

| 0x1FFF F804 | 31:0  | DATAx: 用户数据                                                                                                                                                                                                                                                                                       |

| 0x1FFF F808 | 31:0  | WRPx: Flash 写保护选项字节                                                                                                                                                                                                                                                                               |

| 0x1FFF F80C | 31:0  | WRPx: Flash 写保护选项字节  ● 位[31:24]: nWRP3  ● 位[23:16]: WRP3(存于 FLASH_WRPR[31:24])  ● 位[15:8]: nWRP2  ● 位[7:0]: WRP2(存于 FLASH_WRPR[23:16])  ○ 0: 写保护使能  ○ 1: 写保护禁能  Flash的写保护范围是按照每一位(Bit)对应 4 页(Page)进行控制。WRP2 作用于64~95 页。WRP3 作用于96~127 页。                                                          |

| 0x1FFF F810 | 31:16 | IWDG_INI_KEY: 决定IWDG_RL_IV是否生效。<br>当IWDG_INI_KEY[31:16]为0x5b1e时,IWDG_RL_IV配置有效,否则无效。                                                                                                                                                                                                              |

|             | 15:12 | 保留值                                                                                                                                                                                                                                                                                               |

| 地址          | 位域    | 选项字节描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 11:0  | IWDG_RL_IV[11:0]: IWDG 重载值。 当IWDG_INI_KEY[15:0]为0x5b1e时,IWDG_RL_IV配置有效,否则无效。 IWDG 重载值计算公式参见"16 独立看门狗(IWDG)"。 需要注意的是: 1、使用该功能,必须程序中要对 IWDG 喂狗; 2、如果没有对 IWDG 喂狗,且该值设置太小,IWDG 复位间隔时间短,可能会导致芯片无法正常烧录。                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x1FFF F814 | 31:16 | DBG_CLK_CTL: 关闭或打开 CPU 内部 Debug 时钟。<br>当存储的值为0x12de时,关闭CPU内部Debug时钟,SWD 将不能访问 MCU;<br>否则保持调试时钟为打开状态。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | 15:0  | LSI_LP_CTL: 决定 MCU 在使能 IWDG 后再进入停机模式时,是否需要被 IWDG 或 AWUT 周期唤醒;以及 MCU 在进入待机模式时,是否需要被 SAWUT 定时器周期唤醒;      该位域配置为 0x369C 时:     MCU 进入停机(Stop)模式后,可根据 LSION 的设置关闭 LSI。若 LSION 为开启状态,则:         o 在 Stop 模式时:         MCU 被 AWUT 或 IWDG 周期唤醒,否则不能被唤醒。         o Standby 模式时:         MCU 被 STBAWU 周期唤醒,否则不能被唤醒。 在 MCU 被唤醒后,LSI 恢复为进入停机模式之前的状态。          卷 若未配置该位域:         o 在 Stop 模式时:         在使能 IWDG 后再进入停机模式,则 MCU 被 IWDG 周期唤醒,否则不能被唤醒。         o Standby 模式时:         在使能 IWDG 后再进入停机模式,则 MCU 被 IWDG 周期唤醒,否则不能被唤醒。         o Standby 模式时:         在配置 STBAWU 后再进入待机模式,MCU 会被 STBAWU 周期唤醒。 |

每次系统复位后,信息块数据被读取和存储到相应的选项字节寄存器(FLASH\_OBR)和 Flash 保护寄存器(FLASH\_WRPR)中。

每个选项字节都有其值按位取反之后的值存放在信息块中,其目的用于校验选项字节的正确性。当选项字节装载后,CPU 会检查选项字节的正确性。若选项字节与其按位取反之后的值比较不一致时,会产生选项字节校验错(OPTERR)信息。当产生 OPTERR 后,CPU 会强制将相应的选项字节值变为 0xFF。当选项字节与其按位取反之后的值都为 0xFF 时,CPU 不会比较其与按位取反之后的值的差异。

### 注意:

选项字节的擦除和编程操作在整个产品工作电压范围内都可以完成。

### 3.3.1 选项字节擦除

选项字节擦除操作涉及以下寄存器的配置:

- Flash 关键字寄存器(FLASH\_OPTKEYR)

- Flash 状态寄存器(FLASH\_SR)

- Flash 控制寄存器(FLASH CR)

- Flash 地址寄存器(FLASH\_AR)

擦除选项字节前的准备:

需要先对 FLASH\_KEYR 和 FLASH\_OPTKEYR 写入关键字 KEY 以解锁 Flash,然后进行选项字节擦除操作。

选项字节是按字节擦除的,将目标地址擦除之后的值为趋近于0的随机值,步骤如下:

- 1. 检查 FLASH SR 寄存器中的 BSY 位,以确保上次操作结束。

- 2. 将 FLASH\_CR 寄存器中的 OPTWRE 位置 1,以允许改写选项字节。

- 3. 置 FLASH CR 寄存器中的 OPTER 位为 1,以选择按字节擦除。

- 4. 将待擦除的地址写入 FLASH\_AR 寄存器,待擦除的地址必须在里已有的地址,否则可能会出现不可预计的错误。

- 5. 将 FLASH CR 寄存器中的 STRT 位置为 1,以启动擦除操作。

- 6. 等待 FLASH\_SR 中的 BSY 位变成 0,表明擦除操作结束。

- 7. 将 FLASH CR 寄存器中的 OPTER 位置为 0,以恢复默认值。

### 3.3.2 选项字节编程

选项字节区按照半字为单位进行编程。该区大小总共12个半字,包括:

- 1 个读保护

- 2个用户数据

- 1 个硬件配置

- 4 个写保护

- 2 个 IWDG 配置

- 2个调试时钟控制

选项字节编程前的准备:

需要先对 FLASH\_KEYR 和 FLASH\_OPTKEYR 写入关键字 KEY 以解锁 Flash,然后进行选项字节编程操作。LSB 值会自动转化为 MSB,以适应选项字节的位定义。

选项字节编程的步骤如下:

- 1. 检查 FLASH SR 寄存器中的 BSY 位,以确保上次操作结束。

- 2. 将 FLASH CR 寄存器中的 OPTWRE 位置 1,以使能选项字节编程。

- 3. 将 FLASH CR 寄存器中的 OPTPG 位置为 1,以选择半字方式写入。

- 4. 写数据(半字)到目标地址。

- 5. 等待 FLASH SR 中的 BSY 位为 0,表示编程操作结束。

- 6. 将 FLASH CR 寄存器中的 OPTPG 位置为 0,以恢复默认值。

当读保护选项字节由保护状态变成非保护状态时,会执行一次整片擦除,然后才允许改写读保护位数据。若用户仅想改写选项字节区以外的数据,则不会引起整片擦除,该机制用于保护 Flash 的内容。

#### 3.4 EEPROM

EEPROM 共有 448 个字节可用, 其地址范围是 0x0C00 0000~0x0C00 01BF。

EEPROM 的擦除和编程操作在整个产品工作电压范围内都可以完成。

### 3.4.1 EEPROM 的擦除

该操作涉及以下 5 个寄存器的配置:

- Flash 关键字寄存器(FLASH KEYR)

- Flash 状态寄存器(FLASH SR)

- Flash 控制寄存器(FLASH\_CR)

- Flash 地址寄存器(FLASH\_AR)

- Flash EEPROM 控制寄存器(FLASH ECR)

EEPROM 擦除前的准备:

需要先对 FLASH\_KEYR 写入关键字 KEY 以解锁 Flash,然后进行 EEPROM 擦除操作。

EEPROM 是按字节擦除的,将目标地址擦除之后的值为趋近于 0 的随机值,步骤如下:

- 1. 检查 FLASH SR 寄存器中的 BSY 位,以确保上次操作结束。

- 2. 将 FLASH ECR 寄存器中的 EEPROM ER 位置 1,准备按字节擦除 EEPROM 空间。

- 3. 将待擦除的 EEPROM 的地址写入 FLASH\_AR 寄存器。

- 4. 将 FLASH\_CR 寄存器中的 STRT 位置为 1,以启动擦除操作。

- 5. 等待 FLASH\_SR 中的 BSY 位变成 0,表明擦除操作结束。

- 6. 将 FLASH\_ECR 寄存器中的 EEPROM\_ER 位置为 0,以恢复默认值。

### 3.4.2 EEPROM 的编程

EEPROM 编程前的准备:

需要先对 FLASH\_KEYR 写入关键字 KEY 以解锁 Flash,然后进行 EEPROM 编程操作。 EEPROM 编程的步骤如下:

- 1. 检查 FLASH\_SR 寄存器中的 BSY 位,以确保上次操作结束。

- 2. 将 FLASH ECR 寄存器中的 EEPROM BPG 位置 1,准备按字节编程 EEPROM 空间。

- 3. 写数据(字节)到目标地址。

- 4. 等待 FLASH SR 中的 BSY 位为 0,表示编程操作结束。

- 5. 将 FLASH\_ECR 寄存器中的 EEPROM\_BPG 位置为 0,以恢复默认值。

### 3.5 Flash 寄存器

基地址: 0x4002 2000

空间大小: 0x400

# 3.5.1 Flash 访问控制寄存器(FLASH\_ACR)

地址偏移: 0x00

复位值: 0x0000 0000

| 31  | 30   | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|-----|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Res |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|     | inco |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4        | 3   | 2 | 1 | 0 |

|-----|----|----|----|----|----|---|---|---|---|----|----------|-----|---|---|---|

| Res |    |    |    |    |    |   |   |   |   | LA | TENCY[2: | :0] |   |   |   |

|     |    |    |    |    |    |   |   |   |   |    | rw       |     |   |   |   |

| 本位<br>• 当<br>• ()<br>• ()<br>• ()<br>• ()<br>• ()<br>• ()<br>• ()<br>• ()<br>• ()<br>• 10<br>• 11<br>• 11<br>• 11<br>· 五片 | MCY[2:0]: 等待周期  预设 HCLK 周期和 Flash 访问时间的比率关系。  1.8V ≤ VCC ≤ 2.4V 时:  2000: 0 时钟等待周期(适用于 HCLK ≤ 16 MHz)  2001: 1 个时钟等待周期(适用于 16 MHz < HCLK ≤ 32 MHz)  2010: 2 个时钟等待周期(适用于 32 MHz < HCLK ≤ 48 MHz)  2.4V < VCC ≤ 3.6V 时:  2.000: 0 等待周期(适用于 HCLK ≤ 24 MHz)  2.010: 1 个时钟等待周期(适用于 24 MHz < HCLK ≤ 48 MHz)  2.010: 保留  1: 3 个时钟等待周期  2: 7 个时钟等待周期  1: 9 个时钟等待周期  1: 9 个时钟等待周期  1: 39 个时钟等待周期  2: 19 个时钟等待周期  2: 39 个时钟等待周期  2: 30 个时钟等待周期  2: 30 个时钟等待周期 |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# 3.5.2 Flash 关键字寄存器(FLASH\_KEYR)

地址偏移: 0x04

复位值: 0xXXXX XXXX

说明: X 表示不定值。

该寄存器仅支持写。若读该寄存器,返回值为0。

| 31 | 30           | 29 | 28  | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 |   | 18 | 17 | 16 |

|----|--------------|----|-----|----|----|----|----|----|----|----|----|----|---|----|----|----|

|    | FKEYR[31:16] |    |     |    |    |    |    |    |    |    |    |    |   |    |    |    |

|    | W            |    |     |    |    |    |    |    |    |    |    |    |   |    |    |    |

|    |              |    |     |    |    |    |    |    |    |    |    |    |   |    |    |    |

| 15 | 14           | 13 | 3 ( | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3 | 2  | 1  | 0  |

|    | FKEYR[15:0]  |    |     |    |    |    |    |    |    |    |    |    |   |    |    |    |

|    | W            |    |     |    |    |    |    |    |    |    |    |    |   |    |    |    |

|    |              | 1  |     |    |    |    |    |    |    |    |    |    |   |    |    |    |

位 31:0 FKEYR: Flash 关键字 该位域用于存储可解锁 Flash 的关键字。 • KEY1: 0x45670123 • KEY2: 0xCDEF89AB

说明: w 表示仅可写。

# 3.5.3 Flash 选项关键字寄存器(FLASH\_OPTKEYR)

偏移地址: 0x08

复位值: 0xXXXX XXXX

说明: X 表示不定值。

该寄存器仅支持写。若读该寄存器,返回值为0。

| 31            | 30             | 29 | 28 | 27 | 26 | 25 | 24    | 23      | 22 | 21 | 20 | ) | 19 | 18 | 17 | 16 |

|---------------|----------------|----|----|----|----|----|-------|---------|----|----|----|---|----|----|----|----|

|               | OPTKEYR[31:16] |    |    |    |    |    |       |         |    |    |    |   |    |    |    |    |

|               | W              |    |    |    |    |    |       |         |    |    |    |   |    |    |    |    |

|               |                |    |    |    |    |    |       |         |    |    |    |   |    |    |    |    |

| 15            | 14             | 13 | 1  | .2 | 11 | 10 | 9     | 8       | 7  | 6  | 5  | 4 | 3  | 2  | 1  | 0  |

| OPTKEYR[15:0] |                |    |    |    |    |    |       |         |    |    |    |   |    |    |    |    |

|               |                |    |    |    |    |    | OPTRE | 0.61371 |    |    |    |   |    |    |    |    |

位 31:0 OPTKEYR: 选项字节关键字

该位域用于存储解锁 OPTWRE 的关键字。

KEY1: 0x4567 0123KEY2: 0xCDEF 89AB

## 3.5.4 Flash 状态寄存器(FLASH\_SR)

偏移地址: 0x0C

复位值: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | Re | es |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5        | 4  | 3   | 2 | 1   | 0 |

|----|-----|----|----|----|----|---|---|---|-----|----------|----|-----|---|-----|---|

|    | Res |    |    |    |    |   |   |   | EOP | WRPRTERR |    | Res |   | BSY |   |

|    |     |    |    |    |    |   |   |   |     | rw       | rw |     |   |     | r |

| 位 31:6 | Res: 保留<br>必须保持复位值。                                                            |

|--------|--------------------------------------------------------------------------------|

| 位 5    | EOP:操作结束<br>当 Flash 操作(写/擦除)完成时,由硬件置位。该位由软件写 1 清零。<br>注意:写或擦除操作成功后,硬件才会置位 EOP。 |

| 位 4    | WRPRTERR:写保护错误标志<br>当出现对写保护区域的写操作时,该位被硬件置位。该位由软件写 1 清零。                        |

| 位 3:1  | Res: 保留<br>必须保持复位值。                                                            |

| 位 0    | BSY: 忙标志                                                                       |

该位标明 Flash 操作正在进行。当开始 Flash 操作时,该位被硬件置为"1"。当操作结束时或发生错误时,该位由硬件清零。

说明: r表示仅读。

# 3.5.5 Flash 控制寄存器(FLASH\_CR)

偏移地址: 0x10

复位值: 0x0000 0080

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | Re | es |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14  | 13 | 12    | 11  | 10    | 9      | 8   | 7    | 6    | 5     | 4     | 3   | 2   | 1   | 0  |

|----|-----|----|-------|-----|-------|--------|-----|------|------|-------|-------|-----|-----|-----|----|

|    | Res |    | EOPIE | Res | ERRIE | OPTWRE | Res | LOCK | STRT | OPTER | OPTPG | Res | MER | PER | PG |

|    |     |    | rw    |     | rw    | rw     |     | rw   | rw   | rw    | rw    |     | rw  | rw  | rw |

| 位 31:13 | Res: 保留                                                                    |

|---------|----------------------------------------------------------------------------|

|         | 必须保持复位值。                                                                   |

| 位 12    | EOPIE: 操作结束中断使能 该位可使 FLASH_SR 中的 EOP 位变为 1 时,产生中断请求。  • 0: 中断禁用  • 1: 中断使能 |

| 位. 11   | р /II (д)                                                                  |

| 14. 11  | Res: 保留 必须保持复位值。                                                           |

| 位 10    | ERRIE: 操作错误中断使能                                                            |

|         | 该位使 FLASH_SR 中的 WRPRTERR 位变为 1 时,产生中断请求。                                   |

|         | ● 0: 中断禁用                                                                  |

|         | ● 1: 中断使能                                                                  |

| 位 9     | OPTWRE:选项字节写使能                                                             |

| ,— -    | 该位为 1 时,允许改写选项字节。FLASH_OPTKEYR 寄存器写入正确的关键字序列,该位被置 1。                       |

|         | 该位可由软件清零。                                                                  |

|         | <b>这世界田林自由李。</b>                                                           |

| 位 8     | Res: 保留                                                                    |

|         | 必须保持复位值。                                                                   |

| 位 7     | LOCK: 锁定 Flash 标志                                                          |

|         | 当该位为 1时,表明 Flash 为锁定状态。通过解锁时序将该位清零。当解锁不成功时,该位就一直为1了,除非下次复位重新操作。            |

|         | 注意:该位只能写1。                                                                 |

|         |                                                                            |

| 位 6 | STRT: 启动<br>该位会触发一个擦除操作,仅由软件置 1,仅在 BSY 为 0 时被清零。 |

|-----|--------------------------------------------------|

| 位 5 | OPTER: 选项字节擦除<br>只能按字节擦除。                        |

| 位 4 | OPTPG: 选项字节写入<br>只能按半字的方式写入。                     |

| 位 3 | Res: 保留<br>必须保持复位值。                              |

| 位 2 | MER: 整片擦除整片擦除时选择。                                |

| 位 1 | PER: 页擦除<br>页擦除时选择。                              |

| 位 0 | PG: 半字写入<br>Flash 写入时可配置该位。                      |

# 3.5.6 Flash 地址寄存器(FLASH\_AR)

偏移地址: 0x14

复位值: 0x0000 0000

该寄存器通过硬件根据当前和上一次操作进行更新。对于页擦除操作,该寄存器该由软件来更新以便瞄准要擦除的页。

| 31 | 30                                 | 29 | 28  | 27 | 26 | 25 | 24     | 23     | 22 | 21 | 20 | 19  | 18 | 17 | 16 |

|----|------------------------------------|----|-----|----|----|----|--------|--------|----|----|----|-----|----|----|----|

|    |                                    |    |     |    |    |    | FAR [3 | 31:16] |    |    |    |     |    |    |    |

|    | w                                  |    |     |    |    |    |        |        |    |    |    |     |    |    |    |

|    | 15 14 12 11 10 0 9 7 6 5 4 2 2 1 0 |    |     |    |    |    |        |        |    |    |    |     |    |    |    |

| 15 | 14                                 | 13 | 3 : | 12 | 11 | 10 | 9      | 8      | /  | 6  | 5  | 4 3 | 2  | 1  | 0  |

|    |                                    |    |     |    |    |    | FAR[   | 15:0]  |    |    |    |     |    |    |    |

|    | W                                  |    |     |    |    |    |        |        |    |    |    |     |    |    |    |

| 位 31:0 | FAR: Flash 地址                                   |

|--------|-------------------------------------------------|

|        | 当 PG 位使能时,该位域为写入 Flash 的地址;或当 PER 位使能时,选择待擦除的页。 |

|        | 注意:当FLASH_SR 中的BSY 为1 时,禁止写该寄存器。                |

## 3.5.7 Flash 选项字节寄存器(FLASH\_OBR)

偏移地址: 0x1C

复位值: 0xXXXX XX0X

选项字节的写入值决定了该寄存器的复位值;复位时,选项字节加载环节中比较选项字节及其反码(按

位取反)的结果决定了 OPTERR 位的复位值。

| 31    | 31   30   29   28   27   26   25   24 |  |  |  |  |  |  |  | 22 | 21 | 20 | 19  | 18 | 17 | 16 |

|-------|---------------------------------------|--|--|--|--|--|--|--|----|----|----|-----|----|----|----|

| DATA1 |                                       |  |  |  |  |  |  |  |    |    | DA | ГАО |    |    |    |

| r     |                                       |  |  |  |  |  |  |  |    |    | ı  | r   |    |    |    |

| 15 | 14 | 13  | 12 | 11 | 10               | 9         | 8      | 7 | 6 | 5   | 4 | 3 | 2    | 1      | 0      |

|----|----|-----|----|----|------------------|-----------|--------|---|---|-----|---|---|------|--------|--------|

|    |    | Res |    |    | nRST_ST<br>ANDBY | nRST_STOP | WDG_SW |   |   | Res |   |   | RDPR | T[1:0] | OPTERR |

|    |    |     |    |    | r                | r         | r      |   |   |     |   |   |      | r      | r      |

| 位 31:24 | DATA1: 用户数据                                                                                     |

|---------|-------------------------------------------------------------------------------------------------|

| 位 23:16 | DATAO: 用户数据                                                                                     |

| 位 15:11 | Res: 用户选项字节的保留位                                                                                 |

| 位 10    | nRST_STANDBY: 进入待机模式是否产生复位。<br>该位属于用户选项字节。 • 0: 当进入待机模式产生复位。 • 1: 不产生复位。                        |

| 位 9     | nRST_STOP: 进入停机模式是否产生复位。<br>该位属于用户选项字节。  • 0: 当进入停机模式产生复位。  • 1: 不产生复位。                         |

| 位 8     | WDG_SW:选择软件或硬件看门狗 该位属于用户选项字节。  • 0:硬件看门狗  • 1:软件看门狗                                             |

| 位 7:3   | Res: 保留<br>必须保持复位值。                                                                             |

| 位 2:1   | RDPRT[1:0]: 读保护状态  • 00: 当前处于 Level0 读保护状态。  • 01: 当前处于 Level1 读保护状态。  • 11: 当前处于 Level2 读保护状态。 |

| 位 0     | OPTERR: 选项字节错误<br>当该位置 1 时,表明加载选项字节互补关系不成立。                                                     |

# 3.5.8 Flash 写保护寄存器(FLASH\_WRPR)

偏移地址: 0x20 复位值: 0xXXXX XXXX

选项字节的写入值决定了该寄存器的复位值。

| 31  | 30  | 29   | 28 | 27 | 26 | 25 | 24   | 23     | 22 | 21 | 20  | 19  | 18 | 17 | 16  |

|-----|-----|------|----|----|----|----|------|--------|----|----|-----|-----|----|----|-----|

|     |     |      |    |    |    |    | WRP[ | 31:16] |    |    |     |     |    |    |     |

|     |     |      |    |    |    |    | I    | r      |    |    |     |     |    |    |     |

| 1.5 | 1.4 | 1 12 |    | 2  | 11 | 10 | q    | 0      | 7  | 6  | - 1 | 4 2 | 2  | 1  | 1 0 |

| 15  | 14  | 13   | 1  | .2 | 11 | 10 | ,    | 0      | /  | 6  | 5 4 | 4 3 |    | 1  | U   |

|     |     |      |    |    |    |    | WRP  | [15:0] |    |    |     |     |    |    |     |

|     |     |      |    |    |    |    | 1    | r      |    |    |     |     |    |    |     |

位 31:0 WRP[31:0]: 写保护

该寄存器包含保持由复位后载入的写保护选项字节。

# 3.5.9 Flash 控制寄存器 2(FLASH\_ECR)

偏移地址: 0x70

复位值: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | Re | es |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14 | 13 | 12 | 11 | 10  | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2          | 1         | 0   |

|----|----|----|----|----|-----|---|---|---|---|---|---|---|------------|-----------|-----|

|    |    |    |    |    | Res |   |   |   |   |   |   |   | EEPROM_BPG | EEPROM_ER | BPG |

|    |    |    |    |    |     |   |   |   |   |   |   |   | rw         | rw        | rw  |

| 位 31:3 | Res: 保留<br>必须保持复位值。       |

|--------|---------------------------|

| 位 2    | EEPROM_BPG:字节编程 EEPROM 空间 |

| 位 1    | EEPROM_ER: 字节擦除 EEPROM 空间 |

| 位 0    | BPG: 字节编程 Flash 空间        |

# 3.5.10 中断向量表偏移寄存器(INT\_VEC\_OFFSET)

偏移地址: 0x74

复位值: 0x0000 0004

| 31     | 30 | 29 | 28          | 27 | 26 | 25              | 24 | 23      | 22      | 21     | 20 | 19   | 18  | 17           | 16 |

|--------|----|----|-------------|----|----|-----------------|----|---------|---------|--------|----|------|-----|--------------|----|

|        |    |    |             |    |    |                 | R  | es      |         |        |    |      |     |              |    |

|        |    |    |             |    |    |                 |    |         |         |        |    |      |     |              |    |

| 15     | 14 | 1  | 3           | 12 | 11 | 10              | 9  | 8       | 7       | 6      | 5  | 4 3  | 2   | 1            | 0  |

| R      | es |    | •           |    | •  |                 | IN | IT_VEC_ | OFFSET[ | [13:0] |    | •    | •   |              |    |

|        |    |    | rw          |    |    |                 |    |         |         |        |    |      |     |              |    |

| 位 31:  | 14 |    | s:保旨<br>须保持 | •  | 直。 |                 |    |         |         |        |    |      |     |              |    |

| 位 13:0 | 0  |    |             |    |    | : 中断<br>T[13:0] |    |         |         |        | 可设 | 置的最高 | 小偏移 | <i>量为</i> 4。 |    |

若 INT\_VEC\_OFFSET 设置为 Y\_Addr,则:

- 中断向量表重映射后,CPU 访问 0x0800 0000~0x0800 00FF 这一段地址时,实际访问到的地址是:(Y Addr + 0x0800 0000)~(Y Addr + 0x0800 00FF);

- 当 INT\_VEC\_OFFSET 的值大于或等于 0x100 时,原本物理地址 0x0800 0000 到 0x0800 00FF 中的值将不能被访问到。

注意:若开发一个带 Bootloader 和应用程序(APP)的项目,需要在 APP 工程内调用 Boot 工程中的函数 fun y,那么函数 fun y 必须定义在地址 0x0800 00FF 以后。

下图说明了中断向量表地址映射及偏移的关系:

图 3-3 中断向量表地址映射及偏移

**CPU 访问 Flash 的地址映射规则**:规定了 CPU 每次启动,将访问 0x0000 0000 地址,通过地址映射,实则访问 Flash 地址 0x8000 0000。

**INT\_VEC\_OFFSET = 0x1000**: Cortex-M0 内核把中断向量表固定到了 0x0000 0000 地址,设置中断向量表偏移量后,CPU 到 0x0000 0000 地址取中断向量表入口地址时,实际取到的地址是: (**0x1000+ 0x0000 0000**)。由于默认有地址重映射的,所以取到地址的是(**0x1000+ 0x0800 0000**)。如此,则不需要通过操作 SYSCFG\_CFG1 寄存器中的 MEM\_MODE 位来重映射中断向量表了。这在 IAP 升级应用中很方便。

## 4 CRC 计算单元 (CRC)

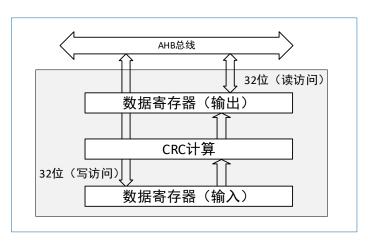

循环冗余校验(CRC)计算单元用于验证数据传输和数据存储的完整性。CRC 计算单元在运行期间 计算出软件的签名,并将其和链接时所产生并存储于在指定存储地址的参考签名进行比较。

### 4.1 CRC 主要功能

- 采用的 CRC-32(与以太网标准相同)多项式 0x4C11DB7

X<sup>32</sup> + X<sup>26</sup> + X<sup>23</sup> + X<sup>22</sup> + X<sup>16</sup> + X<sup>12</sup> + X<sup>11</sup> + X<sup>10</sup> + X<sup>8</sup> + X<sup>7</sup> + X<sup>5</sup> + X<sup>4</sup> + X<sup>2</sup> + X + 1

- 能处理 8 位、16 位和 32 位数据宽度

- 可编程 CRC 初始值

- 单输入/输出 32 位数据寄存器

- 输入缓冲器可避免计算期间发生总线阻塞

- 8位通用寄存器(可用于临时存储)

- I/O 数据的可反转性选项 CRC 功能说明

- 对于 32 位数据大小, CRC 计算在 4 个 AHB 时钟周期(HCLK)内完成。

图 4-1 CRC 计算单元框图

## 4.2 CRC 功能描述

CRC 计算单元具有单个 32 位读/写数据寄存器(CRC\_DR)。CRC\_DR 用于保存输入的新数据(写访问)和之前 CRC 计算的结果(读访问)。

对 CRC\_DR 寄存器的每次写操作都会对之前的 CRC 值(存于 CRC\_DR 中)和新值做一次 CRC 计算。 CRC 计算支持整个 32 位数据字或逐个字节计算,具体取决于写入数据的位宽。

CRC\_DR 寄存器可按字、右对齐半字和右对齐字节进行访问。对于其它 CRC 寄存器,只支持 32 位访问。

计算时间取决于数据宽度:

- 32 位数据需要 4 个 AHB 时钟周期

- 16 位数据需要 2 个 AHB 时钟周期

- 8 位数据需要 1 个 AHB 时钟周期

输入缓冲器中可立即写入第二个数据,无需因之前的 CRC 计算而等待。

CRC 计算单元可动态调整数据大小,从而能最大程度地减少给定字节数的写访问次数。例如,对 5个字节进行 CRC 计算时,可先写入一个字,然后写入一个字节。

输入数据的顺序可反转,以管理各种数据存放方式(双字/单字/字节、大端/小端等)。可对 8 位、16 位和 32 位数据执行反转操作,具体取决于 CRC CR 寄存器中的 REV IN[1:0]位。

例如,输入数据 0x1A2B3C4D 在 CRC 计算中用作:

- 按字节执行位反转后的 0x58D43CB2

- 按半字执行位反转后的 0xD458B23C

- 按全字执行位反转后的 0xB23CD458

通过将 CRC\_CR 寄存器中 REV\_OUT 位置 1,也可以将输出数据反转。该操作按位进行,例如:输出数据 0x1122 3344 将转换为 0x22CC 4488。

配置 CRC CR 寄存器中的 RESET 控制位可将 CRC 计算器初始化为可编程值 (默认值为 OxFFFF FFFF)。

可使用 CRC\_INIT 寄存器对 CRC 初始值进行编程。对 CRC\_INIT 寄存器进行写访问时,会自动初始化 CRC DR 寄存器。

CRC\_IDR 寄存器可用于保存与 CRC 计算相关的临时值。CRC\_IDR 不受 CRC\_CR 寄存器中的 RESET 位影响。

### 4.3 CRC 寄存器

基地址: 0x4002 3000

空间大小: 0x400

## 4.3.1 数据寄存器(CRC\_DR)

偏移地址: 0x00 复位值: 0xFFFF FFFF

| 31 | 30   | 29   | 28 | 27       | 26 | 25 | 24   | 23    | 22         | 21 | 20  | 19 | 18  | 17 | 16 |

|----|------|------|----|----------|----|----|------|-------|------------|----|-----|----|-----|----|----|

|    |      |      |    |          |    |    | DR[3 | 1:16] |            |    |     |    |     |    |    |

|    |      |      |    |          |    |    | r    | w     |            |    |     |    |     |    |    |

| 45 | 1 44 | 1 40 |    |          | 44 | 40 | _    | 0     | <b>-</b> 1 | -  | - 1 |    |     |    |    |

| 15 | 14   | 13   | 12 | <u>'</u> | 11 | 10 | 9    | 8     | /          | 6  | 5   | 4  | 3 2 | 1  | U  |

|    |      |      |    |          |    |    | DR[1 | L5:0] |            |    |     |    |     |    |    |

|    |      |      |    |          |    |    |      |       |            |    |     |    |     |    |    |

位 31:0

DR[31:0]: 数据寄存器

该寄存器用于存放待计算的新数据,直接将其写入即可。读取该寄存器得到的是上次 CRC 计算的结果。如果读出或写入的数据不足 32 位,则表示该数据仅针对有意义的位。

## 4.3.2 独立数据寄存器(CRC\_IDR)

偏移地址: 0x04

复位值: 0x0000 0000

| 31 | 30 | 29 | 28 | 27  | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19       | 18 | 17 | 16 |

|----|----|----|----|-----|----|----|----|----|----|----|----|----------|----|----|----|

|    |    |    |    |     |    |    | Re | es |    |    |    |          |    |    |    |

|    |    |    |    |     |    |    |    |    |    |    |    |          |    |    |    |

|    |    |    |    |     |    |    | 1  | -  |    |    |    |          |    |    |    |

| 15 | 14 | 13 | 3  | 12  | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4 3      | 2  | 1  | 0  |

|    |    |    |    | Res |    |    |    |    |    |    |    | IDR[7:0] |    |    |    |

|    |    |    |    |     |    |    |    |    |    |    |    | rw       |    |    |    |

位 31:8

Res: 保留

|       | 必须保持复位值。                                                                        |

|-------|---------------------------------------------------------------------------------|

| 位 7:0 | IDR[7:0]: 通用目的 8 位数据寄存器 该寄存器可用作 1 个字节的临时存储。CRC_CR 寄存器中的 RESET 位引起的复位操作不会影响该寄存器。 |

# 4.3.3 控制寄存器(CRC\_CR)

偏移地址: 0x08

复位值: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | Re | es |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8       | 7     | 6      | 5 | 4 | 3  | 2 | 1     | 0  |

|----|-----|----|----|----|----|---|---------|-------|--------|---|---|----|---|-------|----|

|    | Res |    |    |    |    |   | REV_OUT | REV_I | N[1:0] |   | R | es |   | RESET |    |

|    |     |    |    |    |    |   |         | rw    | r      | w |   |    |   |       | rs |

| 位 31:8     | Res: 保留<br>必须保持复位值。                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------|

| 位 7        | REV_OUT: 翻转输出数据<br>该位控制输出数据的翻转。 • 0: 不翻转 • 1: 翻转                                                              |

| 位 6:5      | REV_IN[1:0]: 翻转输入数据<br>该位域控制输入数据的翻转。                                                                          |

| 位 4:1      | Res: 保留<br>必须保持复位值。                                                                                           |

| 位 <b>0</b> | RESET: 复位控制 该位用于复位整个CRC计算单元,并将CRC_INIT寄存器中的值更新到 CRC_DR 寄存器。该位由软件置位,由硬件清零。 说明: rs 所表示的含义,参见 "24.1 寄存器描述中的缩略语"。 |

# 4.3.4 CRC 初值寄存器(CRC\_INIT)

偏移地址: 0x10 复位值: 0xFFFF FFFF

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24      | 23       | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|---------|----------|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | CRC_INI | T[31:16] |    |    |    |    |    |    |    |

|    |    |    |    |    |    | ı      | w        |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|--------|----------|---|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9      | 8        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|    |    |    |    |    |    | CRC_IN | NIT[15:0 | ] |   |   |   |   |   |   |   |

|    |    |    |    |    |    | ı      | Ŵ        |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |        |          |   |   |   |   |   |   |   |   |

位 31:0 CRC\_INIT[31:0]: CRC 预置的初值 该寄存器用于设置CRC 的初值。

## 5 电源控制(PWR)

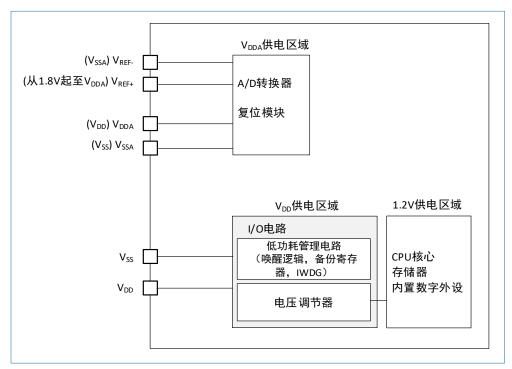

### 5.1 电源

该系列芯片的工作电压(V<sub>DD</sub>)为 1.8~3.6 V。通过内置的电压调节器提供所需的 1.2 V 内核电源。该系列芯片片内数字逻辑的电源由片内 LDO 提供。

片内 LDO 的输出电压可通过寄存器设置,以便于软件根据应用场景最大程度地优化芯片的电流功耗。芯片运行(Run)模式和停机(Stop)模式的 LDO 输出电压可以分别独立设置。

图 5-1 电源框图

注意: V<sub>DDA</sub> 和 V<sub>SSA</sub> 必须分别连到 V<sub>DD</sub> 和 V<sub>SS</sub>。

## 5.1.1 独立的 A/D 转换器供电和参考电压

为了提高转换的精确度,ADC 使用一个独立的电源供电,以过滤和屏蔽来自印刷电路板上的毛刺干扰。

- ADC 的电源引脚为 VDDA

- 独立的电源地 Vssa

如果有 V<sub>REF</sub>-引脚(依封装而定),它必须连接到 V<sub>SSA</sub>。

没有 V<sub>REF</sub>+和 V<sub>REF</sub>-引脚,它们在芯片内部与 ADC 的电源(V<sub>DDA</sub>)和地(V<sub>SSA</sub>)相连。

#### 5.1.2 电压调节器

复位后, 电压调节器总是使能的。根据应用方式, 调节器以3种不同的模式工作。

- 运行(Run)模式:调节器以正常功耗模式提供1.2 V 电源(内核、内存和外设)。

- 停机(Stop)模式:调节器以低功耗模式提供 1.2 V 电源,以保存寄存器和 SRAM 的内容。

- 待机(Standby)模式:调节器停止供电。

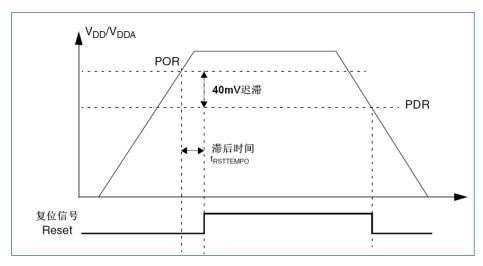

## 5.2 上电/掉电复位 (POR/PDR)

该系列芯片内部有一个完整的上电复位(POR)和掉电复位(PDR)电路。当供电电压达到 POR/PDR 阈值时,系统即能正常工作。

当 V<sub>DD</sub>/V<sub>DDA</sub> 低于指定的限位电压 V<sub>POR</sub>/V<sub>PDR</sub> 时,系统保持为复位状态,而无需外部复位电路。关于上电复位和掉电复位的更多细节,请参考数据手册的电气特性部分。

图 5-2 上电复位和掉电复位的波形图

### 5.3 低功耗模式

在系统或电源复位以后,MCU 处于运行状态。当 CPU 不需继续运行时(例如等待某个外部事件时),可以利用多种低功耗模式来节省功耗。用户需要根据最低电源消耗、最短启动时间和可用的唤醒源等条件,选定一个最佳的低功耗模式。

该系列芯片支持以下低功耗模式:

睡眠(Sleep)模式

Cortex®-M0 内核停止,所有外设包括 Cortex-M0 核心的外设,如 NVIC、系统时钟(SysTick)等仍在运行。

• 深度睡眠(Deep-Sleep)模式

在深度睡眠模式下,系统时钟降低至 114 kHz 以节省功耗。此模式下,仅 CPU 停止工作,所有外设处于工作状态并可通过中断/事件唤醒 CPU。深度睡眠模式的功耗高于停机模式。

停机(Stop)模式

在停机模式下,内核所有内部时钟被关闭,HSI 和 RC 振荡器被关闭。可以通过任一配置成 EXTI 的信号把 MCU 从停机模式中唤醒。

• 待机 (Standby) 模式

在待机模式下,系统可达到最低的电能消耗。此模式下,由于内部 LDO 关闭,因此内部 1.2 V供电域掉电; HSI 振荡器也关闭; SRAM 和寄存器的内容消失,但备份寄存器的内容仍然保留, 待机电路仍工作。

从待机模式退出的条件是: NRST 上的外部复位信号、IWDG 复位、WKUP 管脚上的一个上升边沿或 STBAWU 定时器溢出。

在运行模式下,可以通过以下任意方式降低功耗:

- 降低系统时钟频率。

- 关闭 APB 和 AHB 总线上未被使用的外设时钟。

表 5-1 低功耗模式的进入/唤醒条件

| 工作模式                  | 进入条件                                                                                                        | 唤醒条件                                                                                                                                                                                       | 内核电源时<br>钟状态                         | V <sub>DD</sub> 主区域<br>时钟状态 | 电压调节<br>器状态                |

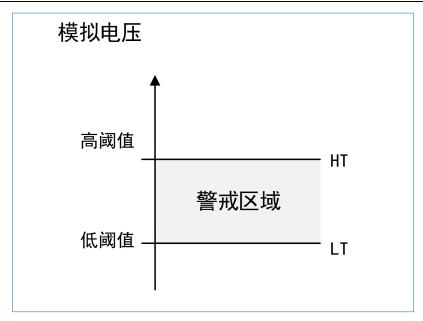

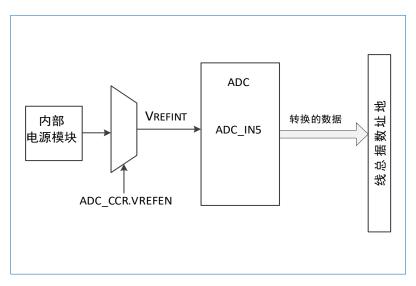

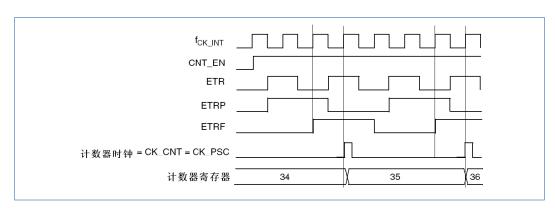

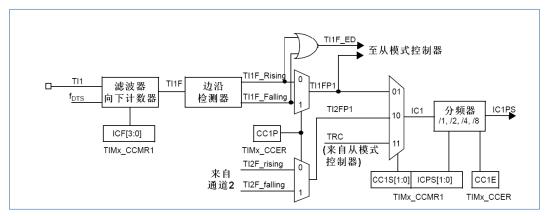

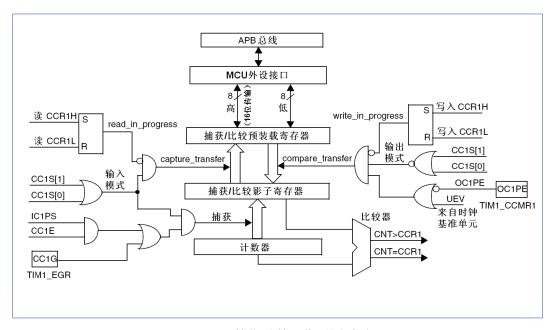

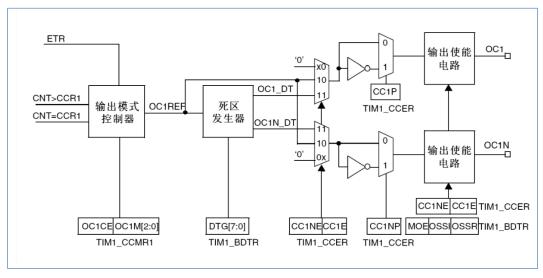

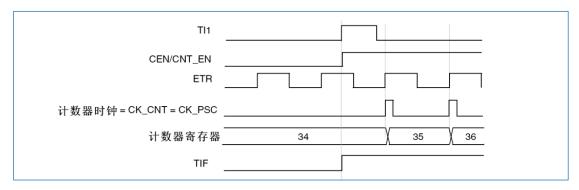

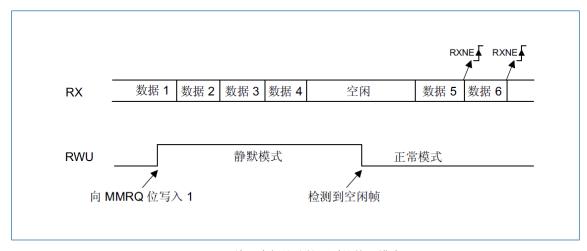

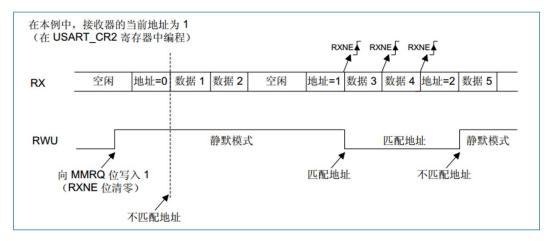

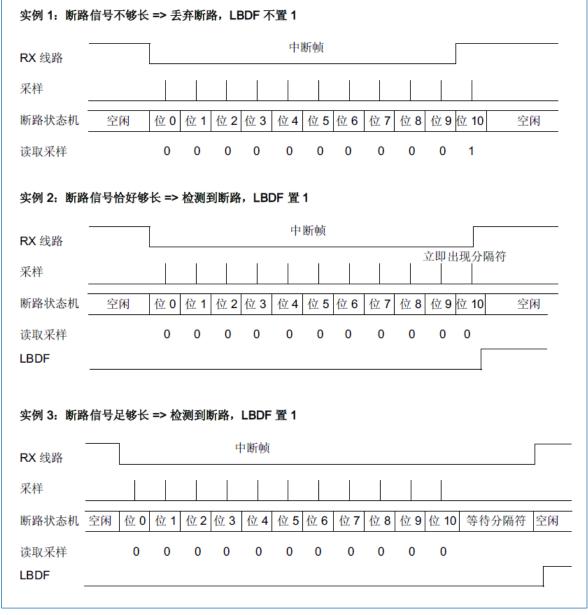

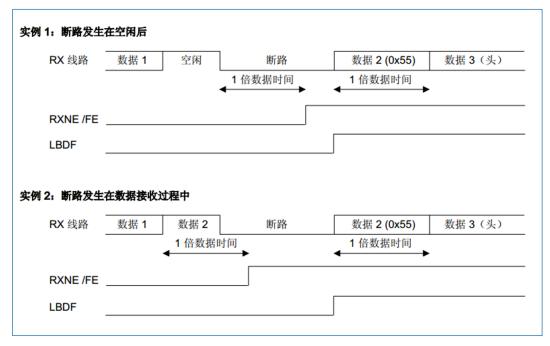

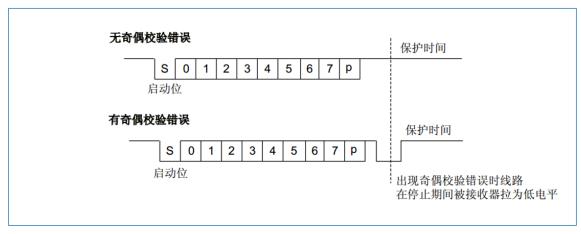

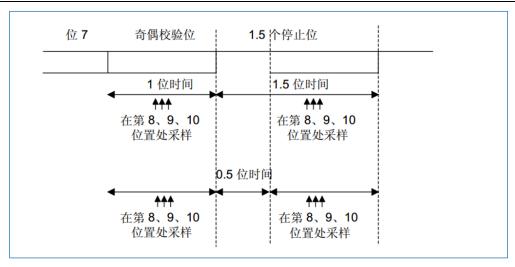

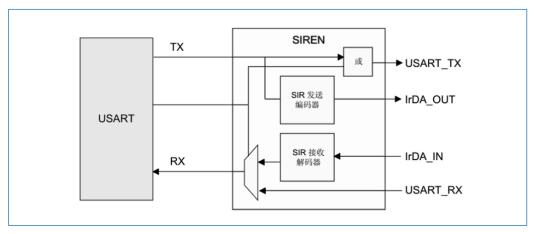

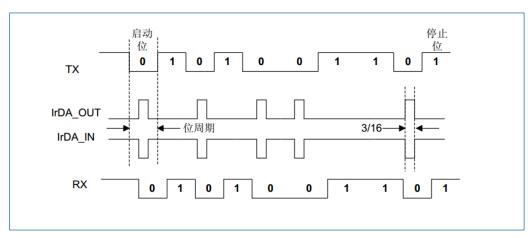

|-----------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------|----------------------------|